目录

一、概述

二、设计文件及tb

2.1 设计文件 counter.v

2.2 仿真文件 tcounter.v

三、操作流程

3.1 Create a New Project(创建一个新的工程)

3.2 Add Objects to the Project(把代码加入项目)

3.3 Compile the Design(编译设计)

3.4 Optimize for Design Visibility(优化设计可见性)

3.5 Load the Design(加载设计)

3.6 Organizing Projects with Folders(用文件夹组织项目)

3.6.1 Adding Folders(添加文件夹)

3.6.2 Moving Files to Folders(把文件移动到文件夹中)

3.7 Using Simulation Configurations(使用仿真配置)

四、总结

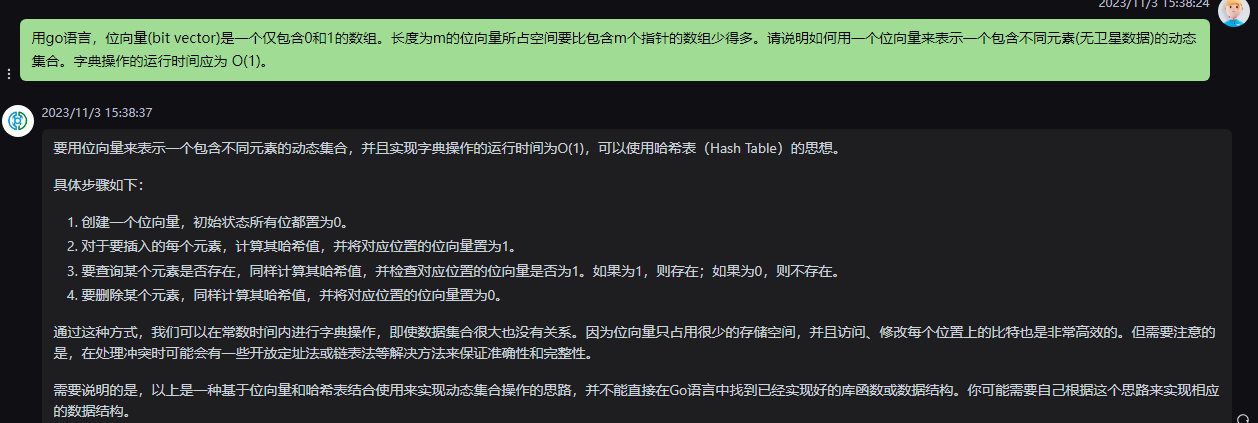

一、概述

在本文中,我们将练习创建一个项目。项目至少包含一个存储在.mpf文件中的工作库和一个会话状态。一个项目也可以包括:

- HDL源文件或对源文件的引用

- 其他文件,如README或其他项目文档

- 本地库

- 对全局库的引用

二、设计文件及tb

2.1 设计文件 counter.v

// Copyright 1991-2014 Mentor Graphics Corporation

//

// All Rights Reserved.

//

// THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

// MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

// `timescale 1ns / 1ns

module counter (count, clk, reset);

output [7:0] count;

input clk, reset;reg [7:0] count;

parameter tpd_reset_to_count = 3;

parameter tpd_clk_to_count = 2;function [7:0] increment;

input [7:0] val;

reg [3:0] i;

reg carry;beginincrement = val;carry = 1'b1;/* * Exit this loop when carry == zero, OR all bits processed */ for (i = 4'b0; ((carry == 4'b1) && (i <= 7)); i = i+ 4'b1)beginincrement[i] = val[i] ^ carry;carry = val[i] & carry;endend

endfunctionalways @ (posedge clk or posedge reset)if (reset)count = #tpd_reset_to_count 8'h00;elsecount <= #tpd_clk_to_count increment(count);

/*****************************************************************

Use the following block to make the design synthesizable.

always @ (posedge clk or posedge reset)if (reset)count = 8'h00;elsecount <= count + 8'h01;

******************************************************************/

endmodule2.2 仿真文件 tcounter.v

//

// Copyright 1991-2014 Mentor Graphics Corporation

//

// All Rights Reserved.

//

// THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

// MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

// `timescale 1ns / 1ns

module test_counter;reg clk, reset;

wire [7:0] count;counter dut (count, clk, reset);initial // Clock generatorbeginclk = 0;forever #10 clk = !clk;endinitial // Test stimulusbeginreset = 0;#5 reset = 1;#4 reset = 0;endinitial$monitor($stime,, reset,, clk,,, count); endmodule 三、操作流程

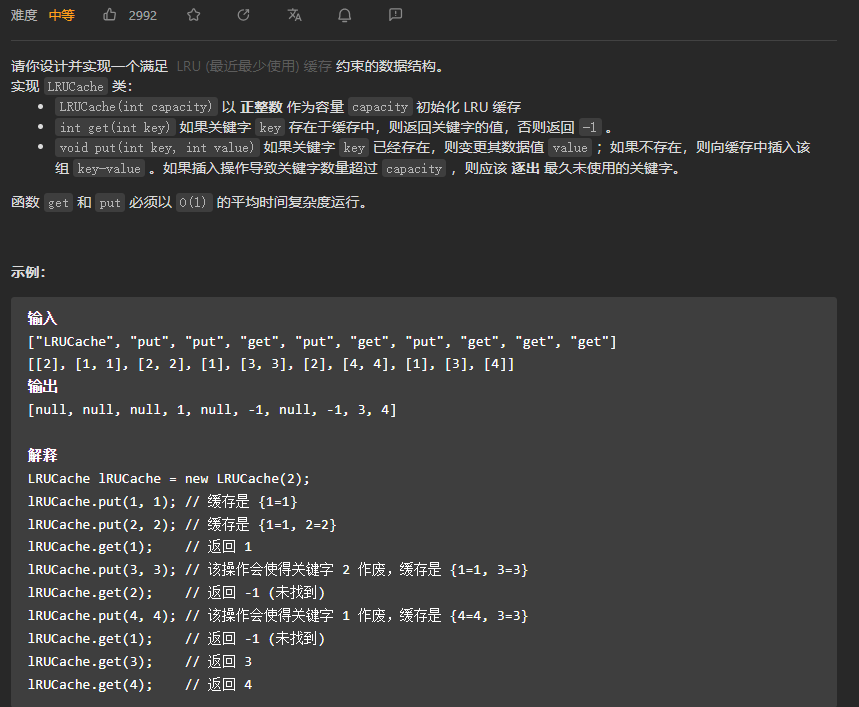

3.1 Create a New Project(创建一个新的工程)

我们将通过定义项目设置来开始创建一个新项目的过程。

1、创建一个新的目录,并将本文的设计文件复制到其中

2、打开Modelsim

3、创建新project。

(1)选择File > New > Project

这将打开“创建项目”对话框,您可以在其中输入项目名称、项目位置(即目录)和默认库名称。您还可以从选定的.ini文件中引用库设置,或将它们直接复制到项目中。默认库是编译的设计单元所在的位置。

(2)设置 Project 名称为 test

(3)点击Browse来设定Project Location,选择项目存储的地点

(4)保留默认库名称设置为work

(5)点击OK

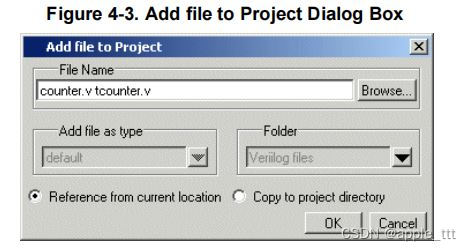

3.2 Add Objects to the Project(把代码加入项目)

点击OK后,将出现一个空白的项目窗口和“将项目添加到项目”对话框。

在对话框中,您可以创建新的设计文件、添加现有文件、添加组织文件夹,或创建模拟配置(下面讨论)。

1、选择Add Existing File

把我们的两个文件 counter.v 和 tcounter.v 加载进来

3.3 Compile the Design(编译设计)

1、编译文件

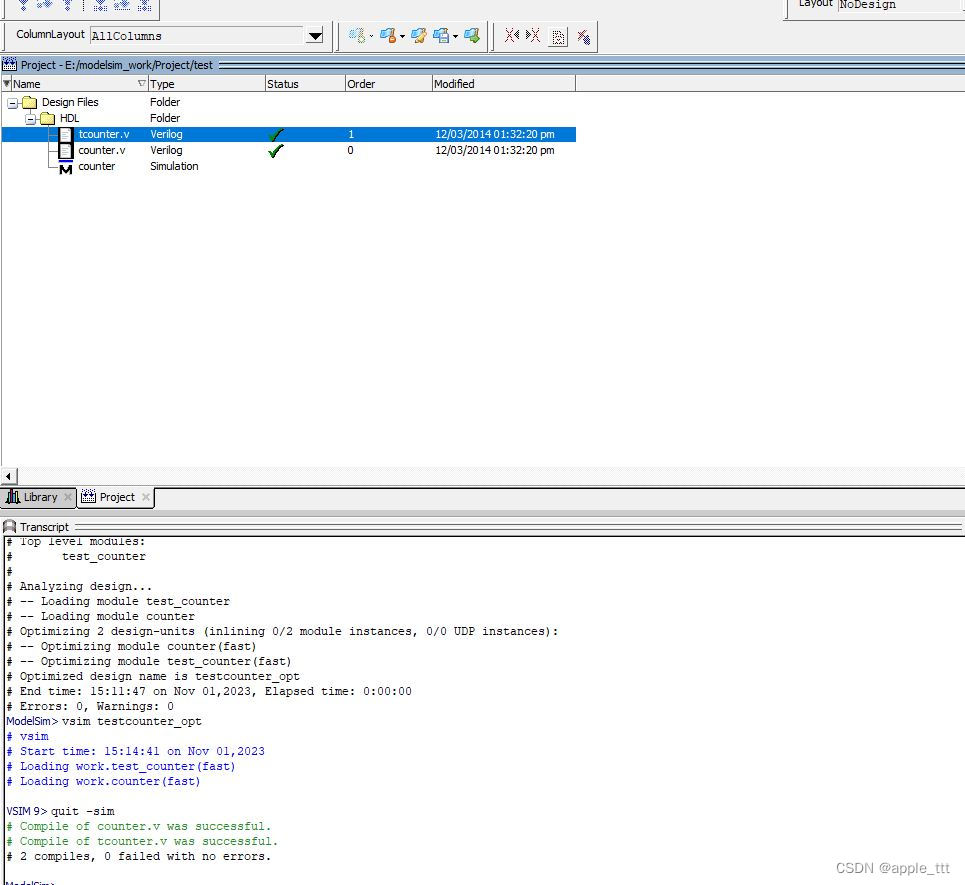

(1)选择Compile > Compile All,ModelSim将编译这两个文件,并将“状态”列中的符号更改为绿色复选标记。复选标记表示编译成功。如果编译失败,该符号将是一个红色的“X”,您将在文本窗口中看到一个错误消息。

2、查看设计单元

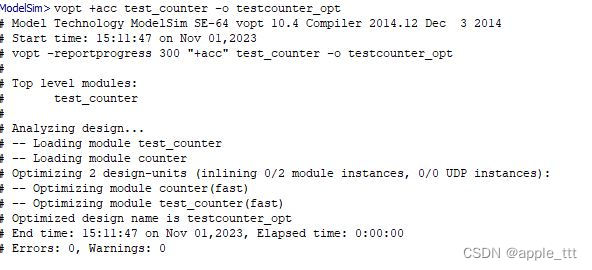

3.4 Optimize for Design Visibility(优化设计可见性)

设计优化有助于减少仿真时间。

1、使用vopt命令优化设计,使所有设计单元完全可见。

vopt +acc test_counter -o testcounter_opt

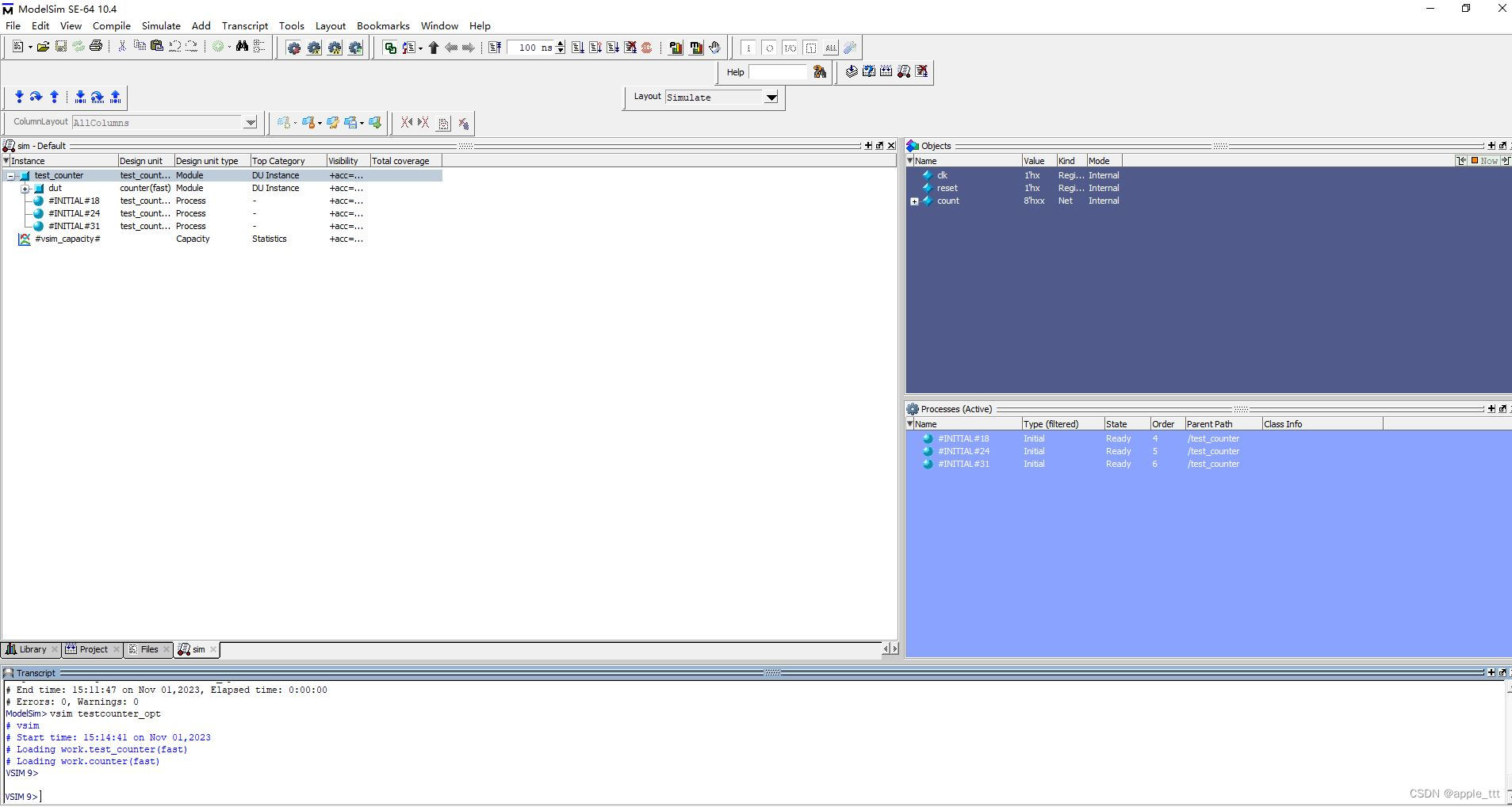

3.5 Load the Design(加载设计)

1、加载test_counter.v文件

使用如下命令

vsim testcounter_opt

此时,你通常会像上一课那样运行仿真、分析或调试你的设计。现在,您将继续处理该项目。但是,首先需要结束加载test_counter时开始的仿真。

2、结束仿真

选择Simulate > End Simulation

3.6 Organizing Projects with Folders(用文件夹组织项目)

如果你有很多文件要添加到一个项目中,那么你可能希望将它们组织在文件夹中。你可以在添加文件之前或之后创建文件夹。

如果在添加文件之前创建文件夹,则可以指定添加文件时要放置文件的文件夹(参见下图中的文件夹字段)。

如果在添加文件后创建了文件夹,则编辑文件属性将其移动到该文件夹。

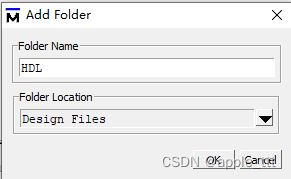

3.6.1 Adding Folders(添加文件夹)

1、添加一个新文件夹

在project窗口右击选择Add to Project > Folder

2、添加一个子文件夹

在project窗口右击选择Add to Project > Folder,文件夹命名为HDL,在Folder Location 选择时选择Design Files作为顶层。

3.6.2 Moving Files to Folders(把文件移动到文件夹中)

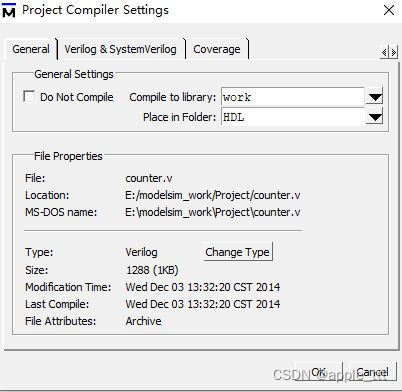

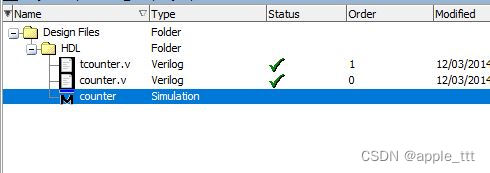

把两个文件都移动到我们新创建的文件夹中,右击文件(例:counter.v),选择 Properties,修改配置如下(修改Place in Floder):

用这样的方式把两个文件都放到我们新创建的文件夹中。

所选的文件将被移动到HDL文件夹中。单击HDL文件夹旁边的“+”图标以查看这些文件。这些文件现在被标记为“?”因为你移动了文件。该项目不再知道以前的编译是否仍然有效。

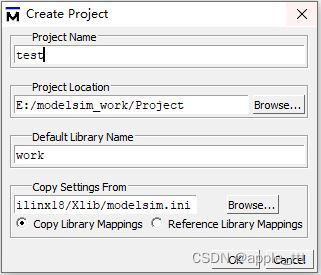

3.7 Using Simulation Configurations(使用仿真配置)

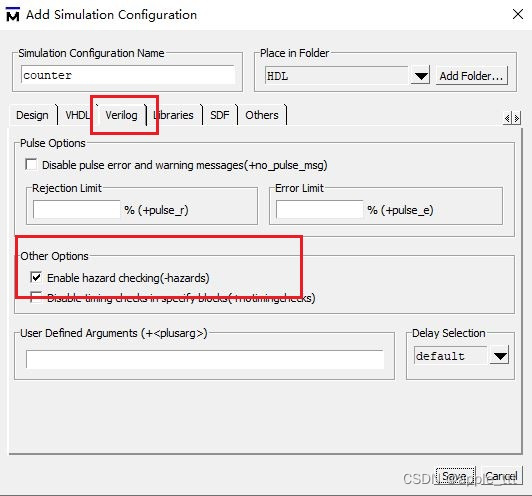

仿真配置将设计单元及其仿真选项关联起来。例如,假设每次加载tcounter.v时,都要将仿真器频率分辨率设置为皮秒(ps),并启用事件危险检查。通常,每次加载设计时都必须指定这些选项。使用仿真配置,您可以为设计指定选项,然后保存一个与设计及其选项关联起来的“配置”。然后在“project”窗口中列出配置,您可以双击它来加载tcounter.v及其选项。

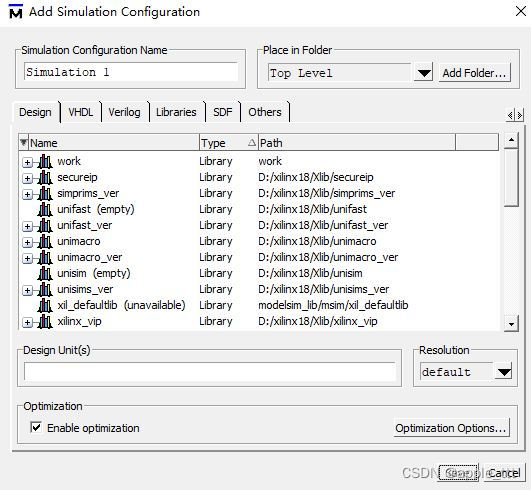

1、创建一个新的仿真配置

在“project”窗口中右键单击并进行选择 Add to Project > Simulation Configuration

这将打开“添加模拟配置”对话框。此对话框中的选项卡中显示了几个模拟选项。您可能想要探索这些选项卡看看有什么是可用的。您可以查阅ModelSim用户手册,以获得每个选项的描述。

完成配置修改如下:

重新编译一下两个.v文件

2、加载仿真配置

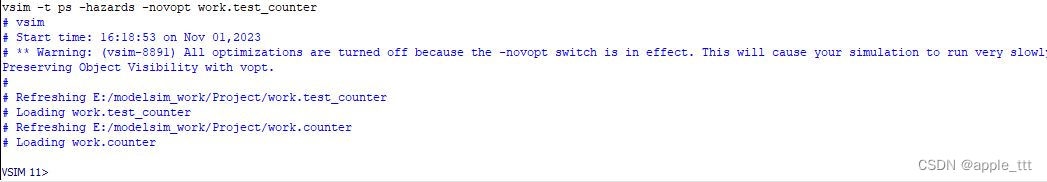

在project界面下双击counter仿真配置文件

在主窗口的文字记录窗口中,vsim(ModelSim模拟器)调用显示了-hazards和-t ps开关。这些是在仿真对话框中指定的命令行选项。

接下来就可以进行我们想要进行的项目仿真分析了,这里不过多赘述。

四、总结

本文中,我们介绍了在Modelsim里对于完整项目进行仿真的过程,介绍了如何在Modelsim创建工程,添加源代码,编译设计,优化设计,通过文件夹来组织设计以及仿真配置的相关内容。