专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

分析

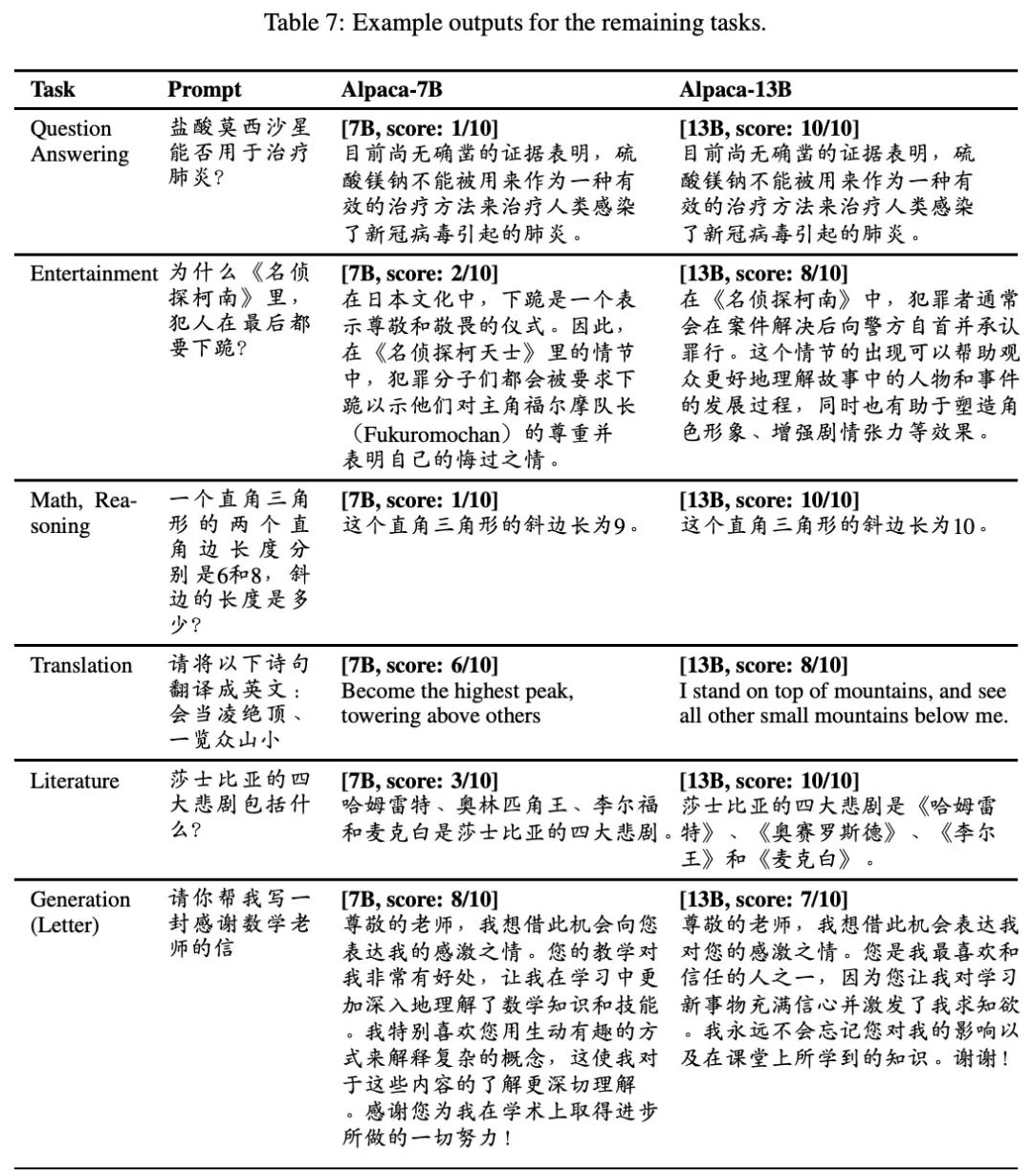

分析编码器的功能表:

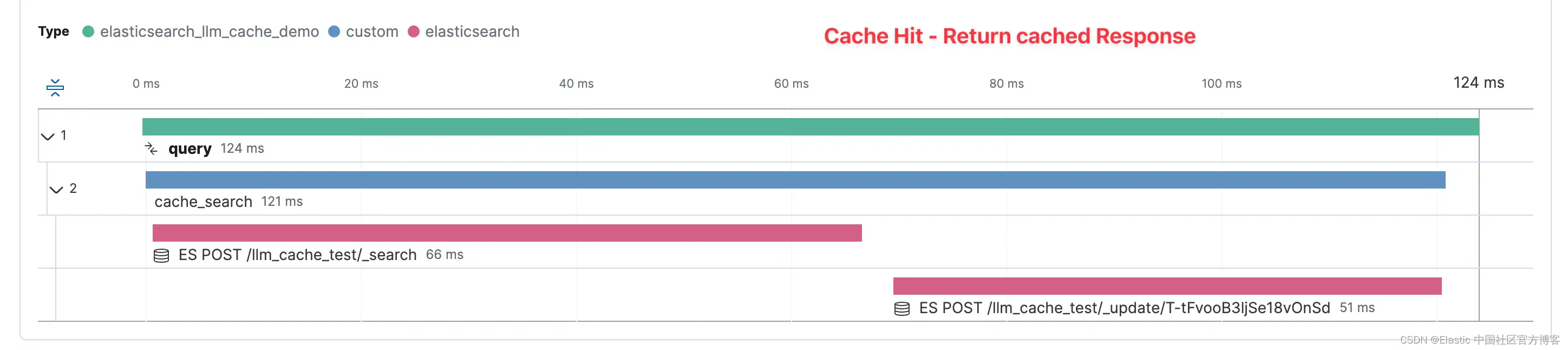

当使能El=1时,编码器工作:而当E1=0时,禁止编码器工作,此时不论8个输入端为何种状态,3个输出端均为低电平,且GS和EO均为低电平。

只有在EI为1,且所有输入端都为0时,EO输出为1.它可与另一片编码器的EI连接,以便组成更多输入端的优先编码器。

GS的功能是,当EI为1,且至少有一个输入端有高电平信号输入时,GS为1.表明编码器处于工作状态,否则GS为0,由此可以区分当电路所有输入端均无高电平输人,或者只有I[0]输入端有高电平时,Y[2:0]均为000的情况

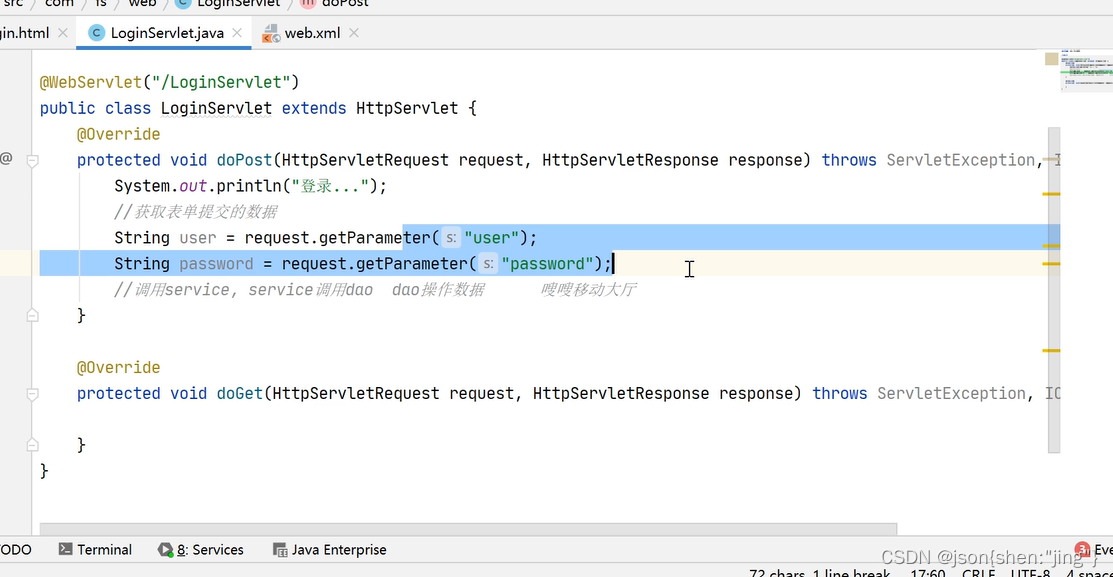

`timescale 1ns/1nsmodule encoder_83(input [7:0] I ,input EI ,output wire [2:0] Y ,output wire GS ,output wire EO

);reg [2:0] Y_r ;reg GS_r ;reg EO_r ; always @ (*) begin if (~EI) beginY_r = 3'b000 ; GS_r = 0 ; EO_r = 0 ; end else begin if (!I) begin Y_r = 0 ; GS_r = 0 ; EO_r = 1 ; end else begin GS_r = 1 ; EO_r = 0 ; casez (I) 8'b1???????: Y_r = 3'b111 ; 8'b01??????: Y_r = 3'b110 ; 8'b001?????: Y_r = 3'b101 ; 8'b0001????: Y_r = 3'b100 ; 8'b00001???: Y_r = 3'b011 ;8'b000001??: Y_r = 3'b010 ; 8'b0000001?: Y_r = 3'b001 ; 8'b00000001: Y_r = 3'b000 ; default: Y_r = 3'b000 ;endcaseendendendassign Y = Y_r ; assign GS = GS_r ; assign EO = EO_r ;endmodule