文章目录

- Filter Designer的打开

- 滤波器参数设置

- 生成matlab代码

- 生成XILINX Coefficient(.COE) File

- 实际浮点数的导出

- 官方使用教程

Filter Designer的打开

打开Filter Designer:

方法一:命令行中输入Filter Designer,再回车打开。

方法二:APP中调用Filter Designer打开。

滤波器参数设置

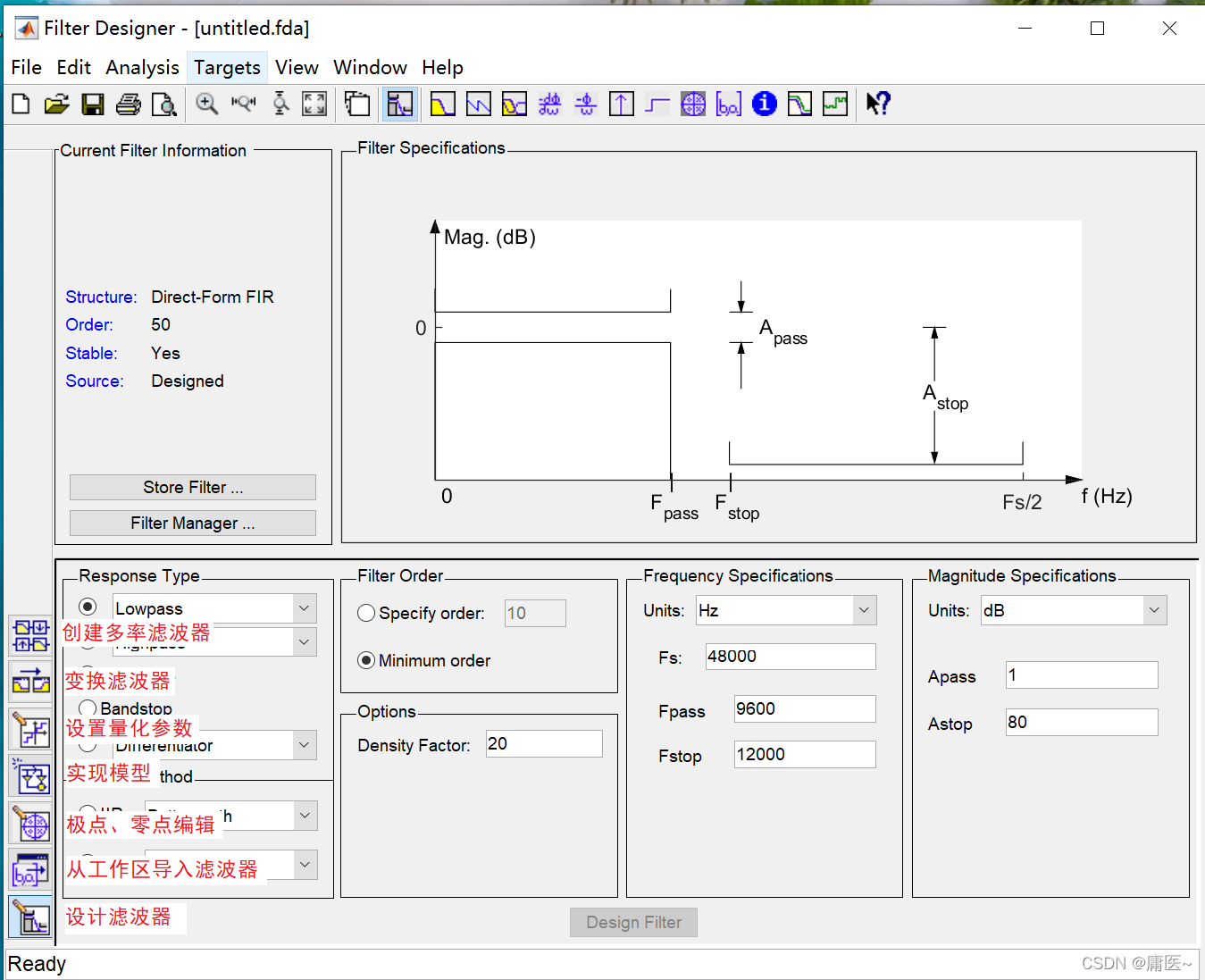

界面的多种滤波器设置选项:

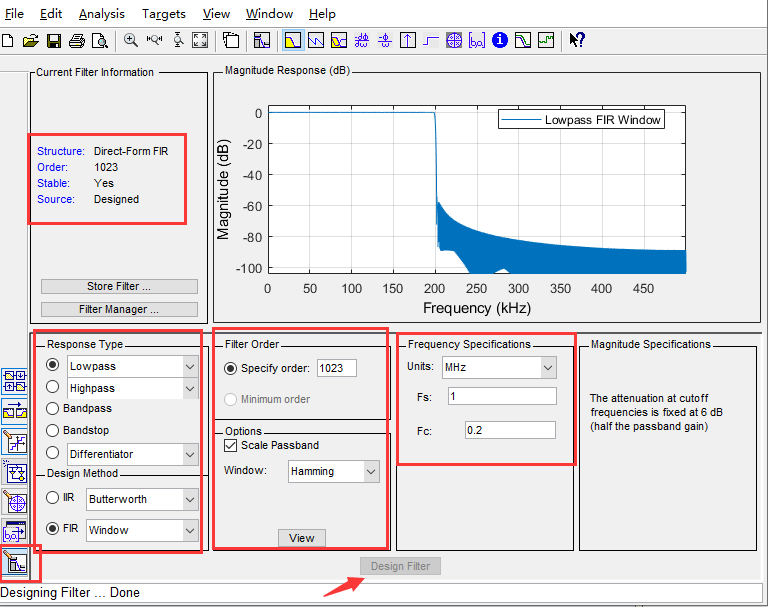

根据设计需求设置滤波器参数:

具体界面介绍参看此文章:MATLAB滤波器设计fdatool(filterDesigner)工具箱使用

生成matlab代码

如需要生成MATLAB,配置后可以生成matlab函数在matlab中进行滤波处理。

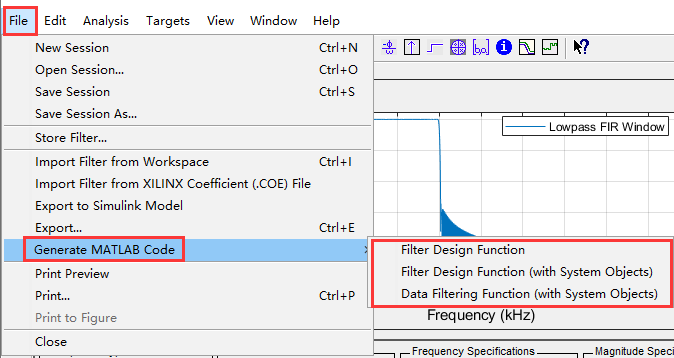

具体方式为:可以使用File>Generate MATLAB Code生成 MATLAB 代码:有三种生成方式。

-

利用Filter Design Function (with System Objects)生成的matlab程序

这种方式仅生成了系数,系数文件用保存的名字来表示,进行滤波时采用filter函数进行滤波。

-

利用Data Filtering Function (with System Objects)生成的matlab程序

这种方式生成了一个函数,进行滤波时直接调用该函数进行滤波。

多种滤波器的配置界面说明以及生成代码的区别参看:https://blog.csdn.net/QUACK_G/article/details/124433102

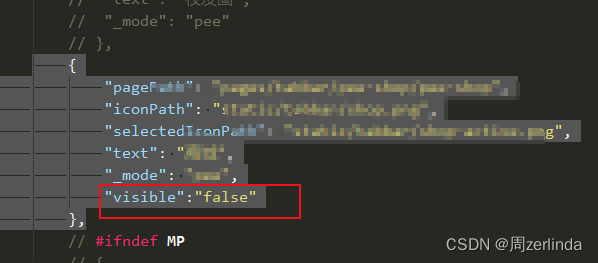

生成XILINX Coefficient(.COE) File

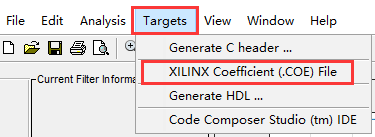

在Targets -> XILINX Coefficient(.coe)File进行导出。.coe文件的格式如下:

Radix = RADIX;

Coefficient_Width = COEFFICIENT_WIDTH;

CoefData = VECTOR;

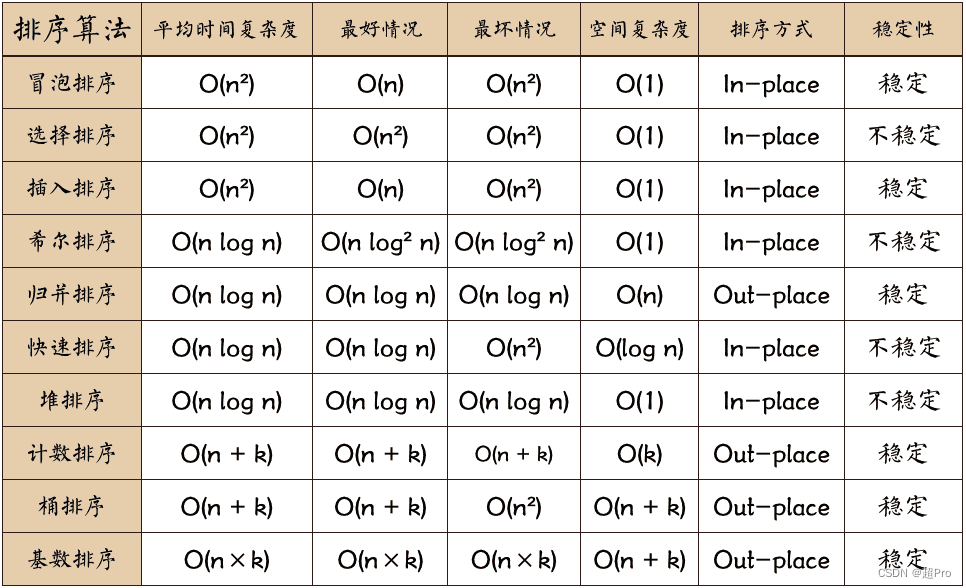

RADIX为数据进制类型,包括十进制、二进制、十六进制。

COEFFICIENT_WIDTH为数据对应的二进制位宽。

VECTOR为数据,数据以",“为间隔进行分开,最后以”; "结尾。

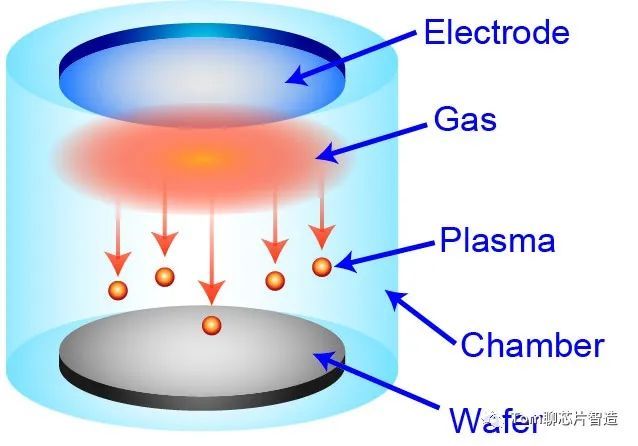

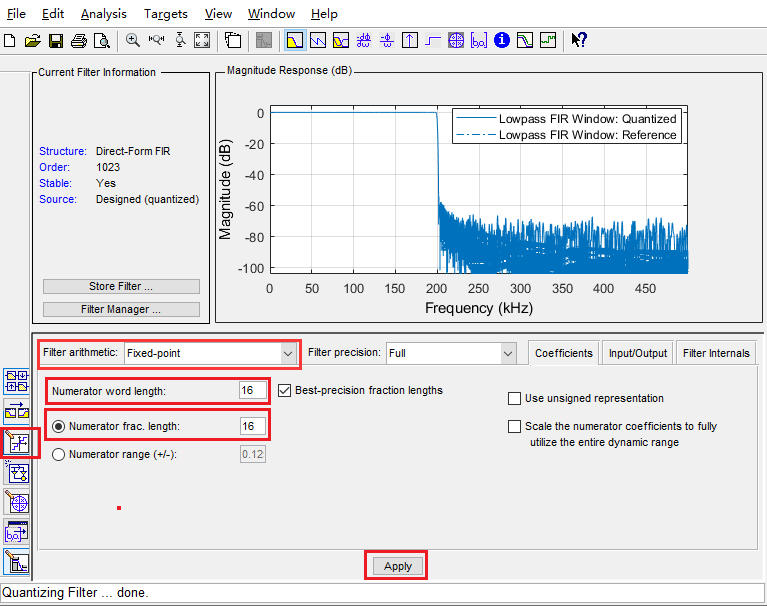

导出时提示错误:Your flter must be a fixed-point single-section, direct-form FIR flter to generate a XILINX cofficient (.COE) file.

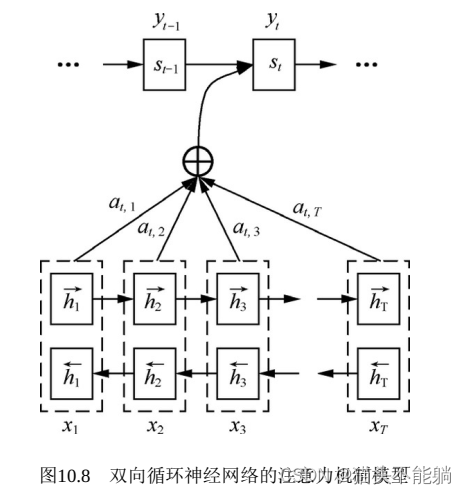

解决办法:设置Filter arithmetic为Fixed-point(定点,由于有些FPGA中是不能直接对浮点数进行操作的,只能采用定点数进行数值运算,所以在导出前要将滤波器的系数配置为定点数,利用设置量化参数(Set Quantization Parameters )将系数改为定点数即可。

关于FPGA定点数的介绍参考文章:FPGA浮点小数与定点小数的换算及应用

按照上图的系数是以定点十六进制表示的,每个数据长度为16位(由Numerator word length决定),其为实际浮点数据左移16位(由Numerator frac. length决定,需要注意的是在未勾选Best-precision fraction lengths时输出的coe文件仍然按照Numerator frac. length进行量化的,所以建议不勾选Best-precision fraction lengths,进而设置Numerator frac. length)得到,例如实际浮点数据第一个系数为0.002,定点表示为0x0081((int)0.002* 2 ^ 16 = 131 = 0x0081,即0.001左移16位)。

实际浮点数的导出

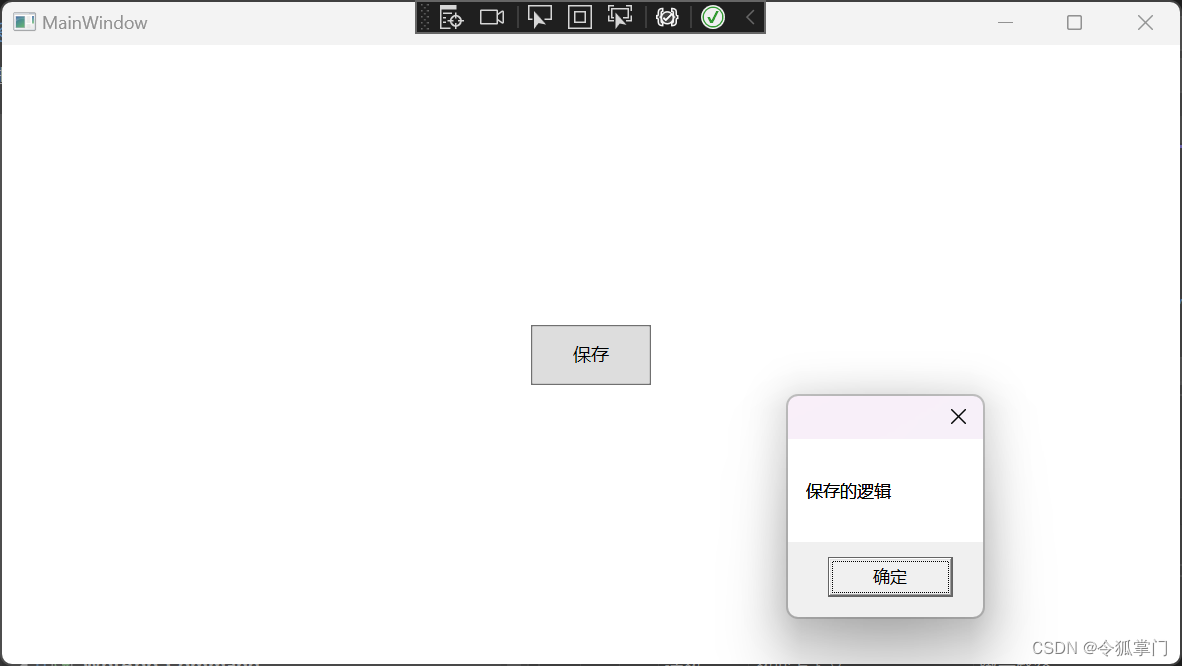

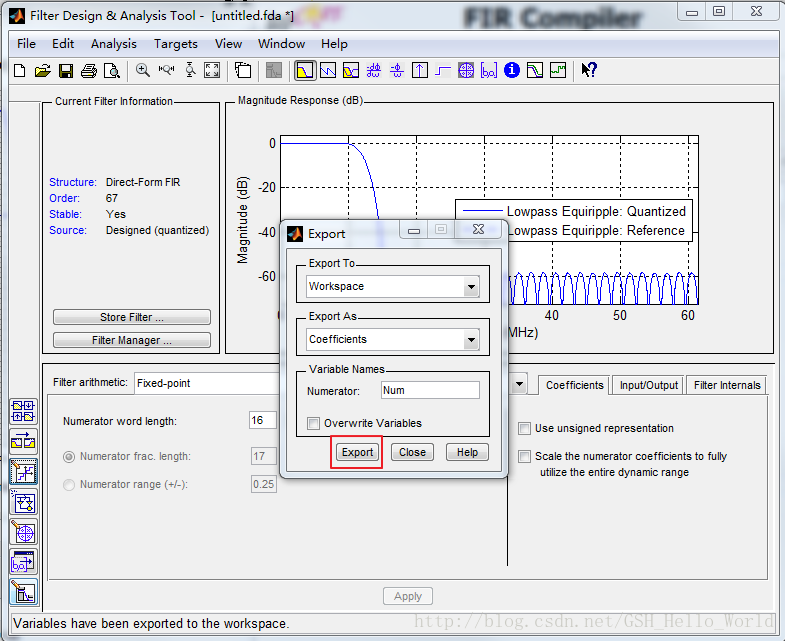

点击File —> Export导出滤波器系数到matlab的工作区workspace,快捷键Ctrl+E,这种方式导出的是实际浮点数据。

参考使用fdatool生成Xilinx中FIR滤波器IP核的系数

官方使用教程

Using Filter Designer - MATLAB & Simulink - MathWorks 中国