水 MicroBlaze 最后的介绍和使用

我对MicroBlaze 已经有了一个普遍的理解 了

现在我将看的两个 一个是 AXI4接口的 DDR读写实验 还有一个是 AXI DMA 环路实验

虽然是 水文 但是 也许能从中 得到一些收获

第一个是 AXI DDR 读写实验

Xilinx 从 Spartan-6 和 Virtex-6 系列开始使用 AXI 协议来连接 IP 核。在 7 系列器件中,Xilinx 在 IP 核中继续使用 AXI 协议。

AXI 协议就是

描述了主设备和从设备之间的数据传输方式,在该协议中,主设备和从设备之间通过握手信号建立连接。

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、总线的地址/控制和数据通道是分离的;

2、支持不对齐的数据传输;

3、支持突发传输,突发传输过程中只需要首地址;

4、具有分离的读/写数据通道;

5、支持显著传输访问和乱序访问;

6、更加容易进行时序收敛。

在数字电路中只能传输二进制数 0 和 1,因此可能需要一组信号才能高效地传输信息,这一组信号就组

成了接口。AXI4 协议支持以下三种类型的接口:

1、 AXI4:高性能存储映射接口。

2、 AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信。

3、 AXI4-Stream:用于高速数据流传输,非存储映射接口。

4、具有分离的读/写数据通道;

5、支持显著传输访问和乱序访问;

6、更加容易进行时序收敛。

在数字电路中只能传输二进制数 0 和 1,因此可能需要一组信号才能高效地传输信息,这一组信号就组

成了接口。AXI4 协议支持以下三种类型的接口:

1、 AXI4:高性能存储映射接口。

2、 AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信。

3、 AXI4-Stream:用于高速数据流传输,非存储映射接口。

在这里我们首先解释一下存储映射(Meamory Map)这一概念。如果一个协议是存储映射的,那么主

机所发出的会话(无论读或写)就会标明一个地址。这个地址对应于系统存储空间中的一个地址,表明是

针对该存储空间的读写操作。

AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite

为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而 AXI-Stream 接口则像 FIFO 一样,

数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速 AD、PCIe、DMA 接

口等需要高速数据传输的场合。

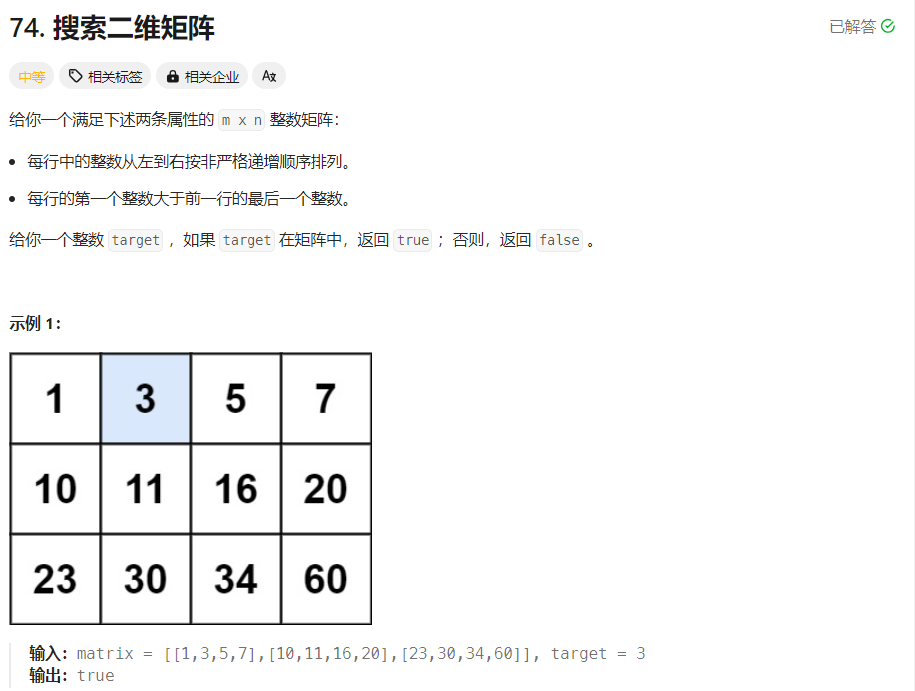

实验任务 :

是通过自定义一个 AXI4 接口的 IP 核,通过 AXI 接口对 DDR3 进行读写测试。

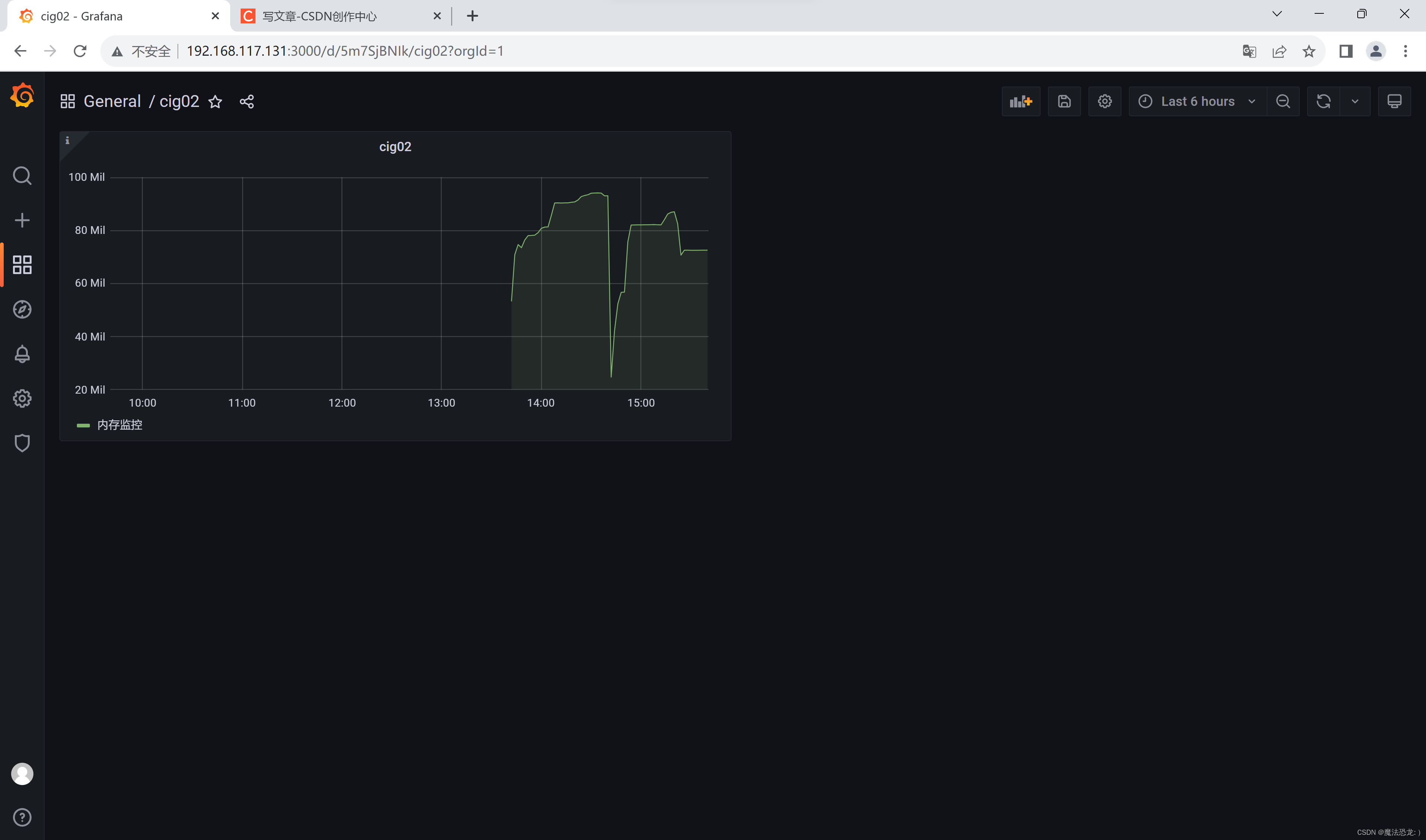

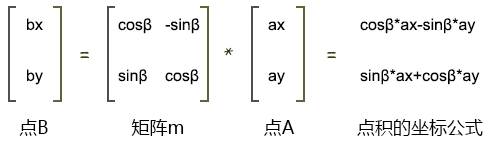

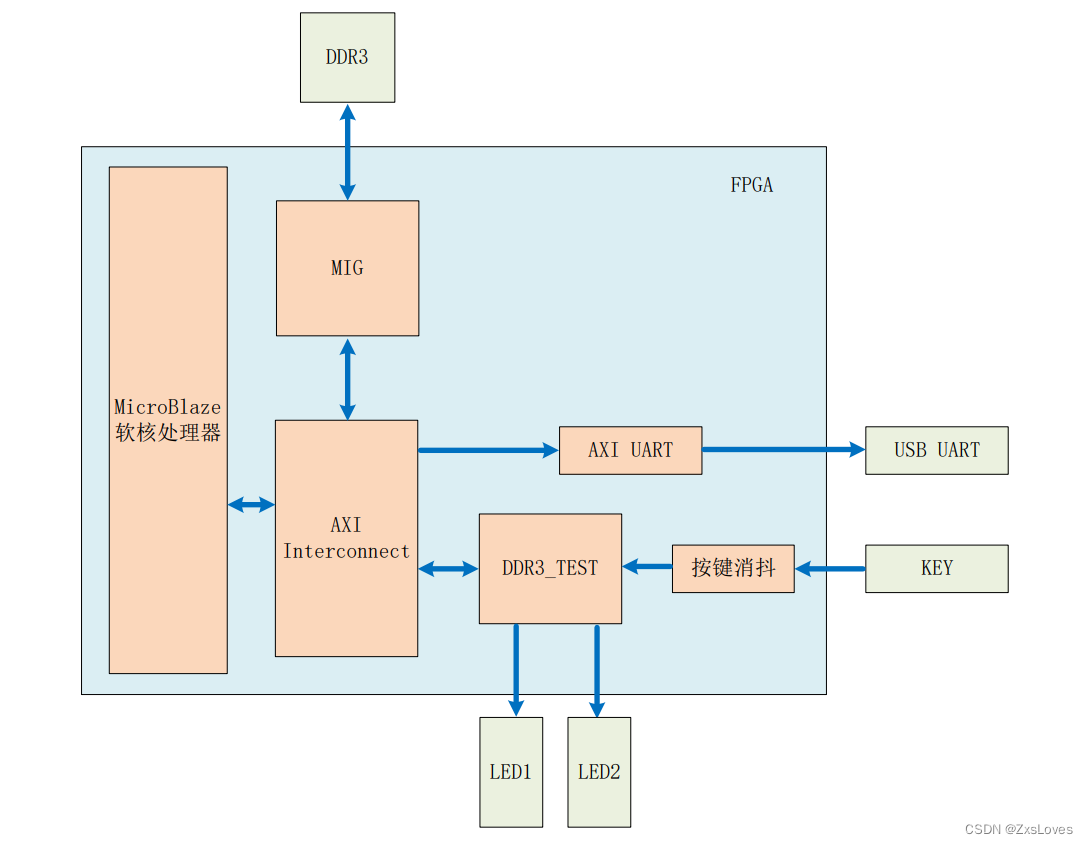

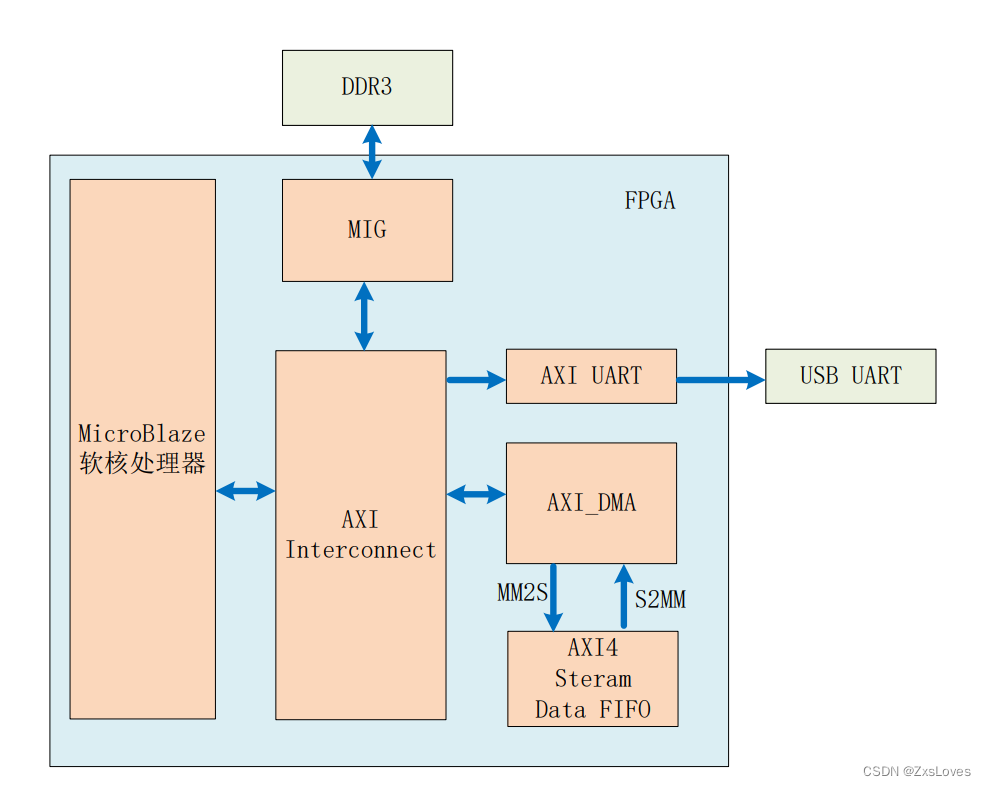

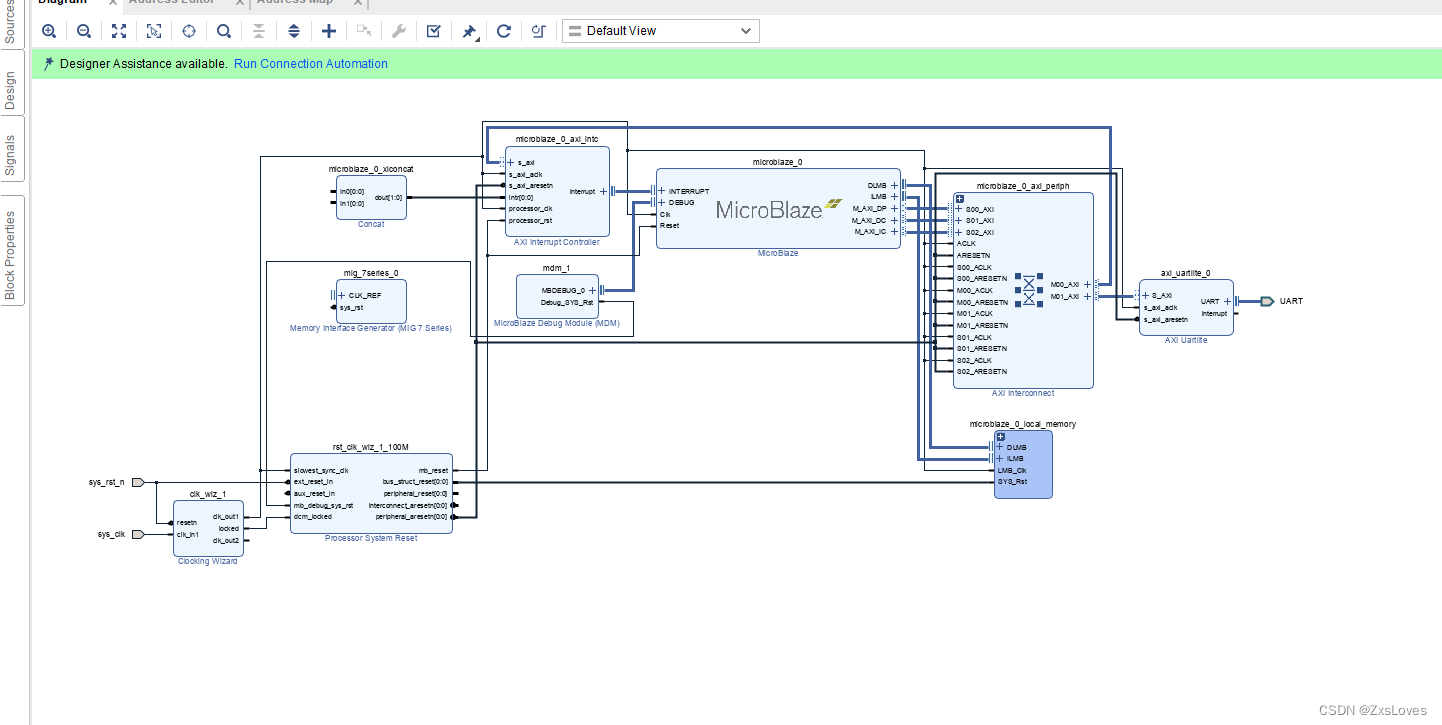

下面是 本次设计的系统框图

在上图中,DDR3_TEST 是我们自定义的 IP 核,具有 AXI4 Master 端口,该端口通过 AXI Interconnect模块,最终连接 MIG IP 核。AXI UART IP 核打印从 DDR3 中读出的数据。DDR3_TEST IP 核在检测到按键按下后会启动读写过程,并将读出的数据与写入的数据作比较,比较完成后点亮 LED1。另外,如果在读写过程中出错,或者在比较的过程中发现读出的数据与写入的数据不一致,LED2 会点亮。

看上去这是 一个相对来说 比之前做过的都要大而复杂的设计

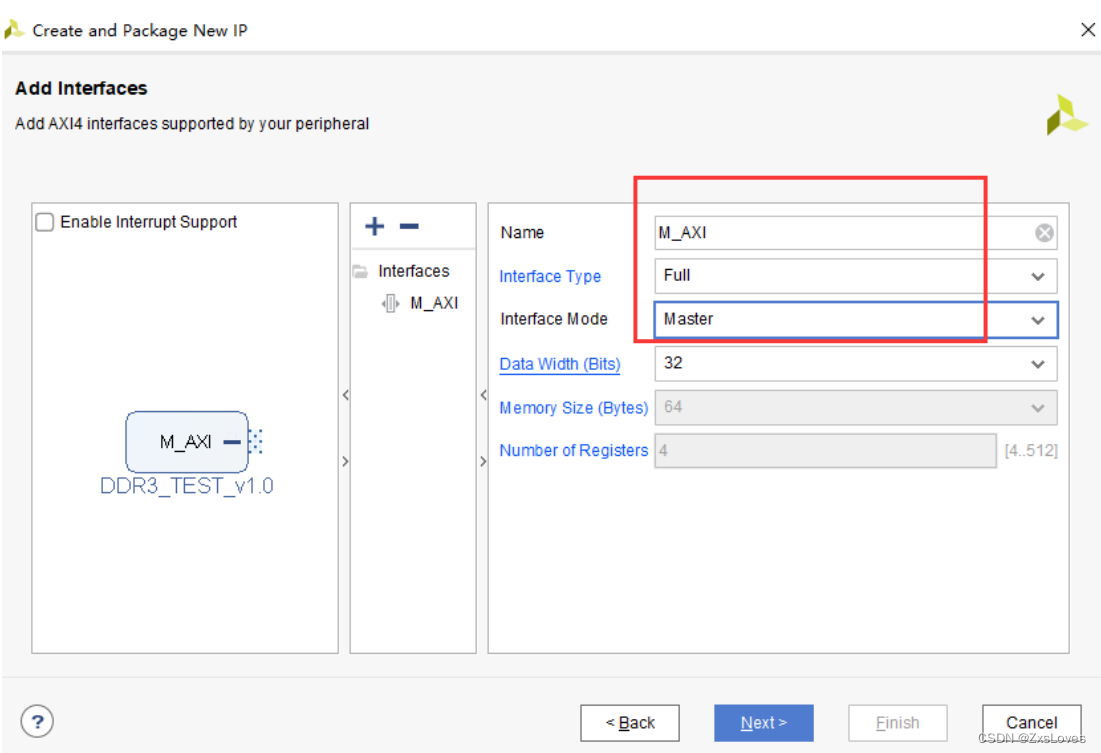

我们需要先自定义一个 带有 AXI4 接口的IP核

自定义IP 我们按照使用手册的要求 配置成了现在这样子

因为我们在创建的时候 选择了AXI接口 所以其实并不需要我们的其他操作 vivado IP工具就已经帮助我们实现了一个对 AXI 读写的

所以并不需要对这个代码有任何修改

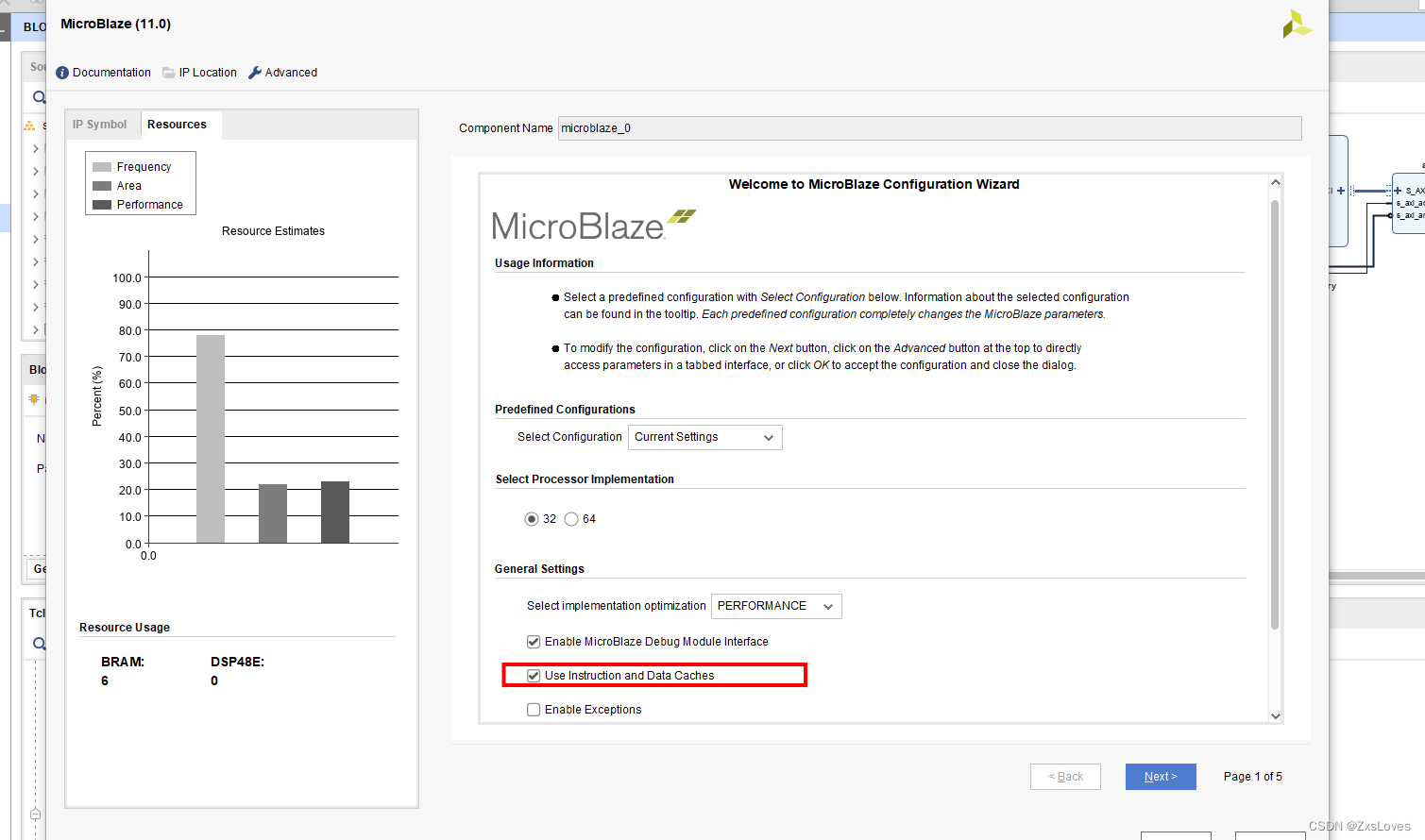

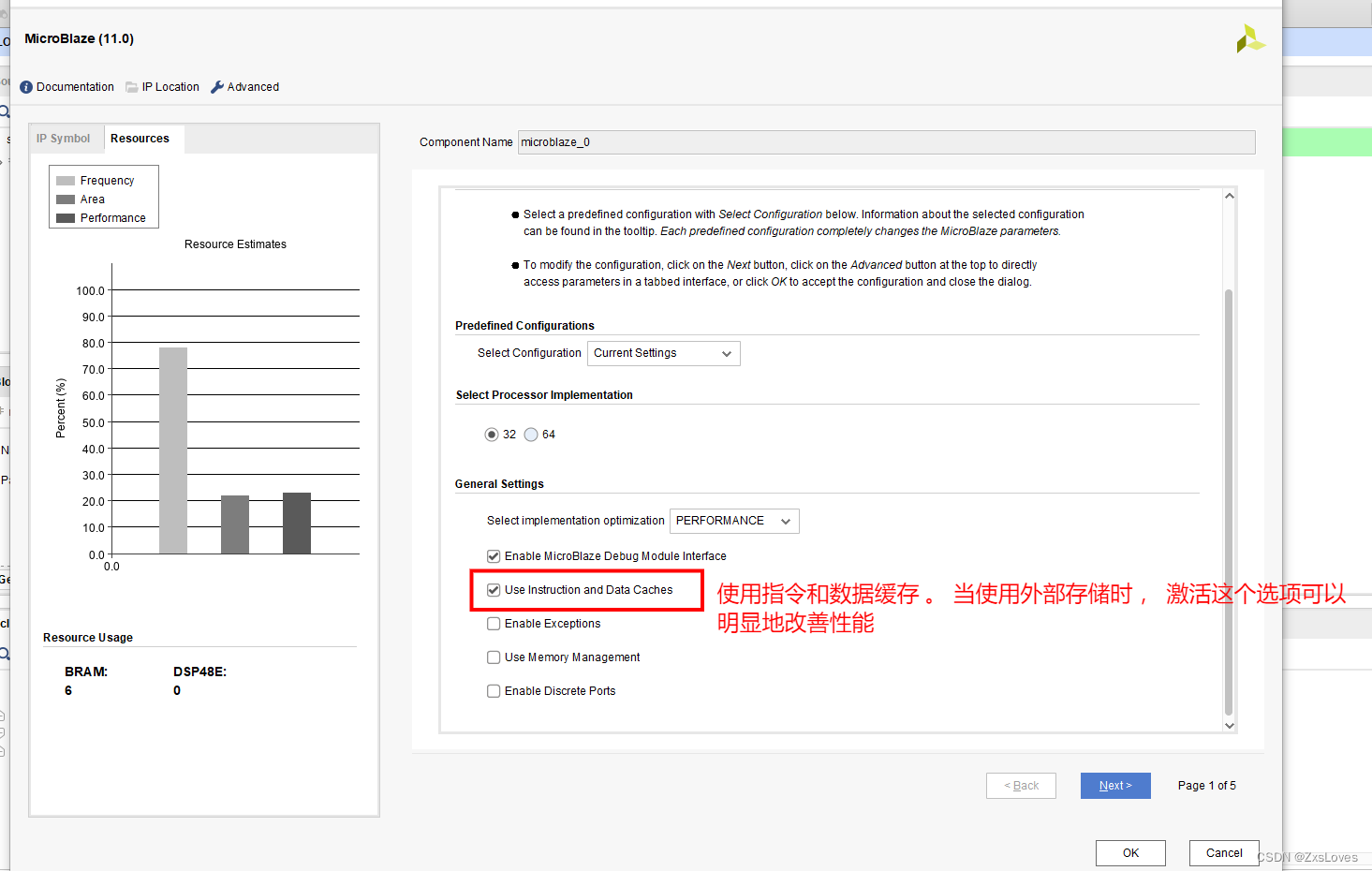

因为以前的 Micro Blaze 的搭建是没有 DDR的系统结构 本次设计 我们将学习带有 DDR的 MicroBlaze 的搭建

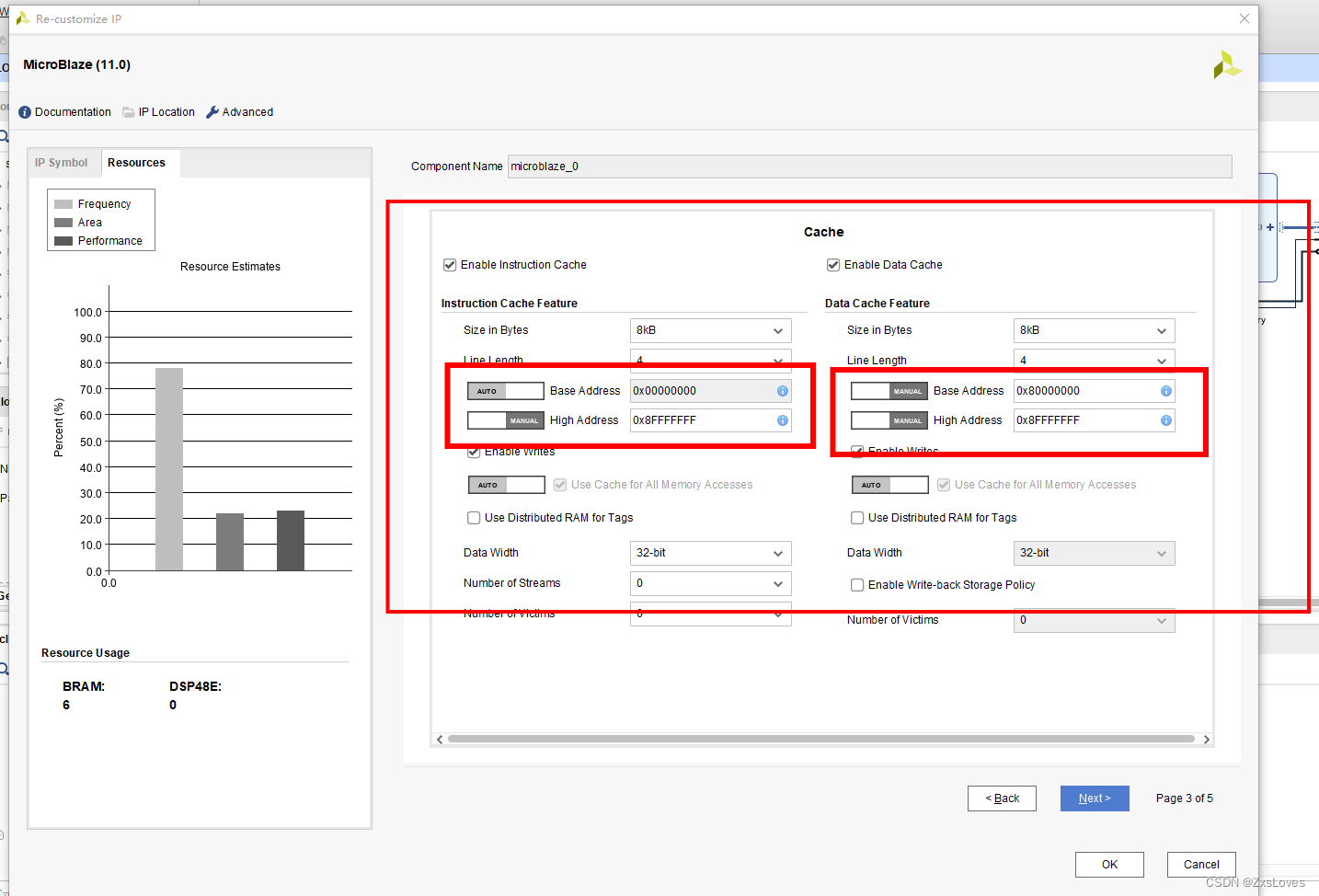

我们修改 Micro Blaze 的第三页 cache的 内容

这里的数据 必须与 IP INITRATOR->Adress Editor->microblaze_0->的 mig_7series_0

下面是 AXI DMA 环路实验

DMA 是所有现代计算机的重要特色,它允许不同速度的硬件设备进行沟通,而不需要依于中央处理器

的大量中断负载。否则,中央处理器需要从来源把每一片段的数据复制到寄存器,然后把它们再次写回到

新的地方。在这个时间里,中央处理器就无法执行其它的任务。

DMA 是用硬件实现存储器与存储器之间或存储器与 I/O 设备之间直接进行高速数据传输。使用

DMA 时,处理器向 DMA 控制器发出一个存储传输请求,这样,DMA 控制器在传输数据时,处理器可

以执行其它操作,传输操作完成后 DMA 以中断的方式通知处理器。

为了发起传输事务,DMA 控制器必须得到以下数据:

⚫ 源地址 — 数据被读出的地址

⚫ 目的地址 — 数据被写入的地址

⚫ 传输长度 — 应被传输的字节数

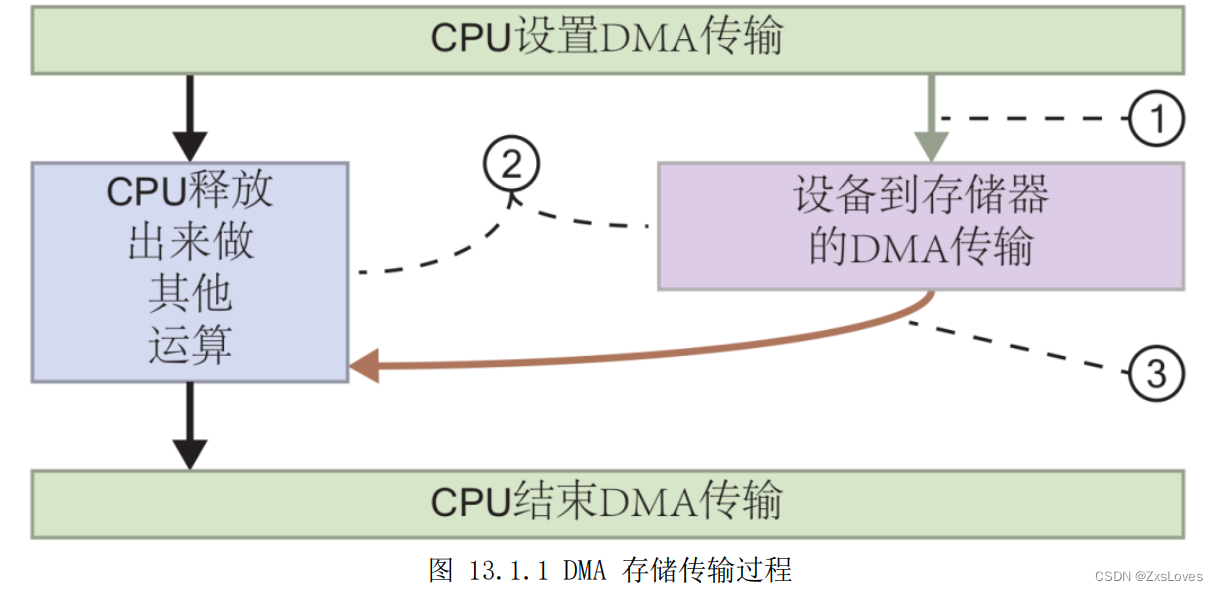

DMA 存储传输的过程如下:

- 为了配置用 DMA 传输数据到存储器,处理器发出一条 DMA 命令。

- DMA 控制器把数据从外设传输到存储器或从存储器到存储器,而不占用 CPU 来传输数据。

- 数据传输完成后,向 CPU 发出一个中断来通知它 DMA 传输可以关闭了。

实验任务是

是使用 AXI DMA IP 核从 DDR3 中读取数据,并将数据写回到 DDR3 中。

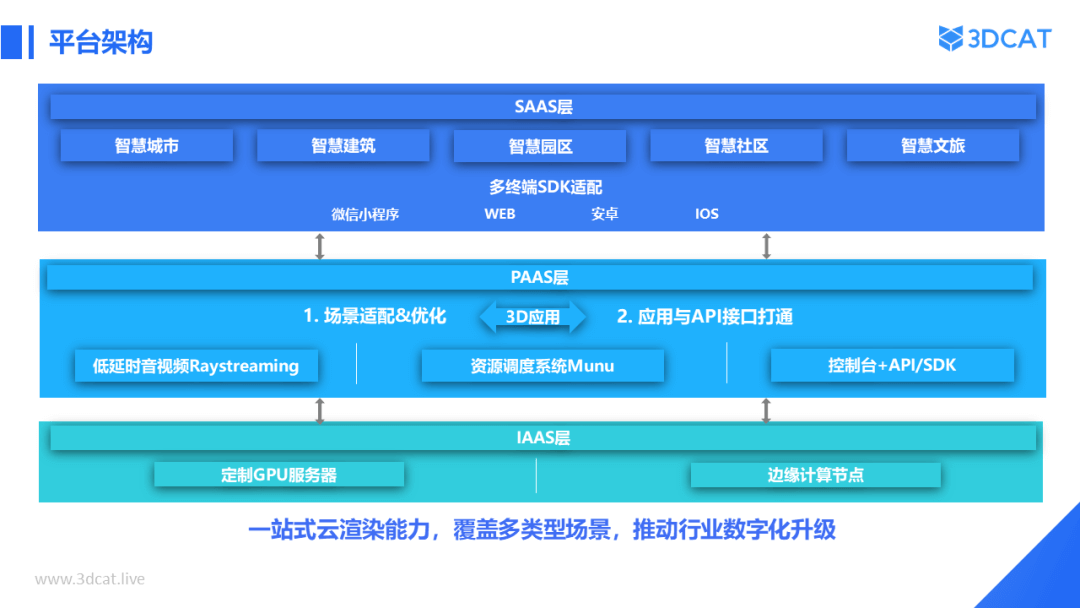

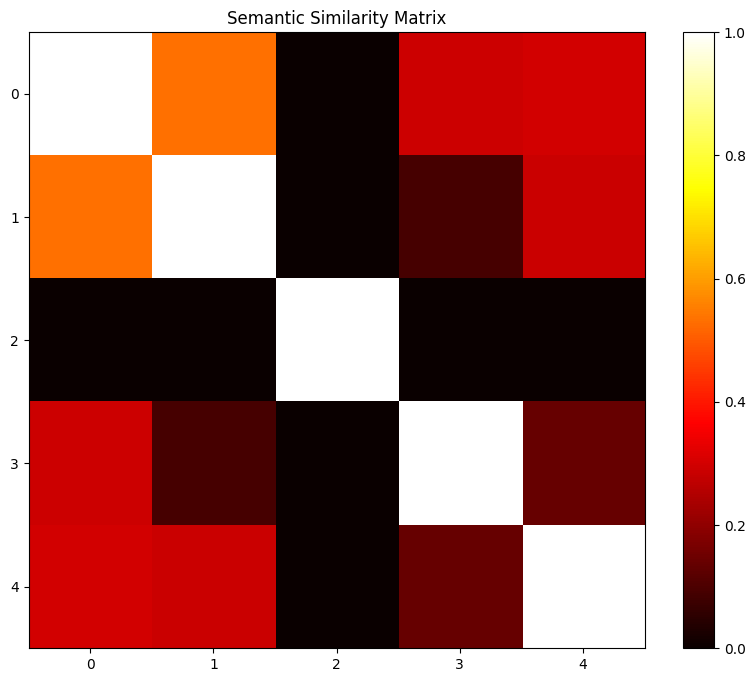

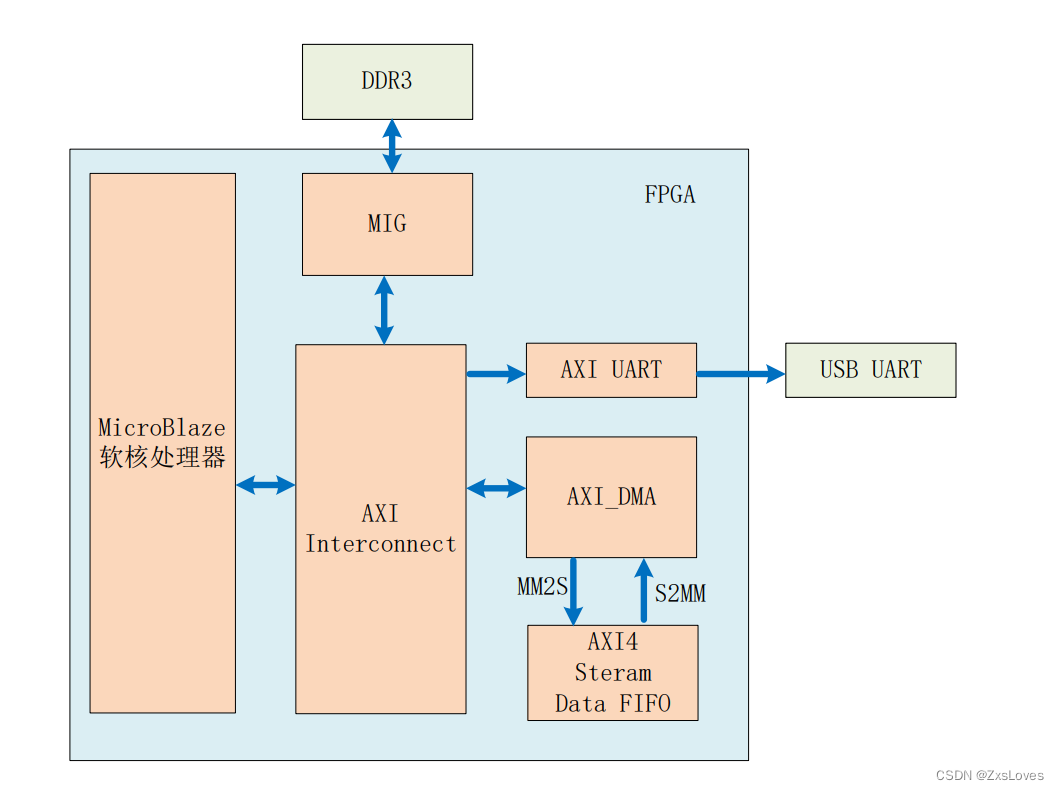

下面展示 Micro Blaze 的 系统框图

这是 AXI DMA环路测试系统的框架图

我们会发现这其中 使用了一个我们上一个实验用过的MIG IP核

我们现在去 《正点原子的达芬奇 FPGA专栏了解 MIG的工作原理》

此处来自 正点原子 达芬奇 FPGA教学的 第44章节

DDR3 SDRAM(Double-Data-Rate Three Synchronous Dynamic Random Access Memory)是 DDR SDRAM 的第三代产品,相较于 DDR2,DDR3 有更高的运行性能与更低的电压。DDR SDRAM 是在SDRAM 技术的基础上发展改进而来的,同 SDRAM 相比,DDR SDRAM 的最大特点是双沿触发,即在时钟的上升沿和下降沿都能进行数据采集和发送,同样的工作时钟,DDR SDRAM 的读写速度可以比传统的SDRAM 快一倍。本次实验使用的 DDR3 芯片是南亚的 NT5CC128M16IP-DI,NT5CC128M16IP-DI 的 bank位宽为 3,行位宽为 14,列位宽为 10,所以它的地址大小等于 23*2142^10(即 2^27=128M),数据位宽为 16bit,所以容量大小为 128M16bit,也就是 256MByte。

由于 DDR3 的时序非常复杂,如果直接编写 DDR3 的控制器代码,那么工作量是非常大的,且性能难以得到保证。值得一提的是,Artix7 系列 FPGA 自带了 DDR3 控制器的硬核,用户可以直接借助 IP 核来实现对 DDR3 的读写操作,从而大大降低了 DDR3 的开发难度。所以我们一般来说,是使用 MIG 这样的IP控制器 来对DDR3 进行赋值操作

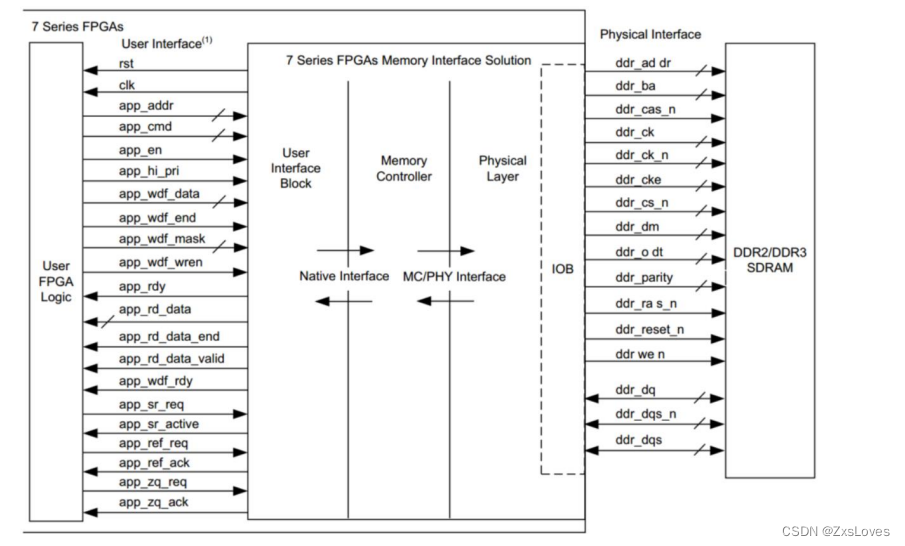

我们观察一下 MIG的结构框图

MIG IP核 对外分出了两组接口。左侧是用户接口(用户端 FPGA 同 MIG交互的接口)

右侧为 DDR 物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。这一侧用户只负责分配正确的管脚,其他不用关心。

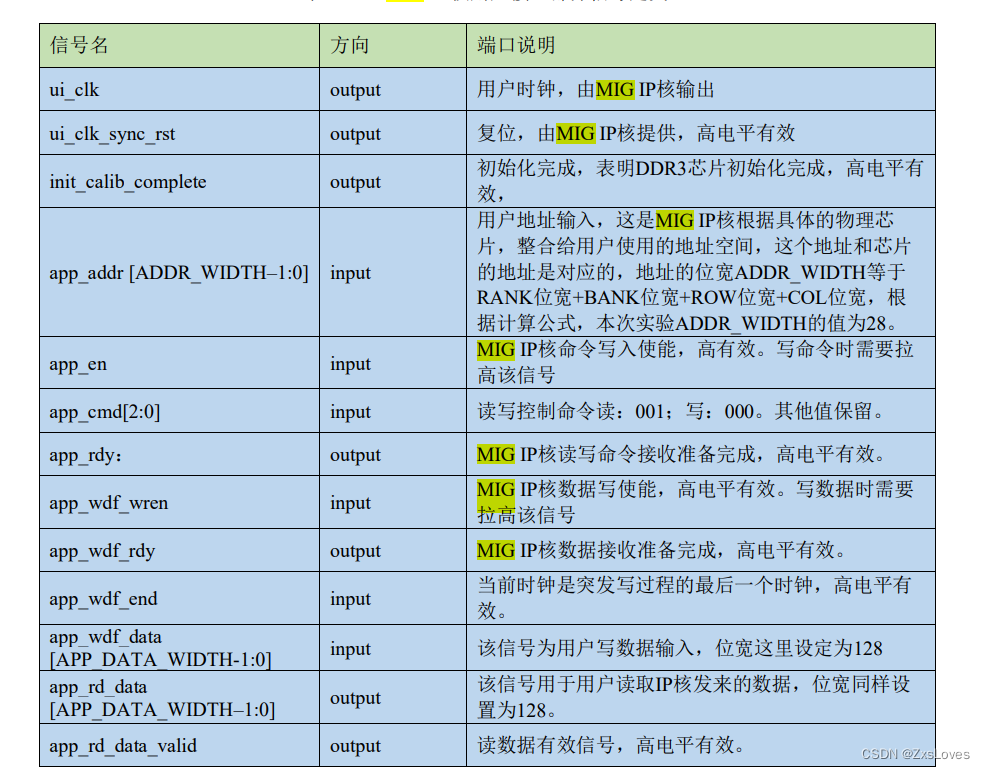

使用这个 IP 核,用户将可以进行 DDR3 的读写操作而不必熟悉 DDR3 具体的读写控制时序,当然用户必须掌握用户接口侧的操作时序,并严格遵照时序来编写代码,这样才能正确实现对 DDR3 的读写操作。在了解具体时序之前,大家有必要先了解相关的信号定义。下图给出了 MIG IP 核用户接口的信号及其说明

MIG IP 核用户侧端口数量共 26 个,当然用户并不用去关心所有的信号,只需要了解本实验要用到几组重要信号。下面将对这些信号逐一讲解并以表格的形式呈现给大家。为了与官方的文档保持一致,表中标明的信号的方向是以 MIG IP 核作为参照的,例如表格中的信号方向定义为输出,那么相对于用户端(FPGA)来说实际上是输入。

以上是用户需要用到的信号,其他信号请大家自行了解。DDR3 的读或者写都包含写命令操作,其中写操作命令(app_cmd)的值等于 0,读操作 app_cmd 的值等于 1。首先来看写命令时序,如下图所示。首先检查 app_rdy,为高则表明此时 IP 核命令接收处于准备好状态,可以接收用户命令,在当前时钟拉高app_en,同时发送命令(app_cmd)和地址(app_addr),此时命令和地址被写入。

大概get 到了 我们现在回到 Micro Blaze 的章节

我们继续研究下整个结构

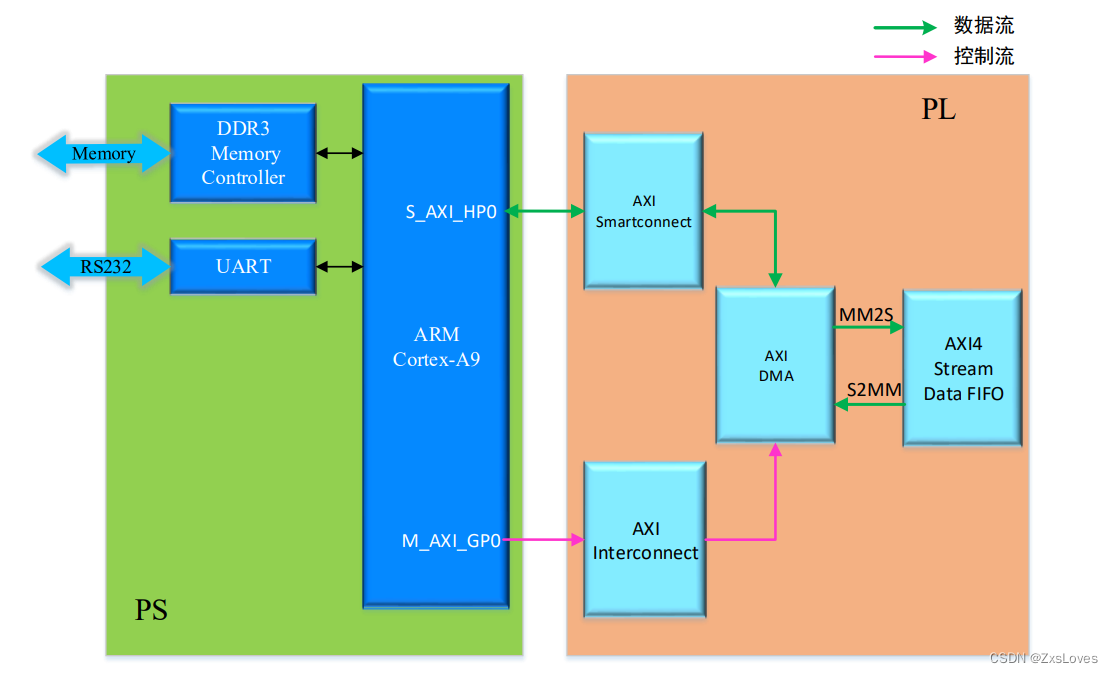

MicroBlaze处理器通过互连模块与AXI DMA IP核通信,从而实现设置、启动和监控数据传输。AXI DMA IP 核通过互连模块从 DDR3 中读取数据后发送给 AXI4 Stream Data FIFO,在这种情况下 AXI4 Stream Data FIFO 模块可以充当带有 Stream 接口的高速 DA。AXI DMA IP 核读取 AXI4 Stream Data FIFO 模块中的数据后通过互连模块将数据写入 DDR3,在这种情况下 AXI4 Stream Data FIFO 模块充当带有 Stream 接口的高速AD。

我们要有举一反三的精神 比照一下之前的 DMA 环路实验

接下来 我们回到现在的 Micro Blaze 的搭建 我们回到vivado

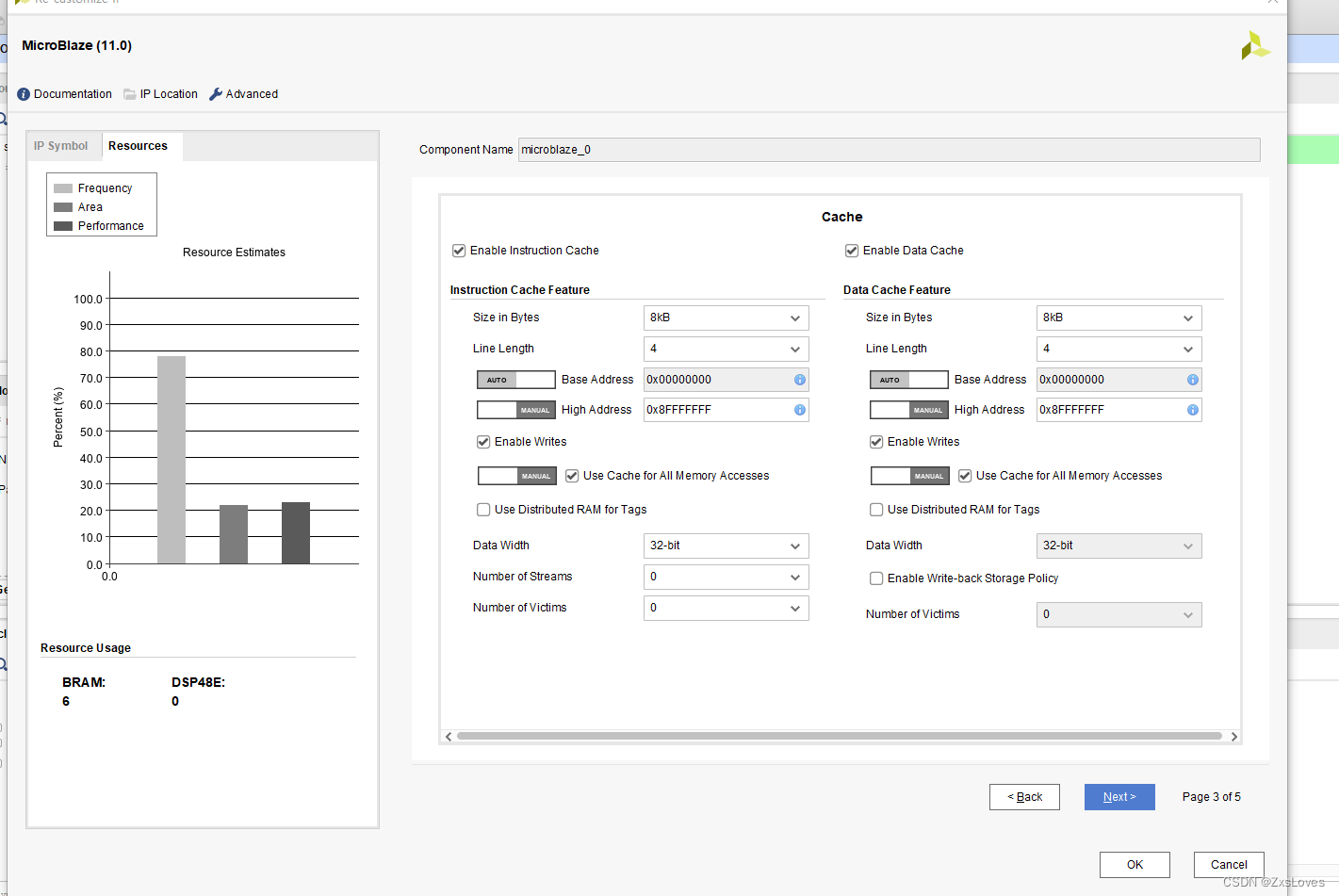

第二页 基本上是 一些优化的选项 我们无需变动 这里第 三页是配置 cache 的 选项

这里是对cache的配置

Debug 保持不变

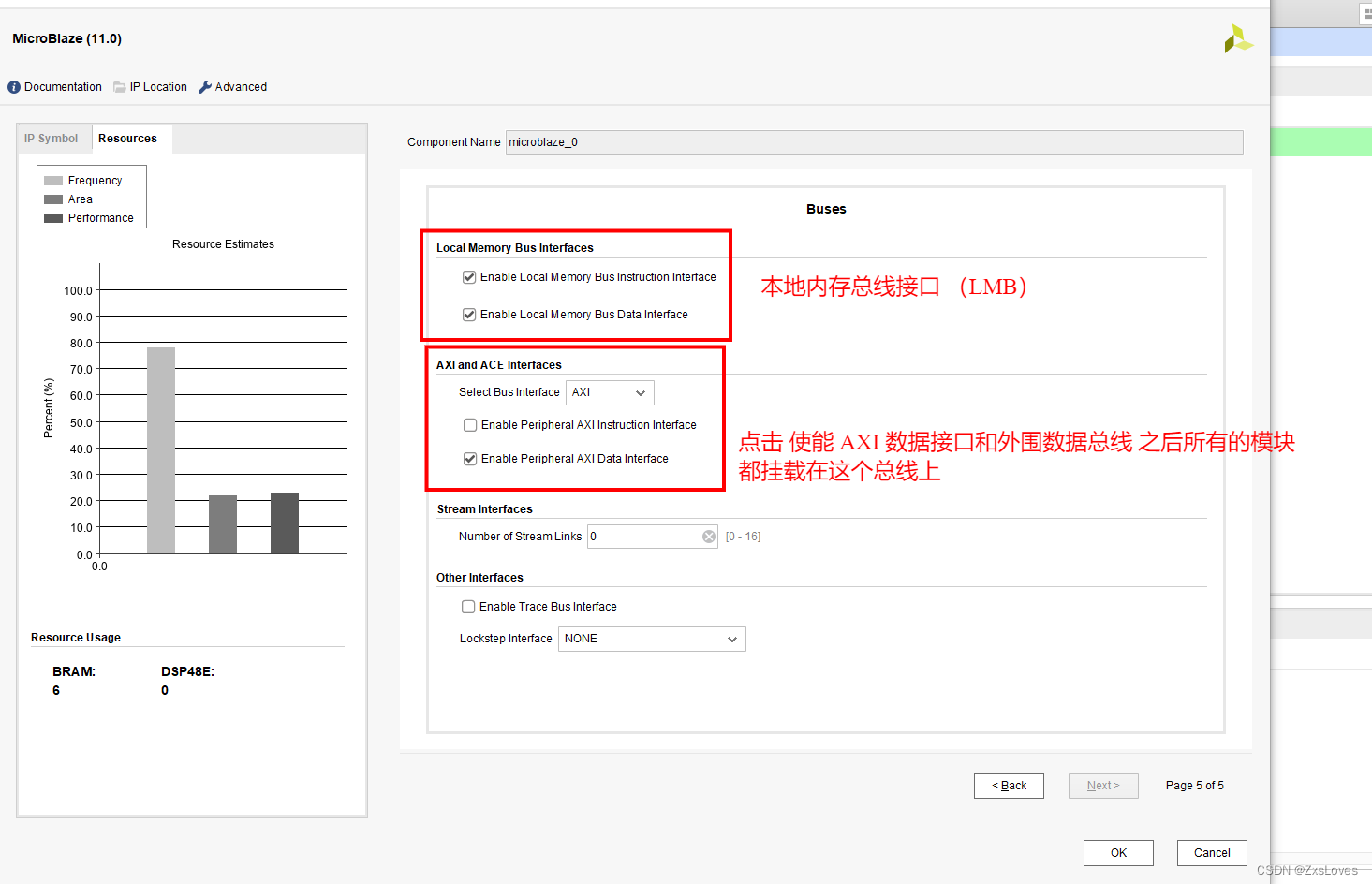

接下来 我们来看 Buses 的 配置

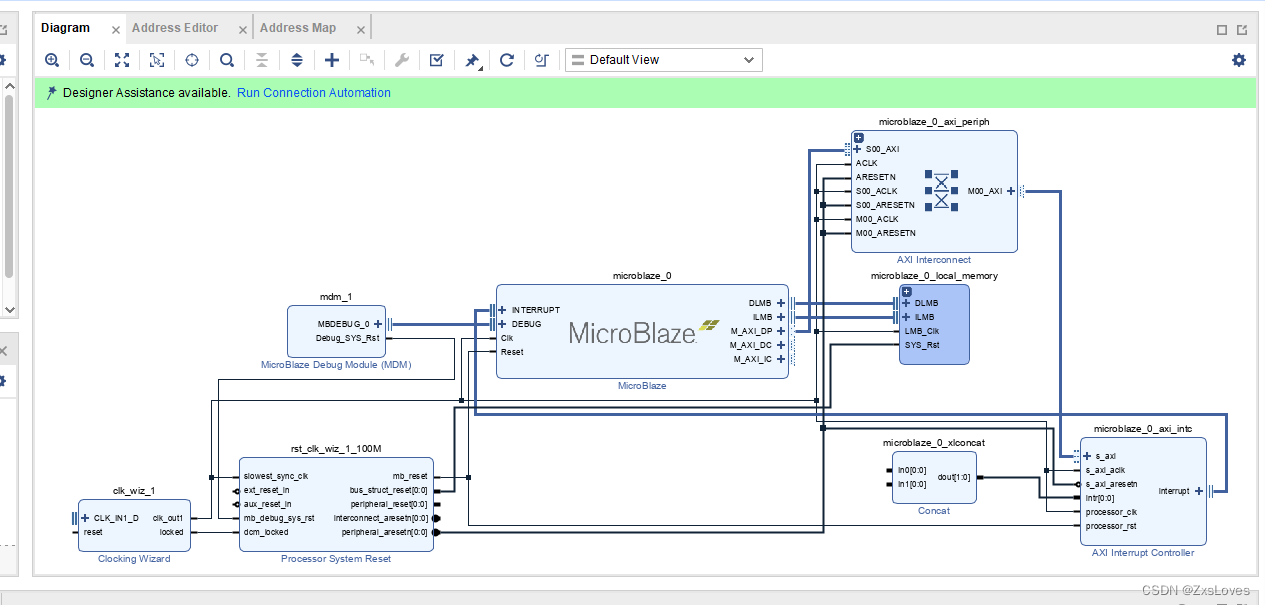

这样子 我们先生成 block design

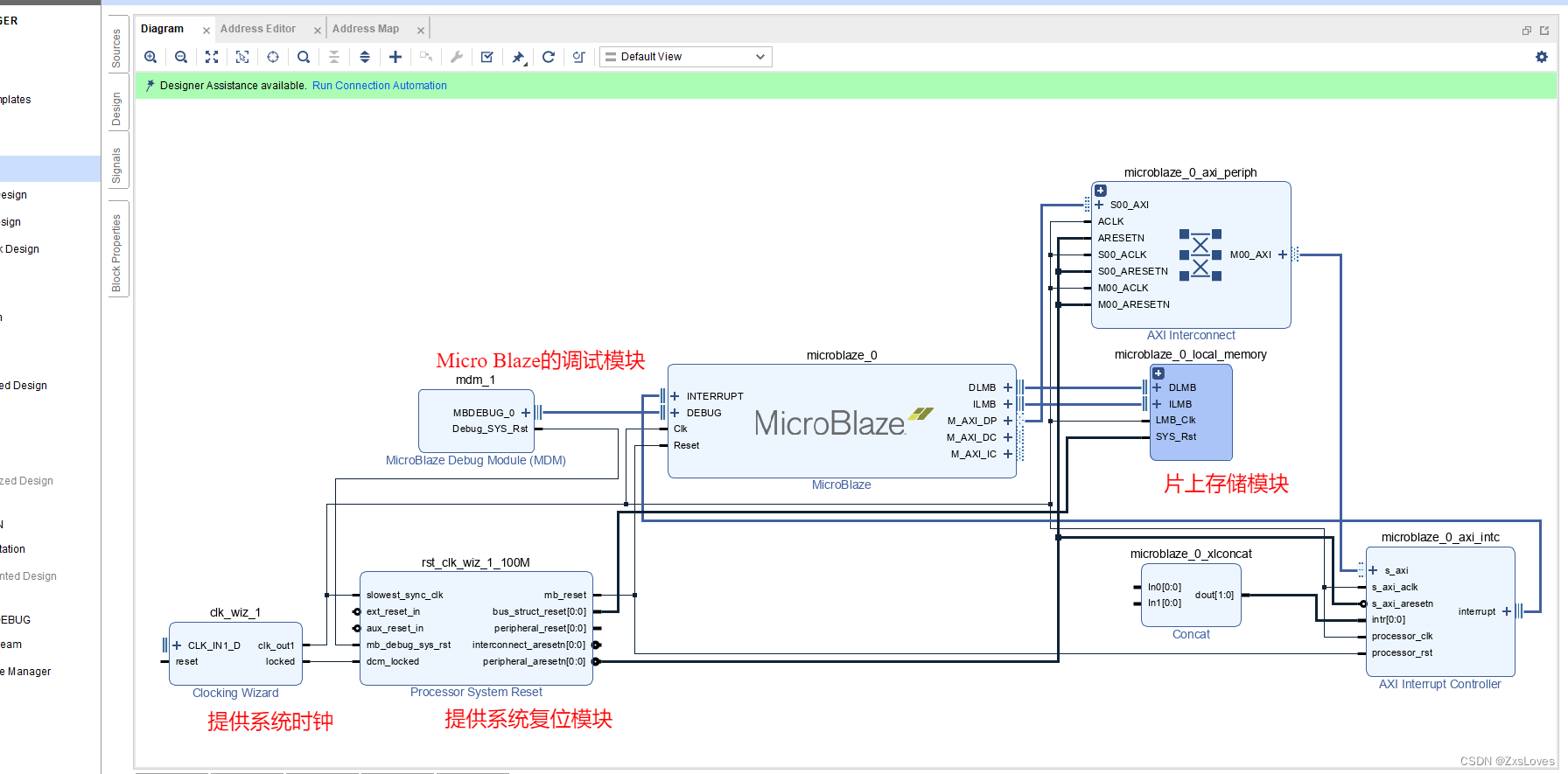

下面是 我们多个模块的作用

下面 我们 进行一系列优化之后的 Block Design

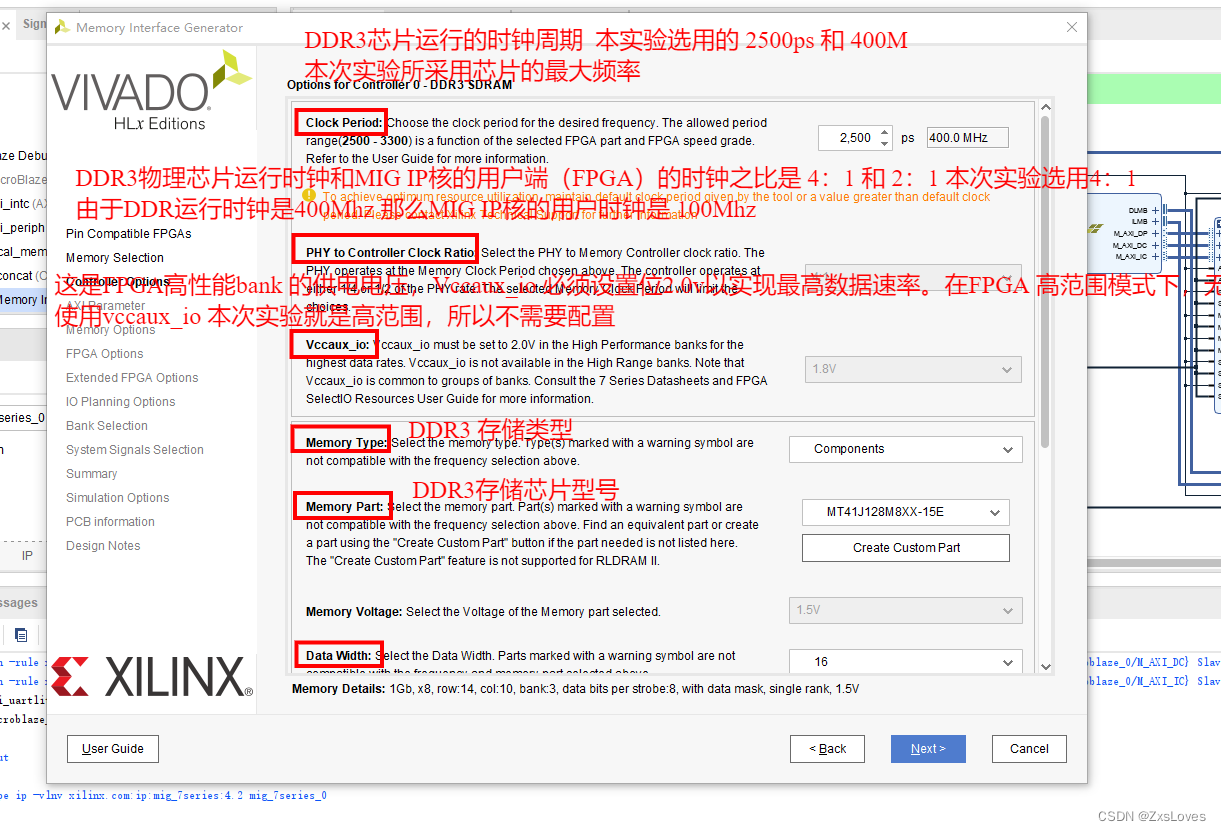

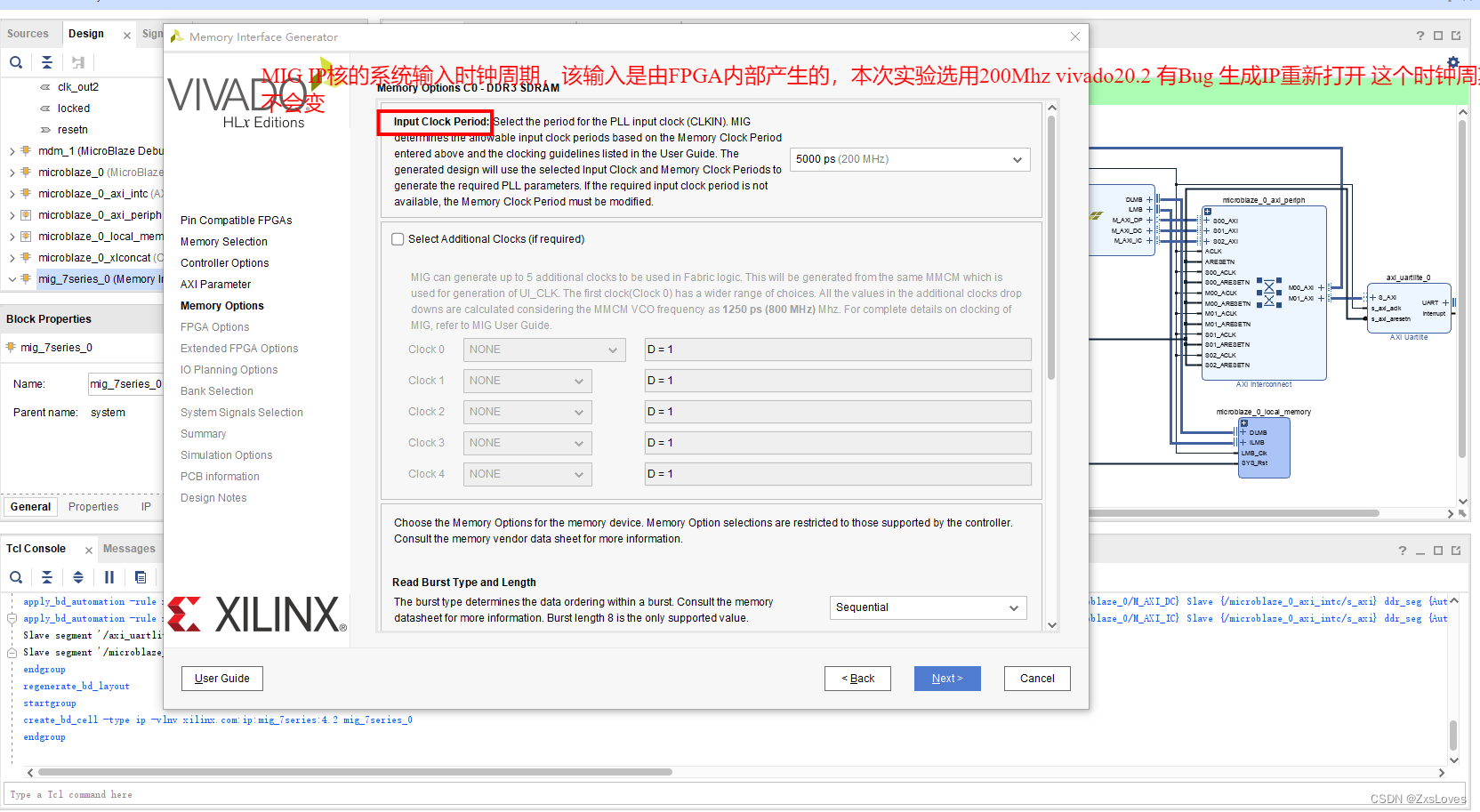

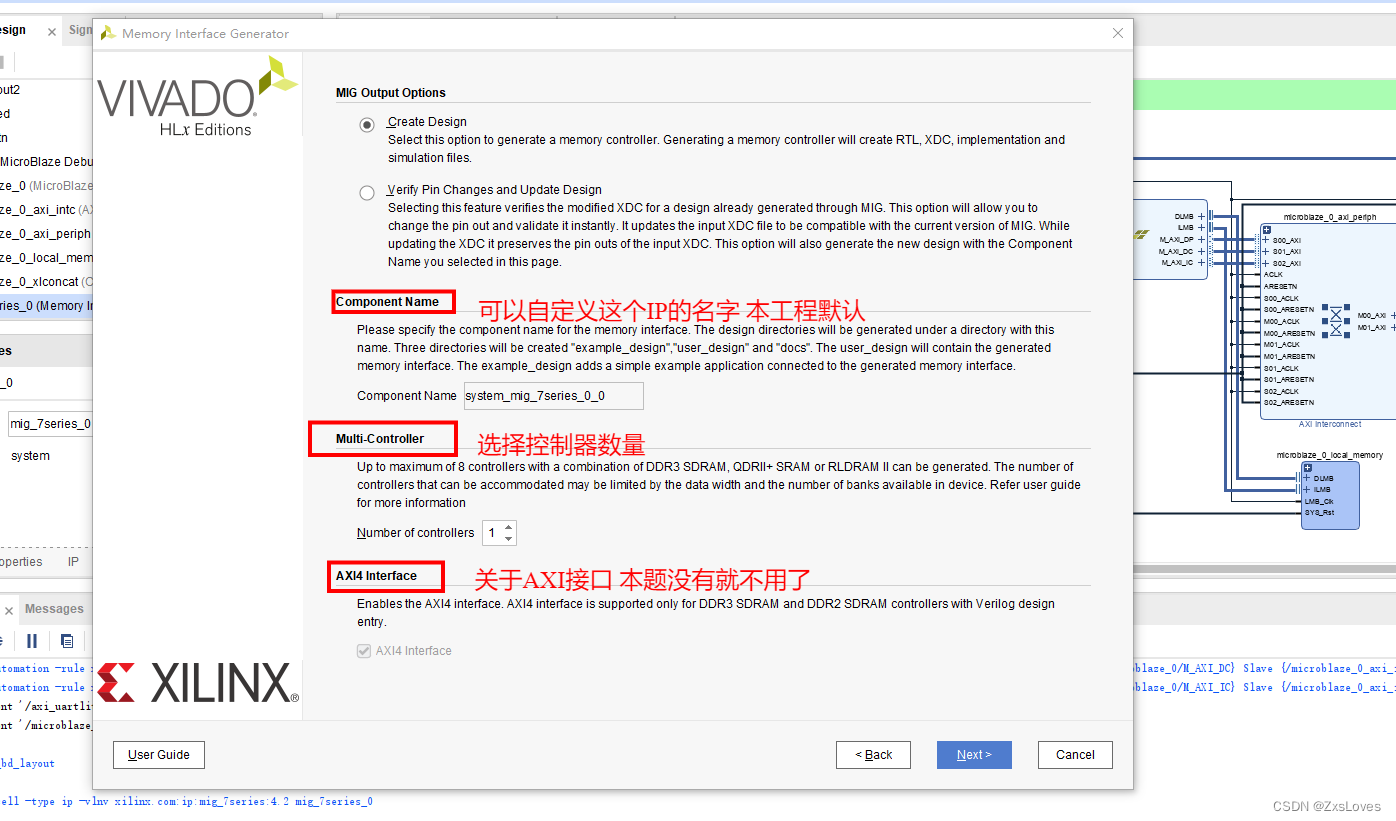

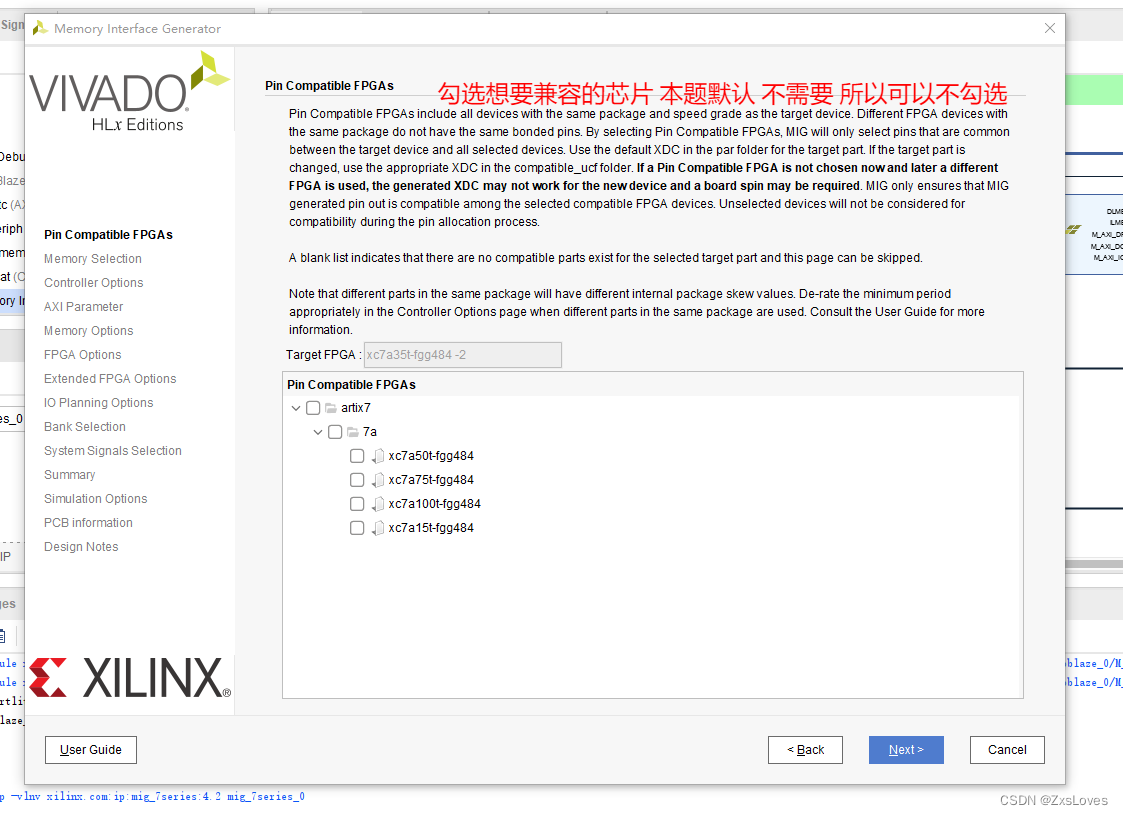

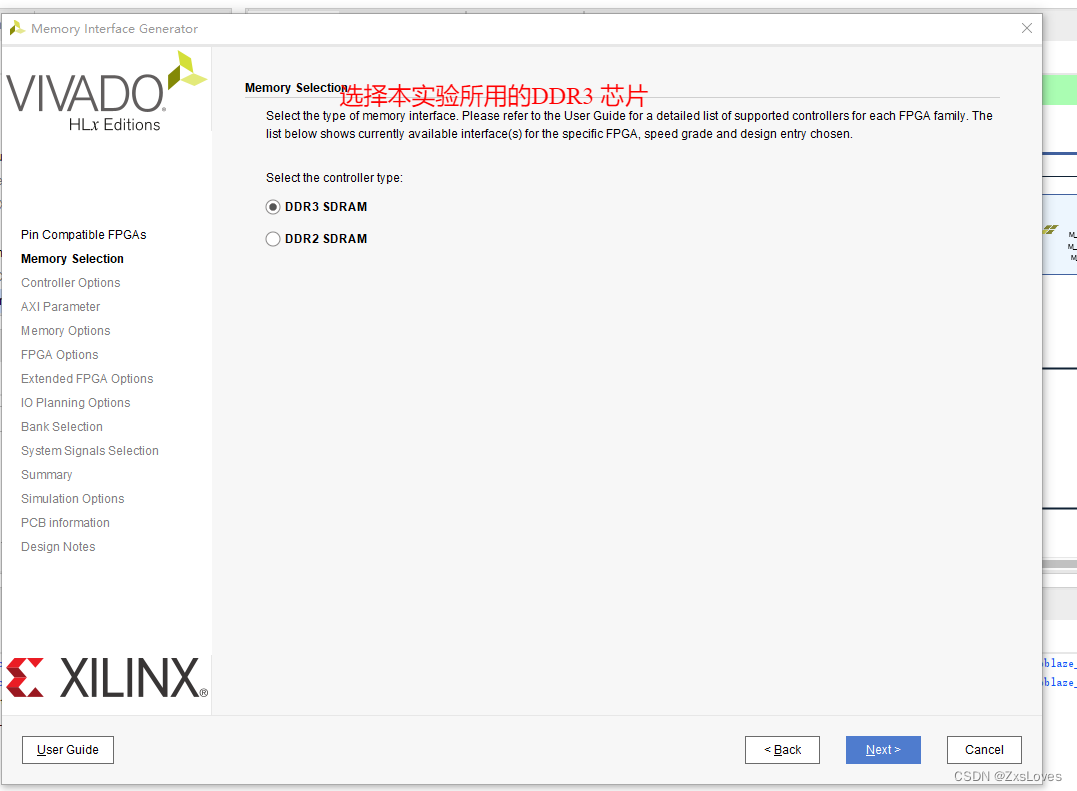

下面我来讲述一下 MIG 的配置原理 及 使用

下面是对Controller Options