关于布局规划

布局规划有助于设计满足时序要求。当设计难以始终如一满足时序要求或者从未满足时序要求时 , AMD 建议您执行布局规划。如果您与设计团队协作并且协作过程中一致性至关重要, 那么布局规划同样可以发挥作用。布局规划可通过减少平均布线延迟来改进建立时间裕量( TNS 和 WNS ) 。在实现期间 , 时序引擎致力于解决最差情况建立时间违例和所有保持时间违例。布局规划只能改进建立时间裕量。当网表采用层级结构时, 手动布局规划最为简单。如果综合将整个网表平铺 , 那么设计分析会明显变慢。请将综合设置为生成层级网表。对于 Vivado 综合 , 请使用 :

• synth_design -flatten_hierarchy rebuilt

或

• Vivado 综合默认策略

含交错逻辑路径的大型层级块可能分析难度较大。在较低的次级层级中采用独立逻辑结构的设计更便于分析。最好寄存层级模块的所有输出。走线穿过多个层级块的路径布局分析难度较大。

了解布局规划基础知识

并非每项设计都能始终满足时序。您可能需要为工具提供解决方案指南。布局规划支持您引导工具完成高层次层级布局或详细门电路布局。

您将通过修复最严重的问题或者最常见的问题来最大程度改进结果。例如 , 如果存在离群路径并且这些路径的裕量明显极差或者具有高层次的逻辑, 那么首先需修复这些路径。“ Reports ” → “ Timing ” → “ Create Slack Histogram ”(报告 > 时序 > 创建裕量直方图 ) 命令可以提供离群路径视图。或者 , 如果在多个负时序裕量路径中出现相同的时序端点, 那么改善其中一条路径可能可为该端点上其他路径实现相同的改善效果。可考虑利用布局规划通过减少布线延迟或者增加非关键块上的逻辑密度来提高性能。逻辑密度是对应芯片上的逻辑封装紧密程度的指标。

布局规划可帮助您满足更高的时钟频率要求并提升结果的一致性。有多种方法适用于布局规划 , 每种方法都各有优缺点。

详细的门级布局规划

详细的门级布局规划涉及在器件上的特定 site ( 站点 ) 内对个别叶节点单元进行布局。

详细的门级布局规划的优势

• 详细的门级布局规划适用于手动布线的信号线。

• 详细的门级布局规划可以最大限度发挥器件性能。

详细的门级布局规划的劣势

• 详细的门级布局规划较为耗时。

• 详细的门级布局规划需要具备有关器件和设计的广泛知识。

• 如果网表发生变更 , 详细的门级布局规划可能需重做。

建议 : 请将门级布局规划作为最终手段来使用。

信息复用

复用来自满足时序的设计的信息。如果设计无法始终如一满足时序 , 请使用此流程。要复用信息 , 请执行以下操作 :

1. 打开 2 个实现运行 :

a. 1 个对应满足时序的运行。

b. 另 1 个对应不满足时序的运行。

2. 查看 2 项设计之间的区别。

a. 通过 report_timing_summary 识别部分失败的时序路径。

b. 在满足时序的设计上 , 以 min_max 模式运行 report_timing , 这样即可对满足时序的设计上的路径进行定时。

3. 比较时序结果 :

a. 时钟偏差

b. 数据路径延迟

c. 布局

d. 布线延迟

4. 如果路径端点之间的逻辑延迟量存在差异 , 请重新执行综合运行。

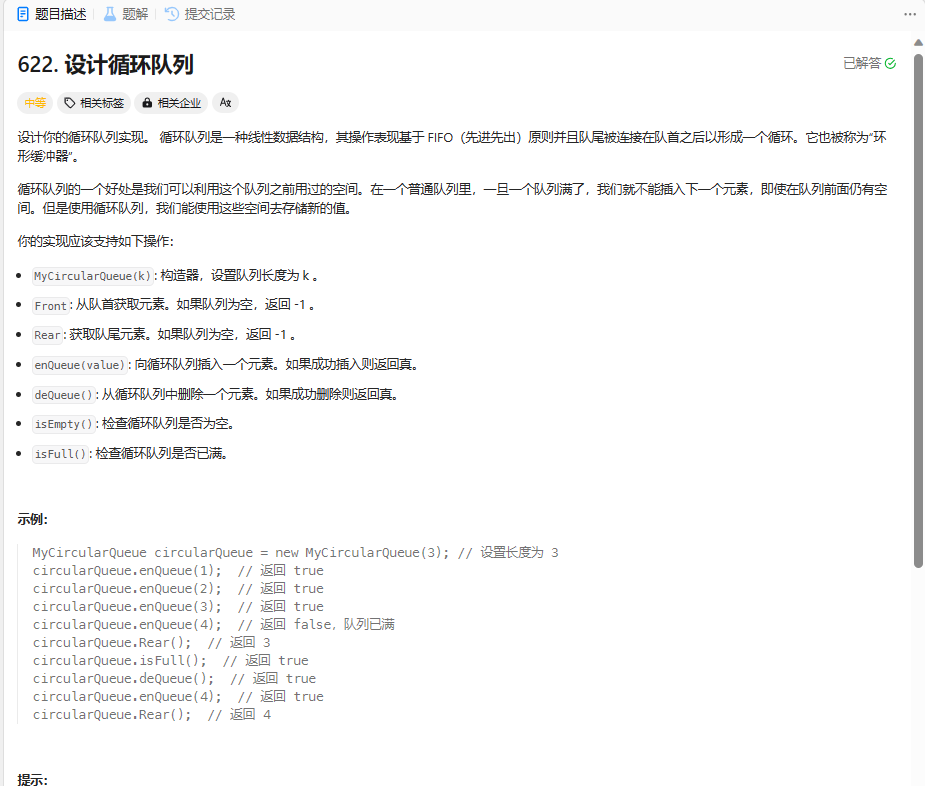

复查 I/O 和单元布局

复查设计中的单元布局。比较 2 份 I/O 报告 , 以复查 I/O 布局和 I/O 标准。确保所有 I/O 均已完成布局。通过简单搜索可以发现不含固定布局的所有 I/O , 如下图所示。

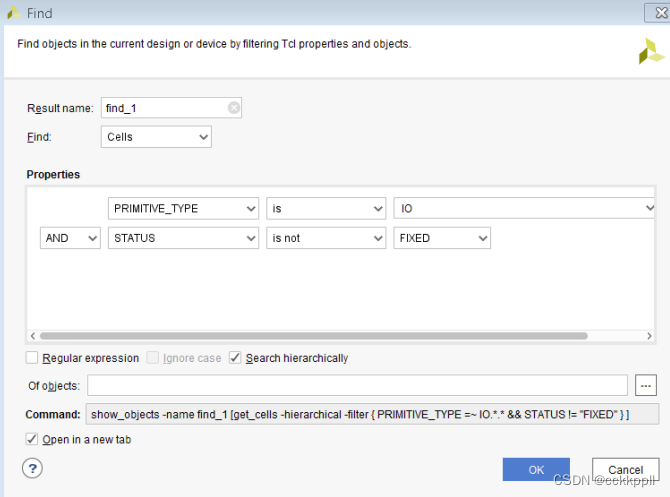

如果不同运行间的时钟偏差发生改变 , 请考虑复用来自满足时序的运行的时钟原语布局。“ Clock Utilization ” ( 时钟使用率) 报告可列出时钟树驱动程序的布局 , 如下图所示。

LOC 约束可轻松复制到 XDC 约束文件中。

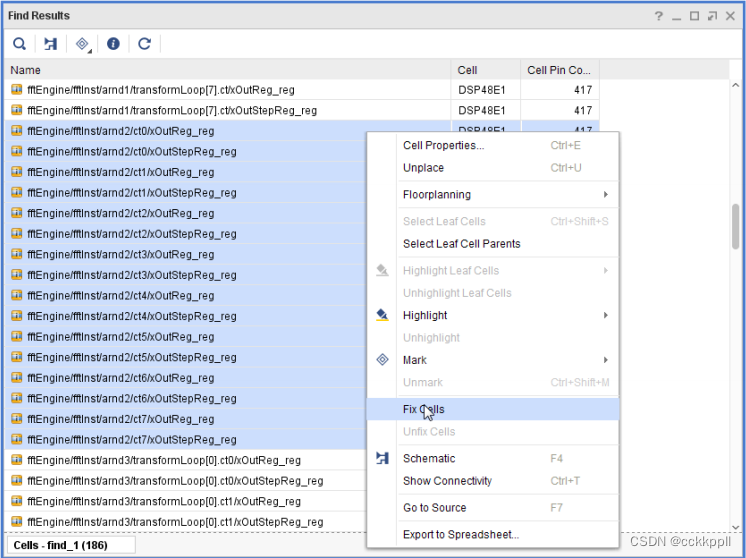

许多设计都已通过复用块 RAM 和 DSP 布局来满足时序。请选择“ Edit > Find ” ( 编辑 > 查找 ) 以列出实例。

添加布局约束

固定逻辑以便向 XDC 添加布局约束。

1. 从查找结果中选择宏。

2. 右键单击并选中“ Fix Cells ” ( 固定单元 ), 如下图所示。

复用布局

I/O 、全局时钟资源、块 RAM 宏和 DSP 宏布局十分便于复用。复用此布局有助于减少各网表版本之间的结果差异。这些原语通常具有稳定的名称。布局通常易于维护。

对增量编译复用布局

增量编译支持复用来自上一次运行的布局布线数据。只需在 place_design 前引用现有已布局或已布线的 DSP 即可完成复用设置。可复用完整设计、任一层级或单元类型( 如 , DSP 或块 RAM ) 。增量编译还可自动处理对设计某些部分执行的更改。