三、NAND接口

NAND闪存接口是连接主机控制器与NAND存储芯片的通信桥梁,负责命令、地址和数据的传输。典型的NAND闪存接口包括一组I/O线(通常为8条或更多)用于数据传输,以及若干控制信号线。

基本接口信号:

-

Chip Enable (CE#):低电平有效,当CE#信号被拉低时,选定的NAND器件开始响应并执行相应的操作。

-

Write Enable (WE#) 和 Read Enable (RE#):分别用于指示写入和读取操作的开始。

-

Address Latch Enable (ALE):用于将总线上的数据锁定为地址信息。

-

Command Latch Enable (CLE):用于将总线上的数据锁定为命令信息。

-

Data Input/Output (I/O0-I/O7 or more):双向数据总线,根据CLE或ALE的状态来传输命令、地址或数据。

-

Ready/Busy (R/B#, R/B, 或 WP#):表明NAND设备是否准备就绪或者正在进行内部操作。

在实际操作中,控制器首先通过控制信号将命令、地址传送到NAND芯片,然后通过I/O线进行数据交换。例如,为了读取一个Page的数据,主控会先发送读命令到CLE,接着送出行地址和列地址,最后从I/O线上接收数据。

在NAND闪存技术发展初期,为了实现高速数据传输,通常采用8位、16位甚至更多位宽的并行接口设计,通过多个独立的数据线(I/O引脚)同时发送地址、命令和数据。这种并行接口虽然能够提供较高的带宽,但其缺点在于需要较多的物理引脚,从而增加了封装尺寸和复杂性,并且不利于小型化设备的应用。

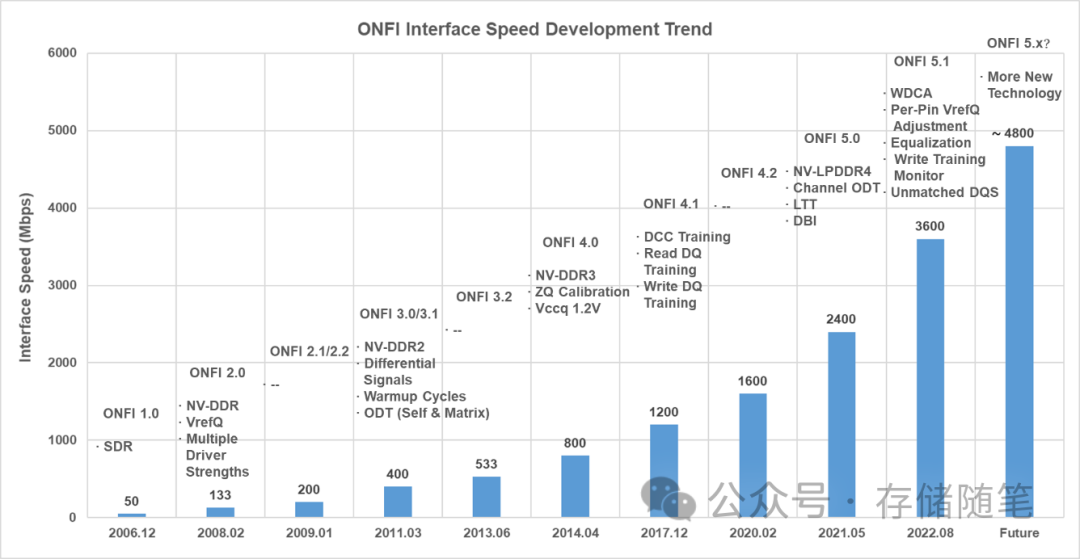

随着技术的发展,串行接口逐渐成为主流,比如ONFI(Open NAND Flash Interface)、Toggle模式等更高级别的存储接口标准,它们通过较少数量的引脚实现了更高的数据传输效率。

(1)ONFI接口

ONFI是由包括Intel、Micron、Hynix等在内的多家公司于2006年联合创建的标准,致力于统一NAND闪存接口规范。

ONFI使用并行或串行接口进行操作,早期版本侧重于并行接口设计,定义了NAND芯片与主控之间的信号时序、命令格式以及电气特性。随着技术发展,ONFI也推出了支持串行通信的标准,如ONFI 4.0引入了ONFi over PCIe (OoP) 接口,实现高速低延迟的数据传输。

ONFI注重兼容性和标准化,通过优化时序参数来提升性能,并且对错误纠正机制有明确的规定,以保证数据的可靠性和完整性。

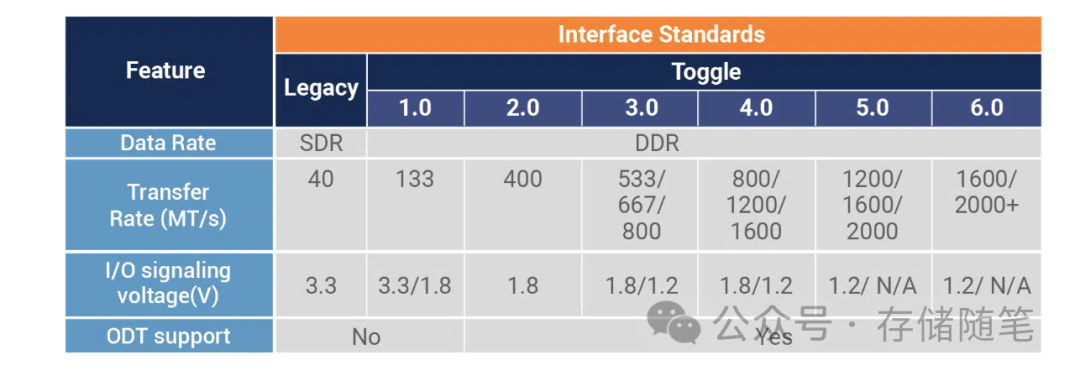

(2)Toggle接口

最初由三星和东芝主导开发,尤其是Toggle DDR(Double Data Rate)标准,它利用DDR技术在时钟的上升沿和下降沿传输数据,从而实现更高的数据吞吐量。

Toggle接口采用串行通信方式,相比ONFI最初的并行接口,能够减少引脚数量,降低封装复杂性。Toggle DDR在单一I/O线上同时读写两个比特的数据,进一步提高了速度。

ONFI和Toggle接口虽然起源于不同厂商阵营,两个阵营各自推广自家标准,但在共同推动NAND闪存技术进步方面起到了重要作用,市场和技术的发展促使双方寻求更多的兼容性和合作,业界正趋向于融合两种标准的优势,提供更通用、高效的解决方案。