通过NAND Flash总线传输的信号分为三种类型:命令(Commands)、地址(Addresses)和数据(Data)。这些信号利用DQ[7:0]时间分时复用技术,在不同的时间段分别进行传输。其中,数据采用同步传输和差分采样方式,传输速率较高;而命令和地址则采用异步传输和单端采样,传输速率较低。

但是,NAND接口从ONFI 1.0版本到ONFI 5.1版本,接口速度有了快速提升,但命令、地址和数据的传输形式基本保持不变。随着总线传输速度的增加,主要改进在于减少了数据传输的延迟,然而命令和地址的传输延迟并未得到改善。

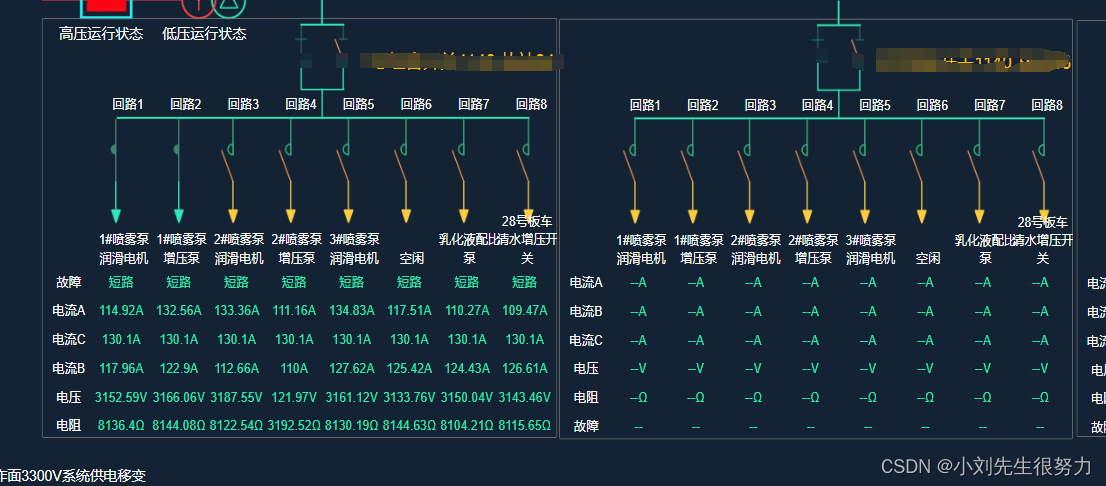

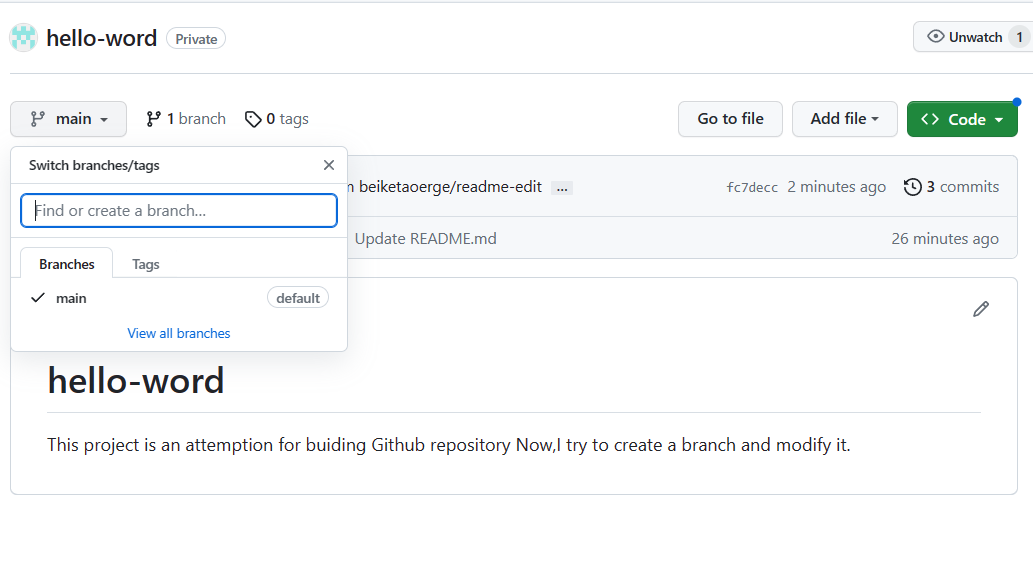

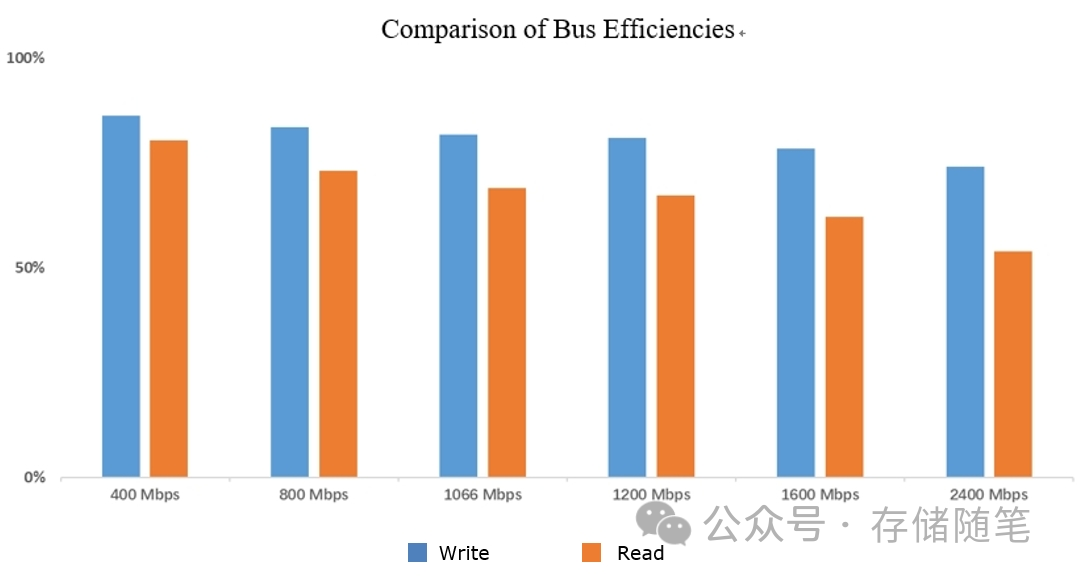

在系统层面,随着总线速度提高,由于命令和地址传输效率未见显著提升,导致整个总线使用效率逐渐下降。如上图,在理想写入/读取场景下总线效率的对比情况,可以看出无论是读取还是写入场景,总线效率都在逐步下滑,特别是在读取场景下,当总线效率降至约50%时,这无疑给系统设计带来了更大的挑战。

尽管NAND闪存接口速度不断提升,但由于命令和地址传输机制的局限性,实际应用中总线资源的利用率并未随速度提升而同步增长,反而出现了效率降低的问题,这对未来系统优化设计提出了新的难题。

当前,面对这一挑战,固态技术协会JEDEC正在深入讨论下一代协议的进化方向,除了继续提高接口速度外,还将优化命令和地址的传输模式,这无疑将给主控芯片的设计带来新的考验。

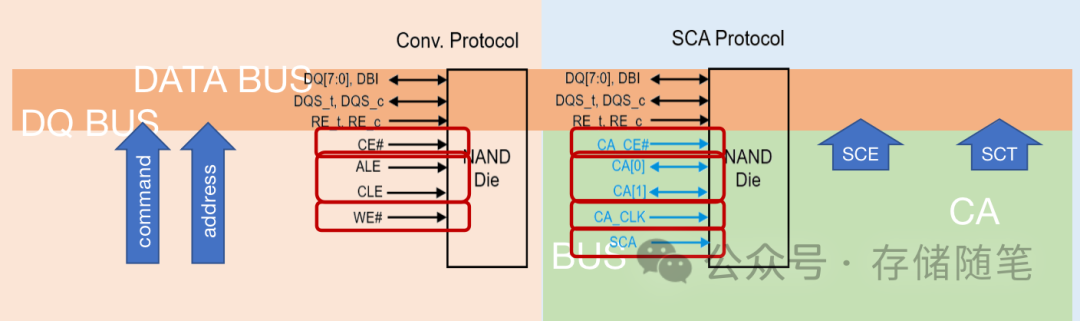

在传统接口中,CE#是NAND闪存的一个关键引脚,用来激活或选择特定的NAND闪存芯片,以便控制器与其进行通信。包括ALE/CLE/WE#等信号。

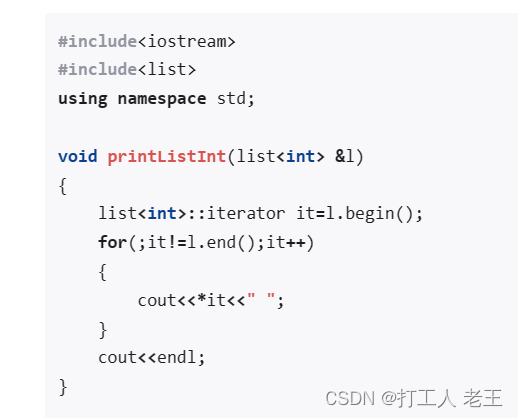

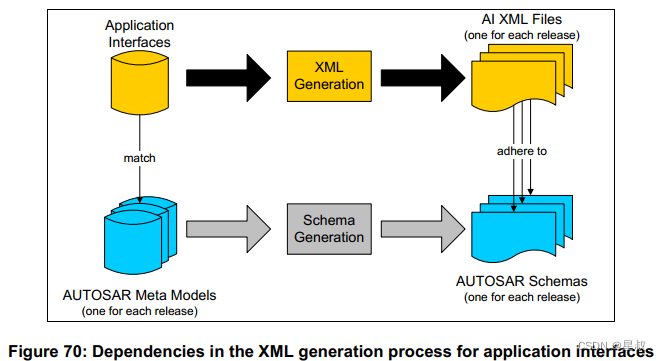

然而,在Separate Command Address (SCA) 接口中,设计思路发生了根本性的变化。SCA接口将命令和地址信号与数据传输分离开来,增加了专门的CA(Command and Address)通道,而不是像传统接口那样混用I/O线传输命令、地址和数据。

传统接口中的CE#和其他引脚主要是用来完成基本的芯片选择、读写操作以及数据和命令地址的并行传输,而SCA引入的CA引脚则是专为串行化命令和地址信息设计,以此实现更高效、灵活的多任务处理能力。

-

CA pins:这些引脚专用于传输命令和地址信息,采用并行转串行的方式,降低了所需的物理引脚数目,同时提高了信号完整性,并允许在数据传输的过程中并发执行命令和地址更改。

-

CA_CLK:用于驱动CA通道的串行数据时钟。

-

CA[1:0] :用于在CA通道上传输串行化的命令和地址数据。

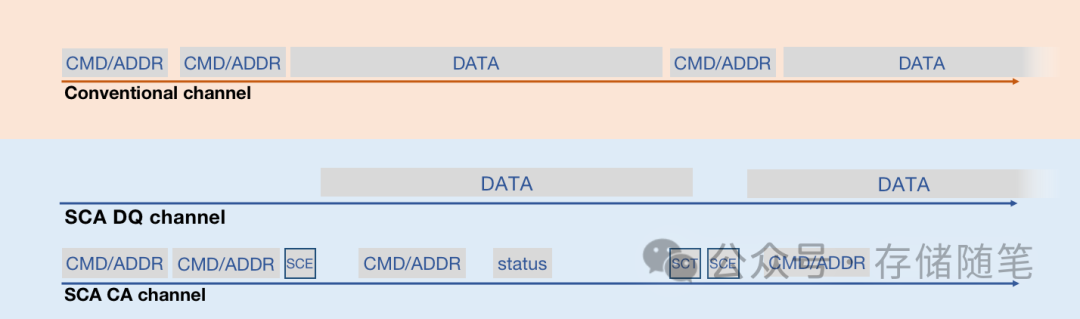

它的主要原理在于将传统的命令和地址(CMD/ADD R)信号与数据传输(DATA/DQ)信号分离到不同的通道上,即创建了专门的SCA CA通道用于命令和地址的串行传输,而DQ通道专注于数据的并行传输。

通过这种方式,SCA接口不仅简化了布线和电路设计,还优化了控制器与NAND闪存之间的交互,允许更高级别的命令交错执行,从而显著提升固态硬盘(SSD)的并行操作能力和整体性能。