配置内存IP

UltraScale体系结构内存IP支持DDR3和DDR4 SDRAM的配置,QDRIIPLUS SRAM和RLDRAM3型接口。截至2015.3,内存IP已被拆分基于内存接口标准和工具流,将其划分为不同的IP。“自定义IP”对话框框包含基本和高级配置选项,其中包括调试。现在记忆I/O分配过程与设计的其余部分合并,IP配置过程与其他AMD IP一致。有关IP配置和管理的更多信息过程,请参阅《Vivado Design Suite用户指南》中的“创建内存IP自定义”一节:用IP(UG896)进行设计。要在Vivado工具中配置内存IP,请执行以下操作:

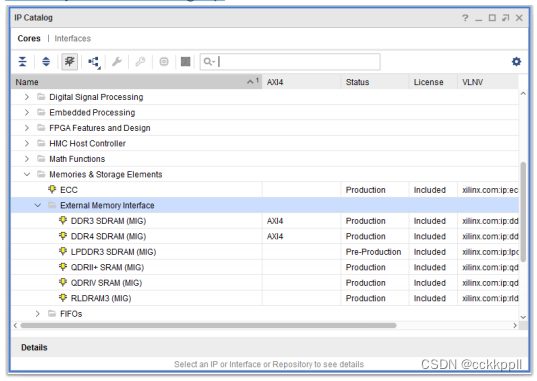

1.打开Vivado IP目录,展开存储器和存储元件 → 外部的内存接口类别。

2.双击所需的界面,打开“自定义IP”对话框。

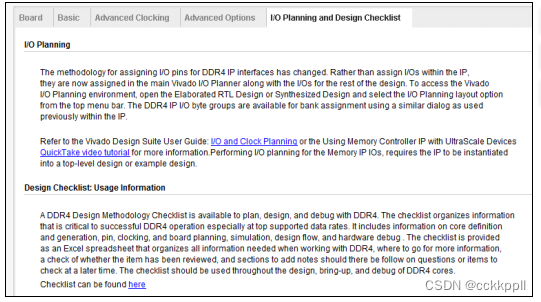

注意:尽管“自定义IP”对话框中仍然存在“I/O规划”选项卡,但它仅解释新的整合的内存IP I/O规划。

有关配置内存IP的信息,请参阅基于UltraScale体系结构的FPGA内存IP LogiCORE IP产品指南(PG150)。

注意:Vivado设计套件在同一位置支持多个UltraScale体系结构的内存控制器设计每个都必须单独定义。

生成IP输出产品

配置内存IP后,必须生成用于实现的输出产品以及第三方工具。当您生成输出产品时,Vivado工具会创建一个IP级别IP目录中的XDC约束文件。XDC文件包含I/O物理约束,例如IOSTANDARD、OUTPUT_IMPEDANCE、DRIVE和SLEW。Vivado工具衍生出这些来自IP中配置设置的约束,以帮助进行I/O规划。约束出现在I/O规划视图布局中。有关生成输出产品的更多信息,请参阅中的“生成输出产品”一节Vivado Design Suite用户指南:使用IP进行设计(UG896)。

UltraScale体系结构内存IP I/O

Vivado IDE中的规划如果您的设计包含UltraScale体系结构内存IP,Vivado IDE包括以下内容特殊功能:

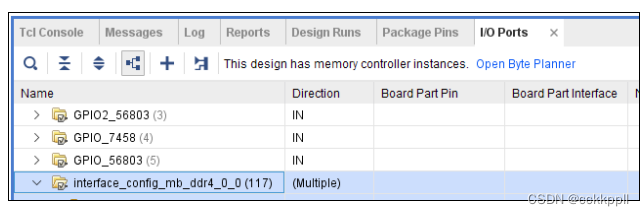

•将每个内存IP的I/O端口分组到I/O端口窗口中的端口接口中启用组选择和修改

•防止所有与内存IP相关的端口使用交互式端口放置功能,例如在图形视图中拖放、交换端口或手动移动端口

•提供内存库/字节规划器,允许自动或手动分配内存I/O引脚组到I/O组和字节通道您可以通过打开详细的RTL设计或Vivado IDE中的综合设计。对于精心设计和综合设计,您可以使用相同的基本过程和命令。然而,Vivado工具执行更详细的DRC在综合设计中。

中的UltraScale体系结构内存IP I/O规划精心设计

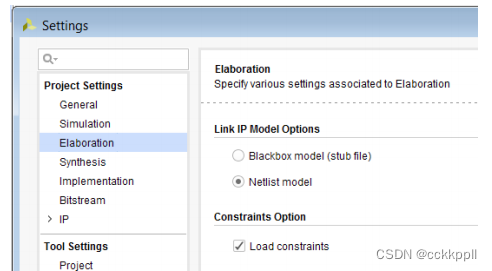

在使用详细设计进行内存I/O规划时,必须设置适当的详细设计打开设计之前的选项如下:

1.在Vivado IDE中,选择Flow → 精化设置。

2.在“项目设置”对话框中,确保“网表模型”和“加载约束”选项被选中。

加载网表模型允许详细设计读取具有所选的I/O属性,如IOSTANDARD和OUTPUT_IMPEDANCE。如果您使用黑匣子模型,您不能在详细设计中做内存IP I/O规划。

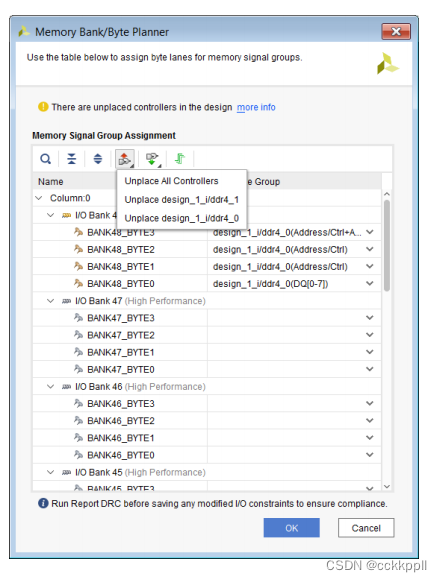

使用内存库/字节规划器

I/O规划视图布局包括I/O端口和封装引脚窗口。如果UltraScale架构内存IP存在于设计中,两个窗口的横幅都包含一条消息和启动内存库/字节规划器的按钮。

注意:或者,您也可以通过选择“工具”打开“内存库/字节规划器” → I/O规划 → 内存字节规划器。您可以使用内存组/字节规划器自动或手动分配内存接口信号组到I/O组内的特定字节组。

注意:如果使用直接从内存IP生成的示例设计,则示例中的XDC文件该设计提供了出现在内存库/字节规划器中的默认I/O分配。内存库/字节规划器包括以下功能:

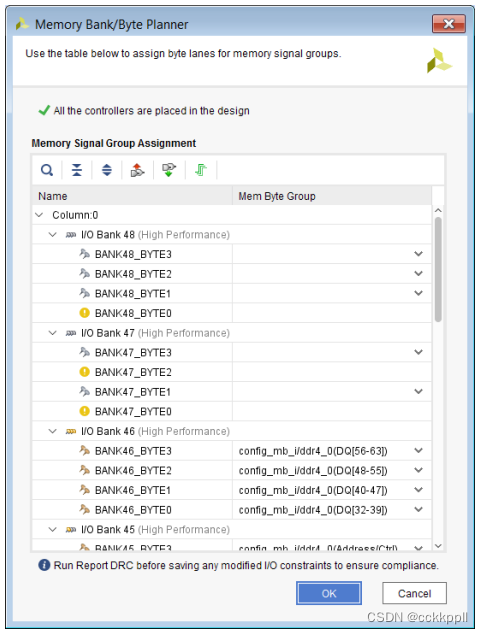

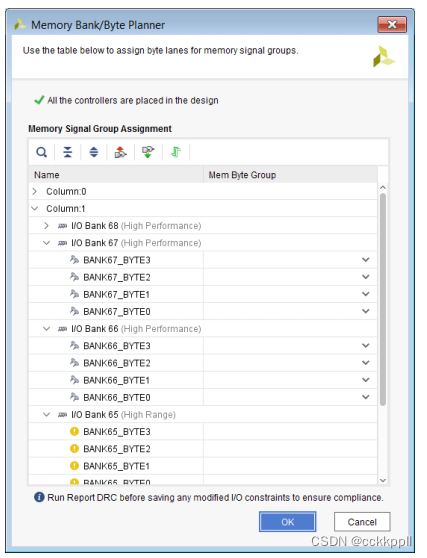

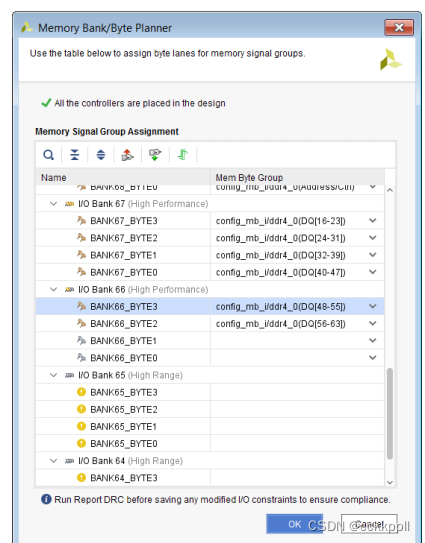

•可折叠设备资源树:设备资源,如超级逻辑区域(SLR)、I/O列、组和字节组显示在可折叠和可扩展的树中取决于所选择的设备。可以折叠树以针对的特定区域设备,如下图所示。树按资源的顺序显示资源出现在设备上,因为必须将内存接口分配给相邻的I/O组。

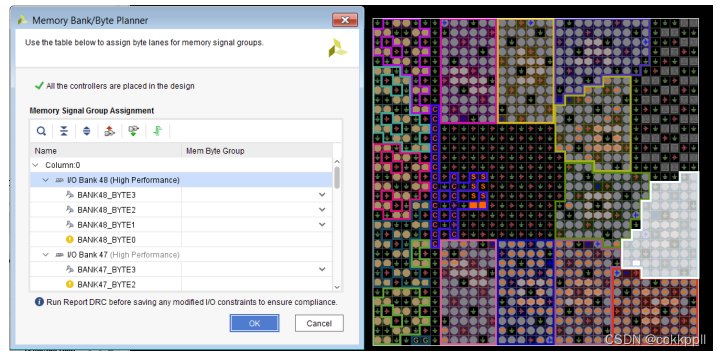

•与其他视图的交叉选择:当您选择I/O组和字节组时,组为也在Package和Device窗口中突出显示,以帮助识别资源,如如下图所示。

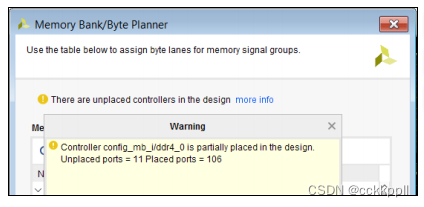

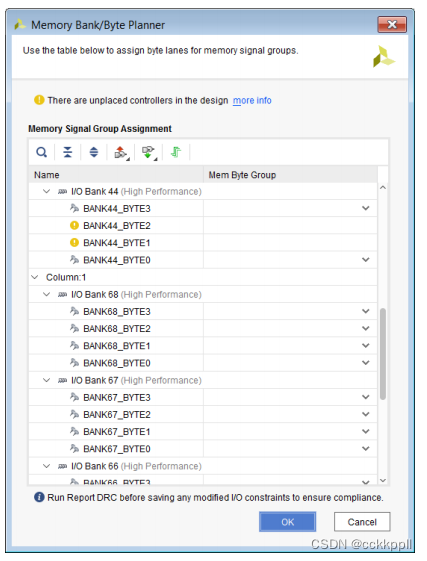

•DRC信息:在内存库/字节规划器(下图)的顶部,DRC状态消息提供有关DRC违规的信息以及指向更多信息的链接。当您选择I/O组和字节组时,这些组也会在软件包中突出显示和设备窗口,以帮助识别资源,如下图所示。

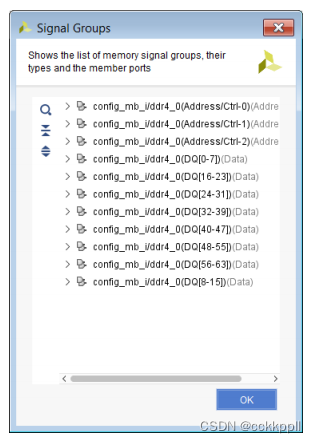

•信号组信息:点击显示信号组按钮显示信号列表“信号组”对话框中每个内存IP的组。

手动分配信号组

要手动将信号组分配给字节通道:

1.在下图中的Mem Byte Group列中,单击

2.选择要分配的信号组。

每次分配后,Vivado工具都会运行活动的DRC。DRC违规显示为红色,而您可以点击更多信息链接了解详细信息。Vivado IDE显示每个内存IP的信号组这样您就可以同时为多个内存控制器规划I/O分配。自动分配信号组您可以单独或一次自动放置内存控制器的信号组时间您可以针对每个内存控制器的一个I/O组或一组I/O组。到自动分配信号组:

1.单击“自动分配控制器”按钮。

2.选择自动放置所有控制器或自动放置<控制器名称>。

3.在“选择要自动放置的库”对话框中,选择以下选项之一:

•选择系统:允许Vivado工具找到内存的最佳位置控制器。

•用户选择:允许您选择内存控制器的目标组。

注意:如果您没有选择足够的I/O组来容纳内存,则会出现警告控制器。

自动放置后,会出现一个确认对话框,列出已放置端口的数量。了解分配的非内存的警告端口

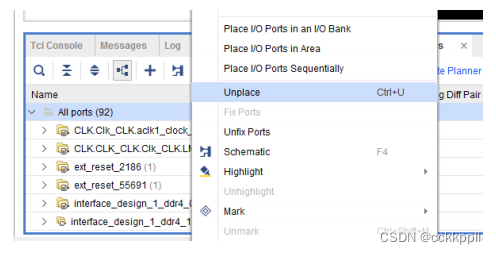

内存组/字节规划器不允许将信号组分配给以下I/O组已分配给非内存I/O端口。将显示一个黄色警告图标和工具提示指示非内存端口已分配给字节组,如下所示图形

您可以通过取消排列端口来解决此问题。在I/O端口窗口中,右键单击端口,然后选择“取消放置”,如下图所示。

不接地信号组和控制器

可以单独或一次全部取消放置内存控制器的信号组。到取消放置信号组:

1.单击“取消对内存控制器的连接端口”按钮。

2.选择取消放置所有控制器或取消放置<控制器名称>。

![[香橙派开发系列]使用蓝牙和手机进行信息的交换](https://img-blog.csdnimg.cn/img_convert/9cf17e1b539011f9b7f24231fd7bab17.png)