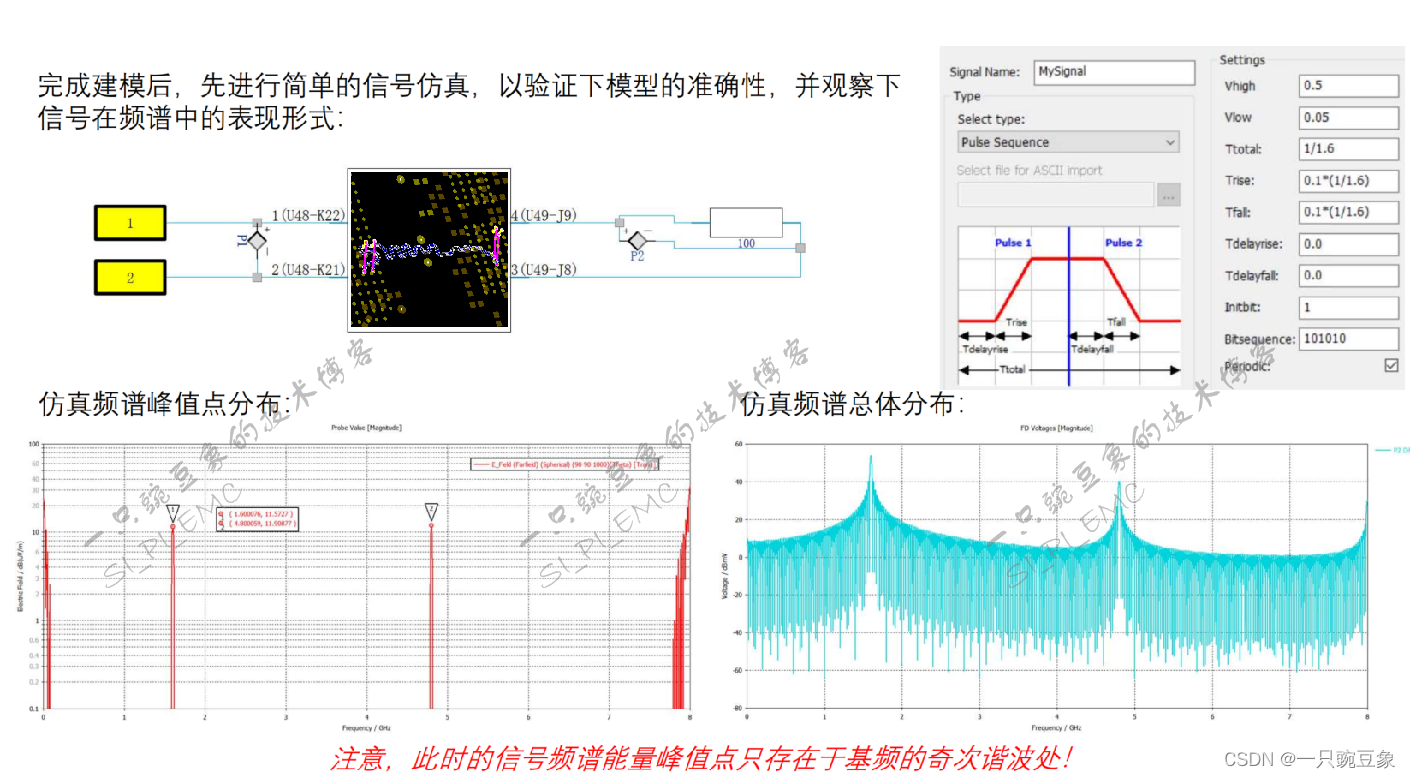

从信号与系统理论中,可以知道,对于占空比为50%的周期信号,只含有奇次谐波,实际中,时钟信号并不是理想的占空比为50%的梯形波,因此,会同时含有奇偶次谐波,一个典型的案例,DDR仿真中,如果用模拟的理想激励源,如下图所示,可以发现,频谱中只会存在基频及其奇次谐波。

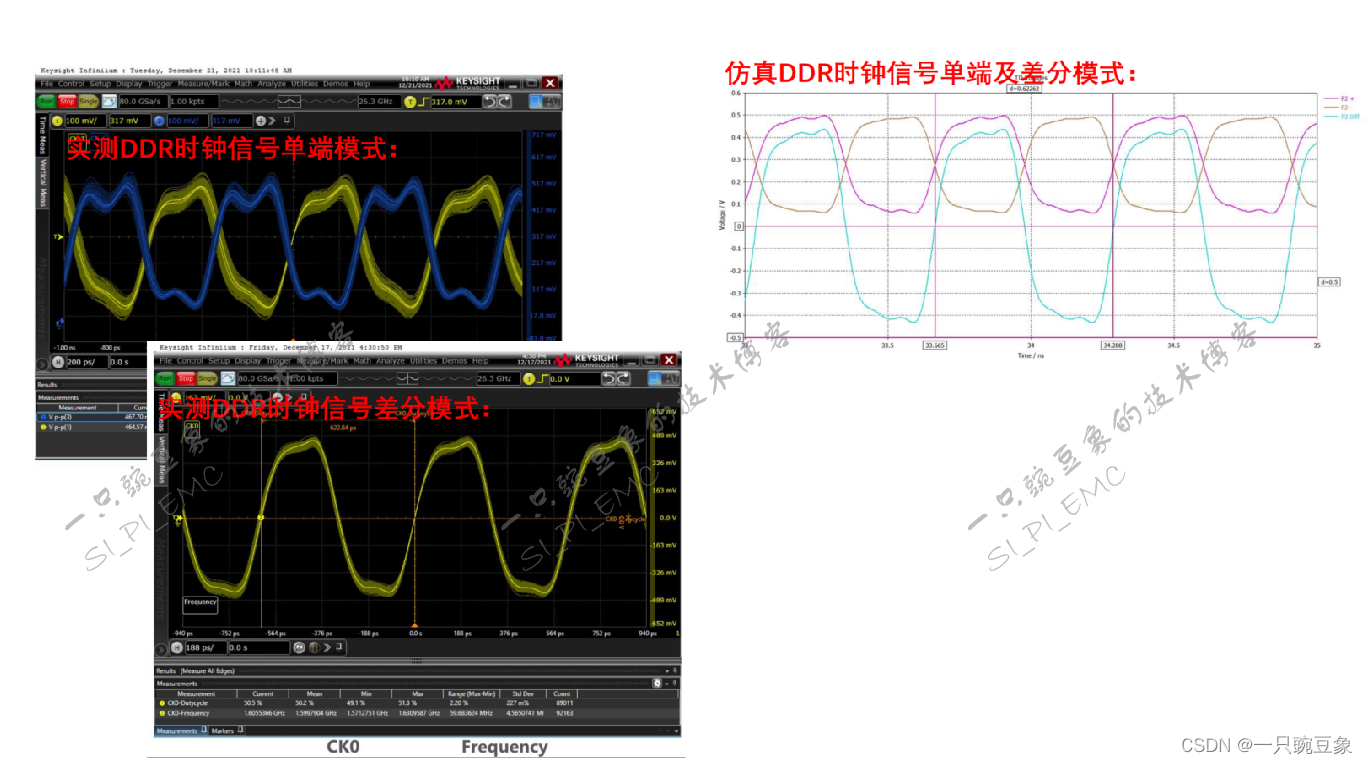

并且,利用这种自定义激励源产生的时域波形,与实测的DDR时钟信号相比,几乎看不出明显的差异,因此,这种配置用于普通的信号仿真是没有问题的。

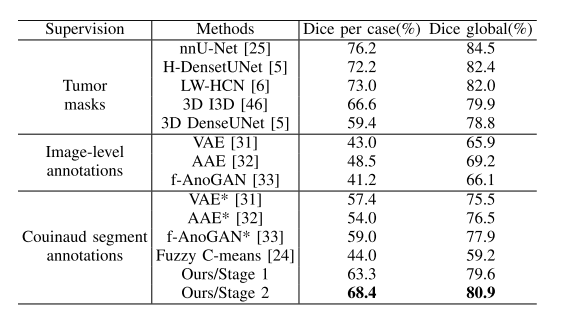

但是,当使用厂商提供的IBIS驱动文件进行仿真时,从获取的频谱图中,不仅可以看到奇次谐波,还可以看到偶次谐波,这就说明,真实的电路行为中,时钟信号的占空比是非理想化的,此时,相对于理想的梯形波,频谱已经发生了变化。