主页: 元存储博客

文章目录

- 前言

- 1. 为什么DDR5要在一个dimm里面设计两个channel?

- 2.

前言

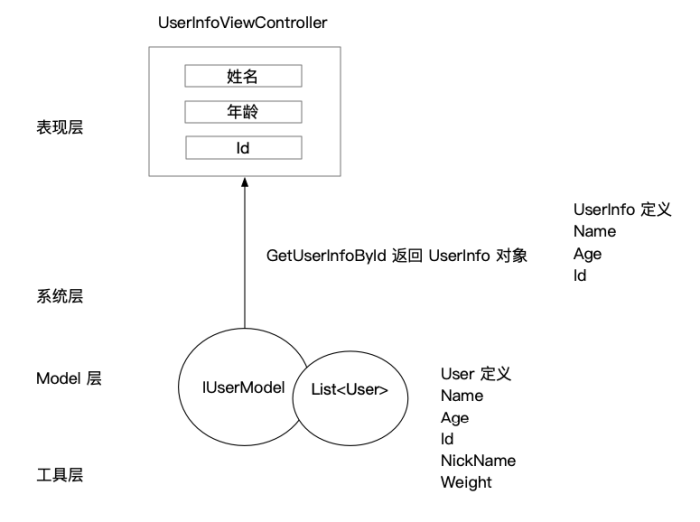

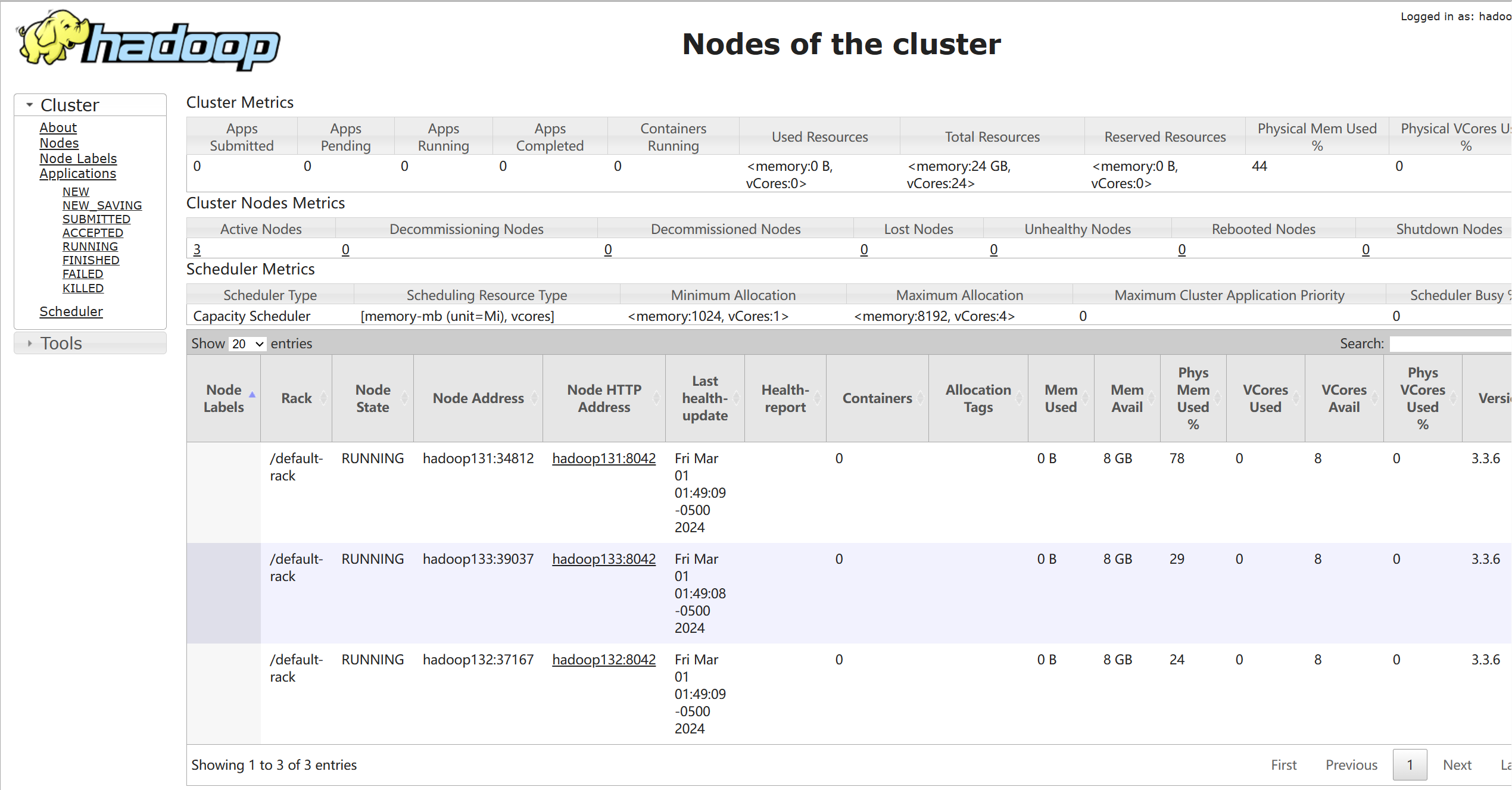

DDR5 是第 5 代双倍数据速率同步动态随机存取内存,又称 DDR5 SDRAM。DDR5 是在 2017 年由行业标准机构 JEDEC推动的,DDR5 产品 问世于 2021 年。

图片来源: 金士顿官网

DDR5 将内存模组分成两个独立的 32 位可寻址子通道,以提高内存控制器数据访问的效率并减少延迟。

1. 为什么DDR5要在一个dimm里面设计两个channel?

哪怕是上古时代的SDRAM一直到DDR4 SDRAM内存,单条内存的位宽都是64bit。 为啥 DDR5 位宽要改完 32bit

这要从 Cache(CPU 缓存) 说起。将 Cache 空间均分为很多块, 每一块称为cache line。

Cache line 是 Cache(一般是SRAM) 和内存(如 DDR5) 之间数据数据传输最小单位。 对于X86 CPU,cache line 是 64 bytes. 如果要从内存取 16 Byte, 不会只把 16 Byte 读出,而是一次读 64 Byte.

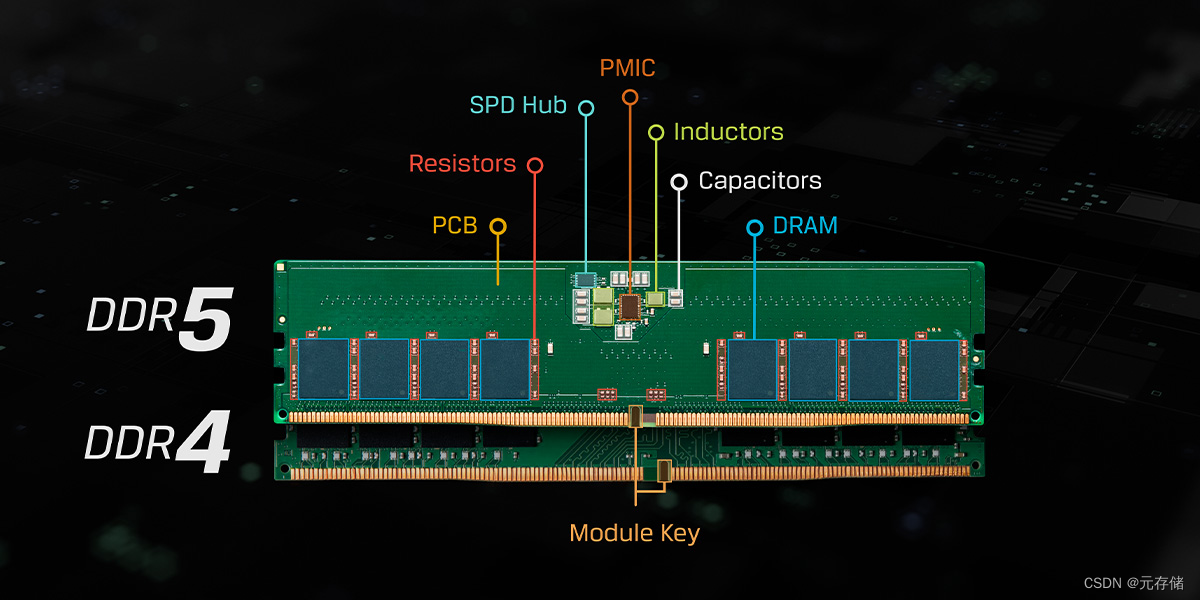

因为DDR5 burst length 是 16,如果 DDR5 位宽保持 64, 64 * 16(burst length) =1024bit = 128 Byte,超过了 CPU cache line. 那是改 Cache line 还是 DDR5 位宽呢? 如果改CPU cache line, 整个PC 的架构都要改, 从地方和上层的硬件和软件。这改动就超大了,明显是和整个生态不兼容。

DDR 引入 sub-channel, 每个 sub channel 是 32 bit, 32 * 16(burst length) = 512 bit。这样就和 COU 匹配了。每一个 sun channel 可以独立提供一个 cache line。

16n (Burst Length) 是大势所趋。DDR5必定采用16n,因为16n才导致64bit超过caches line size(64B),而linesize牵扯的东西太多不好改,所以直接改DDR5单通道位宽。就像GDDR、LPDDR一样继续降低单通道位宽。

- Sub Channel

DDR5 模组的数据带宽仍是 64 位,但将其分成两个 32 位可寻址通道可提高总体性能。对于服务器级内存 (RDIMM),向每个子通道添加了 8 位用于 ECC 支持,最终达到每个子通道 40 位或每列 80 位。双列模组包含四个 32 位子通道。

2.

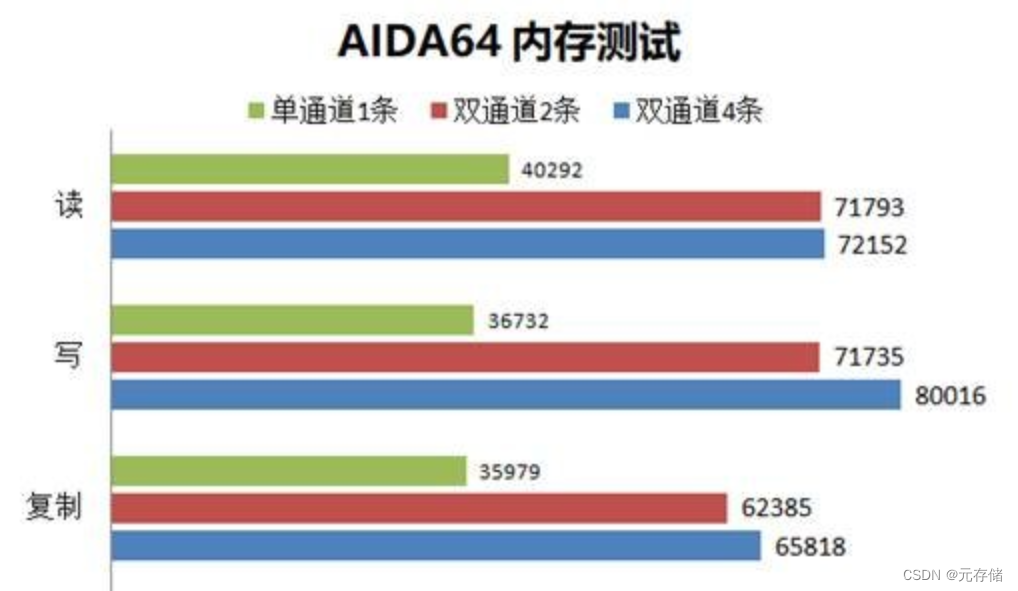

双通道对性能的提升

2.1 内存读写速度测试

图片来源: 装机天下

2.2 游戏测试

图片来源: 装机天下

CS:GO和LOL的平均FPS都达到数百帧了,差上十几二十帧基本可以无视差异的成绩。

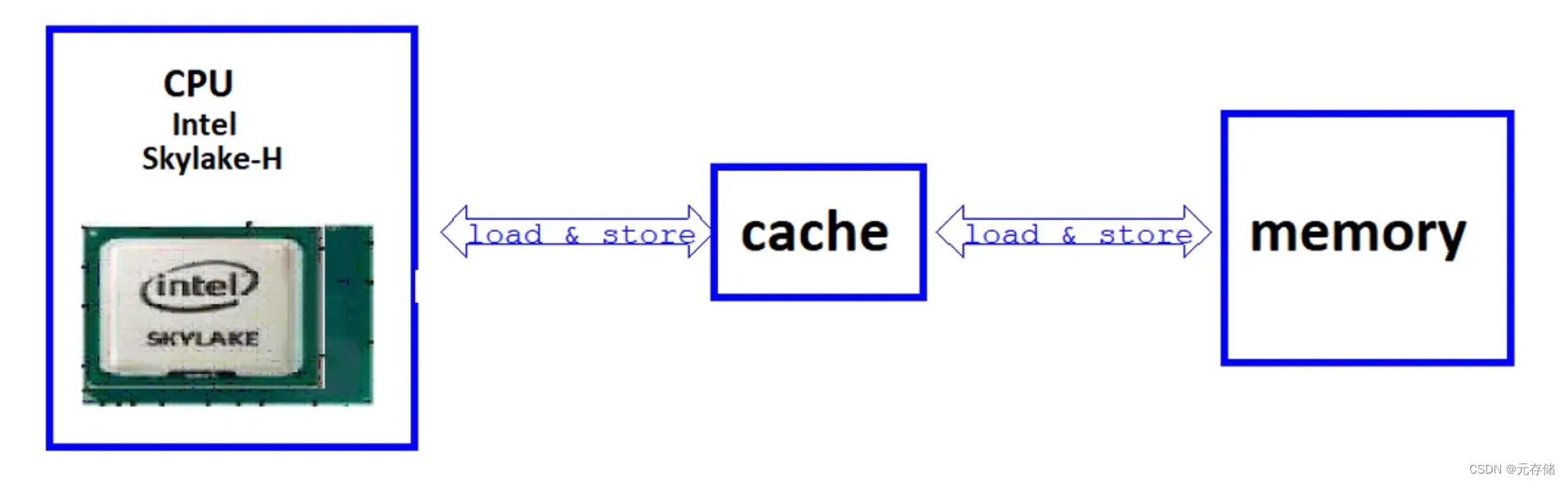

关于影响内存性能的因素中,除了频率之外,另外一个就是带宽,直接影响因素就是双通道、单通道对带宽的影响。

在DDR5内存中,传统意义的单通道内存将消失,因为单条D5内存就将位宽由64bit切割成32bit*2,换而言之就是单条D5内存自带“双通道”。不过需要明确的是,单条D5内存只会激活一个内存控制器,所以这个”双通道“和D4双通道在性能上还是有差距。

但是,如果同容量的两条DDR5内存与两条DDR4内存相比,带宽可以提高4倍之多,这对读写性能的影响非常大。

在使用独显的情况下,DDR4很有必要组双通道,两根比单根性能提升约10%~15%左右,而DDR5两根比单根提升仅2% ~ 3%,大部分情况性能是一样的。

虽然DDR5的单条双通道是走的两个32位位宽,但似乎这个特性确实对游戏起到了不小的作用。

当然核显肯定能双通就双通的。

- ddr5单条双通道的话,可以8+32g用吗?

用对称大小的双通道内存,非对称双通道会有性能损失。

参考文献

-

ddr5内存选双通道还是单通道(DDR5单通道、双通道性能对比测试)

-

为什么DDR5要在一个dimm里面设计两个channel?

声明

本文仅为学习交流目的。

文中部分文字和图片来源于互联网,列在参考的文献,但可能有遗漏。如有侵权,请告知我删除。