描述

sig_a 是 clka(300M)时钟域的一个单时钟脉冲信号(高电平持续一个时钟clka周期),请设计脉冲同步电路,将sig_a信号同步到时钟域 clkb(100M)中,产生sig_b单时钟脉冲信号(高电平持续一个时钟clkb周期)输出。请用 Verilog 代码描述。

clka时钟域脉冲之间的间隔很大,无需考虑脉冲间隔太小的问题。

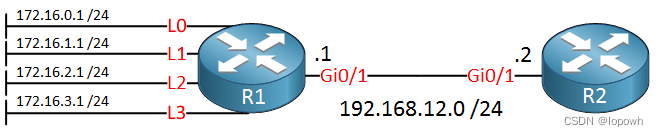

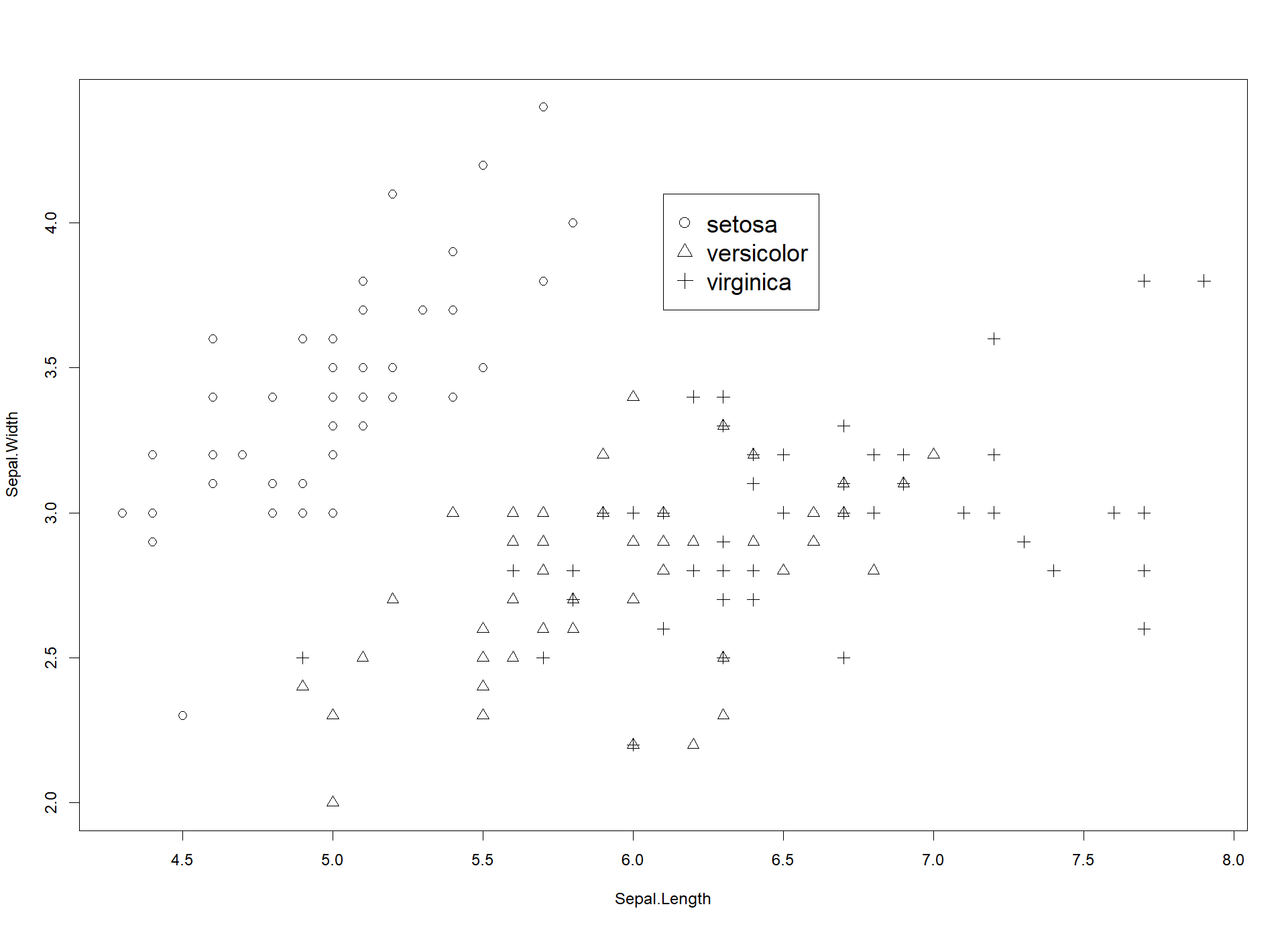

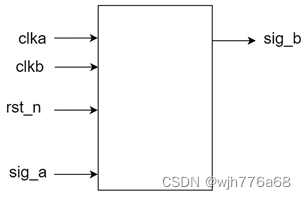

电路的接口如下图所示:

输入描述:

input clka ,

input clkb ,

input rst_n ,

input sig_a ,

输出描述:

output sig_b

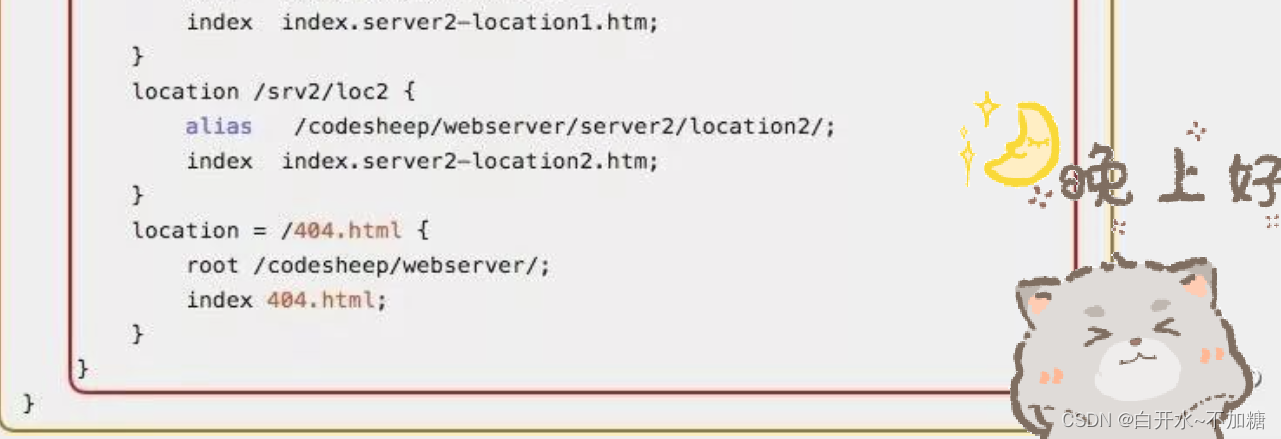

`timescale 100ps/100psmodule pulse_detect(input clka , input clkb , input rst_n ,input sig_a ,output sig_b

);reg sig_a_r = 1'b0;reg sig_a_pulse_r = 1'b0;reg sig_a_pulse_clkb_r = 1'b0, sig_a_pulse_clkb_d1_r = 1'b0,sig_a_pulse_clkb_d2_r = 1'b0;always @(posedge clka, negedge rst_n) beginif (~rst_n) beginsig_a_r <= 1'b0;end else beginsig_a_r <= sig_a;endendalways @(posedge clka, negedge rst_n) beginif (~rst_n) beginsig_a_pulse_r <= 1'b0;end else beginif (~sig_a_r & sig_a) begin // 仅同步sig_a上升沿sig_a_pulse_r <= ~sig_a_pulse_r;endendendalways @(posedge clkb, negedge rst_n) beginif (~rst_n) beginsig_a_pulse_clkb_r <= 1'b0;sig_a_pulse_clkb_d1_r <= 1'b0;sig_a_pulse_clkb_d2_r <= 1'b0;end else beginsig_a_pulse_clkb_r <= sig_a_pulse_r;sig_a_pulse_clkb_d1_r <= sig_a_pulse_clkb_r;sig_a_pulse_clkb_d2_r <= sig_a_pulse_clkb_d1_r;endendassign sig_b = sig_a_pulse_clkb_d1_r ^ sig_a_pulse_clkb_d2_r;endmodule