数字IC实践项目(9)—基于Verilog的SNN加速器

- 写在前面的话

- 项目整体框图

- 完整电路框图

- 项目简介和学习目的

- 软件环境要求

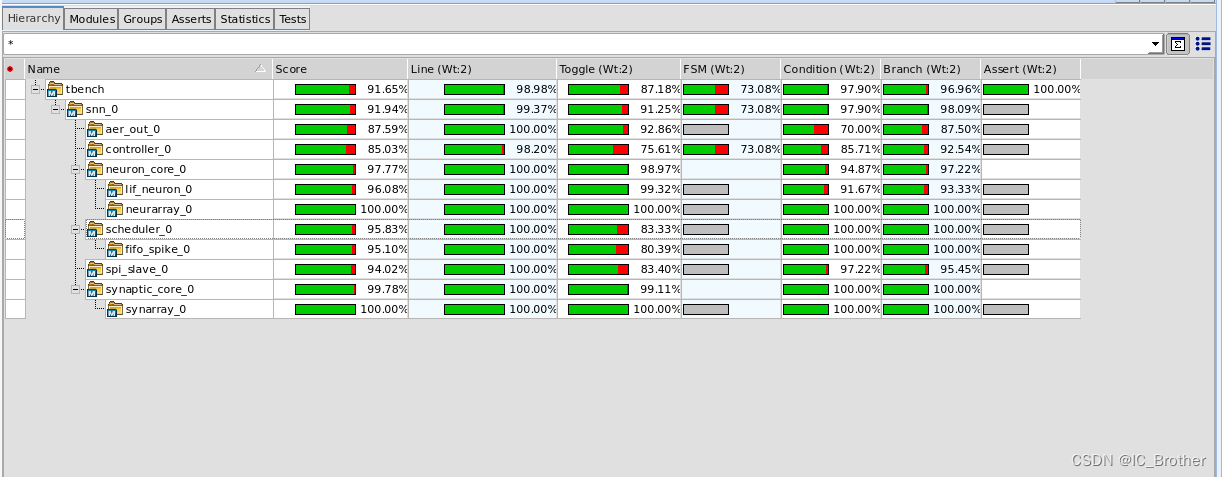

- Wave&Coverage

- Timing,Area & Power

- 总结

写在前面的话

项目介绍:

SNN硬件加速器是一种专为脉冲神经网络(Spiking Neural Networks)设计的硬件加速器。脉冲神经网络模拟了生物大脑中神经元之间的工作方式,通过离散的脉冲信号传递信息。SNN硬件加速器可以加速脉冲神经网络模型的训练和推理过程,提高神经网络的效率和能耗表现。

通过在硬件级别优化脉冲神经网络的计算,SNN硬件加速器可以实现更快的推理速度和更低的能耗,适用于诸如智能感知、边缘计算和神经形态学计算等领域。

本项目是对经典SNN的复现,是从开源的ODIN SNN处理器进行调整而来tinyODIN。是一款低成本的脉冲神经网络(SNN)处理器,简化为最简单的交叉阵列形式。tinyODIN内嵌了256个12位漏积分-放电(LIF)神经元和64k个4位突触,tinyODIN中没有现象学的Izhikevich神经元模型,也没有在线学习突触。

重要性:

SNN(脉冲神经网络)硬件加速器在人工智能和神经形态学计算方面具有重要性,其重要性体现在以下几个方面:

- 高效能耗比:SNN硬件加速器可以针对脉冲神经网络的特性进行优化,实现更高的能耗效率。由于神经元的活动是以脉冲的形式进行传递,因此专门针对这种模式设计的硬件可以显著降低能耗,提高能效比。

- 实时处理能力:脉冲神经网络通常用于处理实时感知和决策任务,例如视觉处理和运动控制。SNN硬件加速器的并行计算和快速响应特性,使其能够满足实时处理的需求,对于嵌入式系统和边缘计算等领域尤为重要。

- 神经形态学研究:对于神经形态学和神经科学研究来说,SNN硬件加速器提供了一种高度可定制和可调节的平台,有助于模拟大规模神经网络的活动,加深对大脑功能的理解,并促进人工智能与生物学的交叉研究。

对于找工作的帮助:

- 就业竞争力增强: SNN硬件加速器是人工智能领域的前沿技术之一,掌握其设计将使数字IC专业学生在求职市场上具备更强的竞争力。公司在人工智能芯片设计、边缘计算、物联网等领域都需要数字IC工程师具备相关技能,因此拥有SNN硬件加速器的设计经验将使学生更容易获得相关职位。

- 加深理论与实践结合: SNN硬件加速器的设计涉及到神经形态学计算原理、硬件架构优化等多个领域的知识。通过掌握SNN硬件加速器的设计,学生能够将所学的理论知识与实践相结合,加深对数字集成电路设计和人工智能的理解,并且能够在实际项目中应用所学的知识。

- 开拓创新思维: SNN硬件加速器的设计是一个创新的领域,需要工程师具备创新思维和解决问题的能力。掌握SNN硬件加速器的设计将培养学生的创新能力,激发他们在数字IC领域中提出新的设计理念和解决方案的能力,这对于找工作时的项目经验展示和职业发展都非常有帮助。

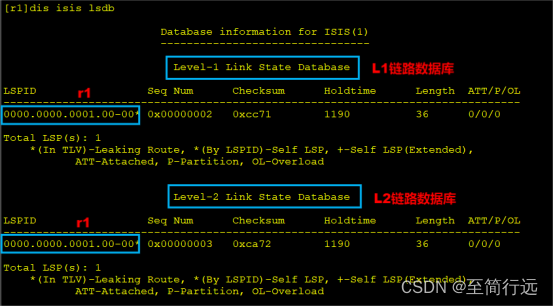

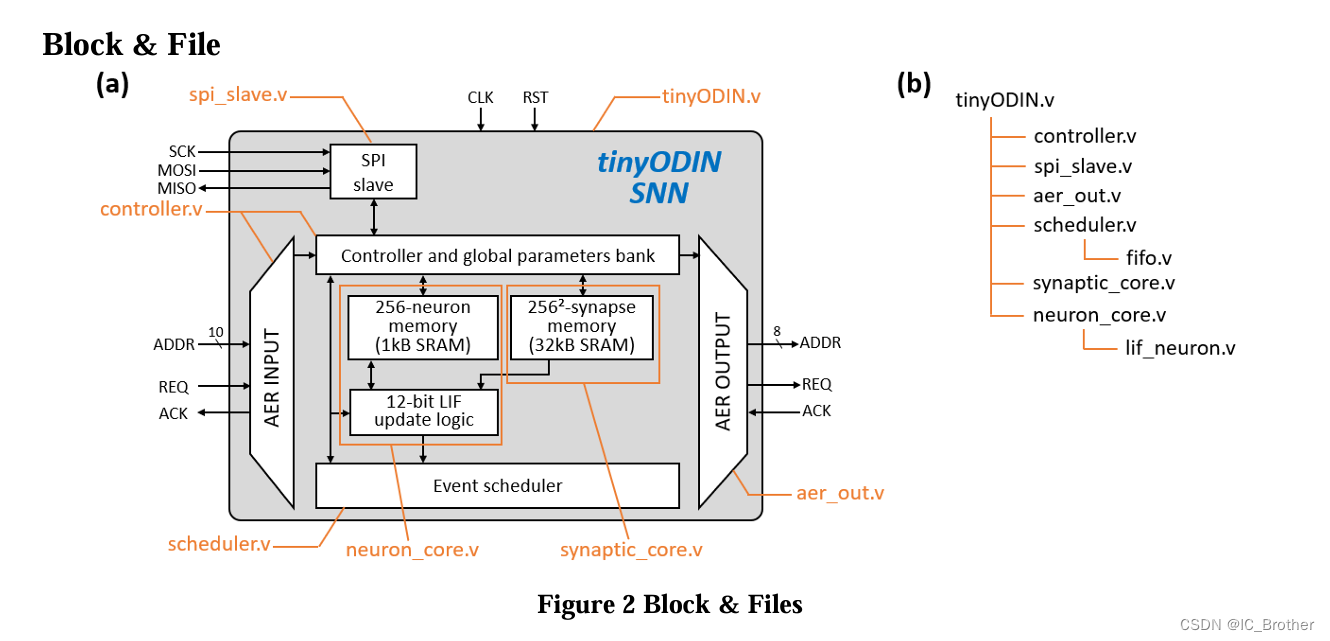

项目整体框图

项目整体框图如下,以SNN硬件突触和片上SRAM为核心,搭配SPI外围模块完成权重配置和事件输入,处理器采用了时间多路复用的方式,实现了一个包含256个神经元和64k个突触的交叉架构。

每个神经元和突触的状态和参数分别存储在1 kB 和32 kB的单口同步存储器中。

- 控制器负责神经元和突触更新逻辑的时间多路复用

- 调度器则处理来自输入AER总线的内部和外部事件

完整电路框图

整个电路结构如下,主要分为六个部分,分别为:

- aer_out:事件输出端口,用于处理地址和SNN突触触发结果。

- spi_slave:spi配置端口,用于设置全局寄存器、SNN突触权重以及事件配置等命令,支持双向读写。

- controller:SNN内部主控制模块。

- scheduler:事件分发模块,用于处理Bus数据和内部事件。

- synaptic_core:SNN突触阵列,存储突触状态,分时复用,降低SNN突触例化数量。

- neuron_core:LIF模型

项目难度:⭐⭐⭐⭐⭐

项目推荐度:⭐⭐⭐⭐

项目推荐天数:14~21天

项目简介和学习目的

基于开源项目完成rtl前仿到icc2布局,感兴趣的同学可以私信我,整个项目还有很多可以优化改进的地方,大家可以在完成学习的基础上进行改进,希望可以帮助大家更好的完成求职!

软件环境要求

整个项目对于初学者要求较高,完成复现需要花费较长的时间搭建软件环境,这里建议大家按需完成学习,循序渐进,可以从神经网络、SNN硬件加速器、RTL代码以及综合等方面进行展开。

要求的软件和EDA环境:

(1)操作系统要求:

Centos

(2)EDA 软件要求:

VCS2018,DC2018,ICC2 2018

(3)硬件要求:

电脑运行内存 >= 16Gb(便于综合)

项目学习目的:

(1)熟练掌握复杂项目的工程管理;

(2)熟悉 Verilog HDL仿真、综合工具以及了解数字IC设计工具及流程;

(3)学习SNN网络的基本结构和基础原理;

(4)学习SNN硬件加速器;

(5)熟练掌握Verilog语法和验证方法;

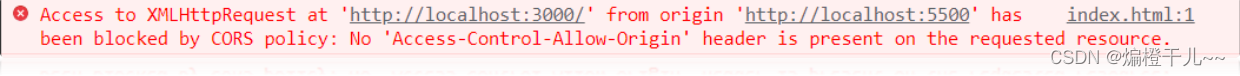

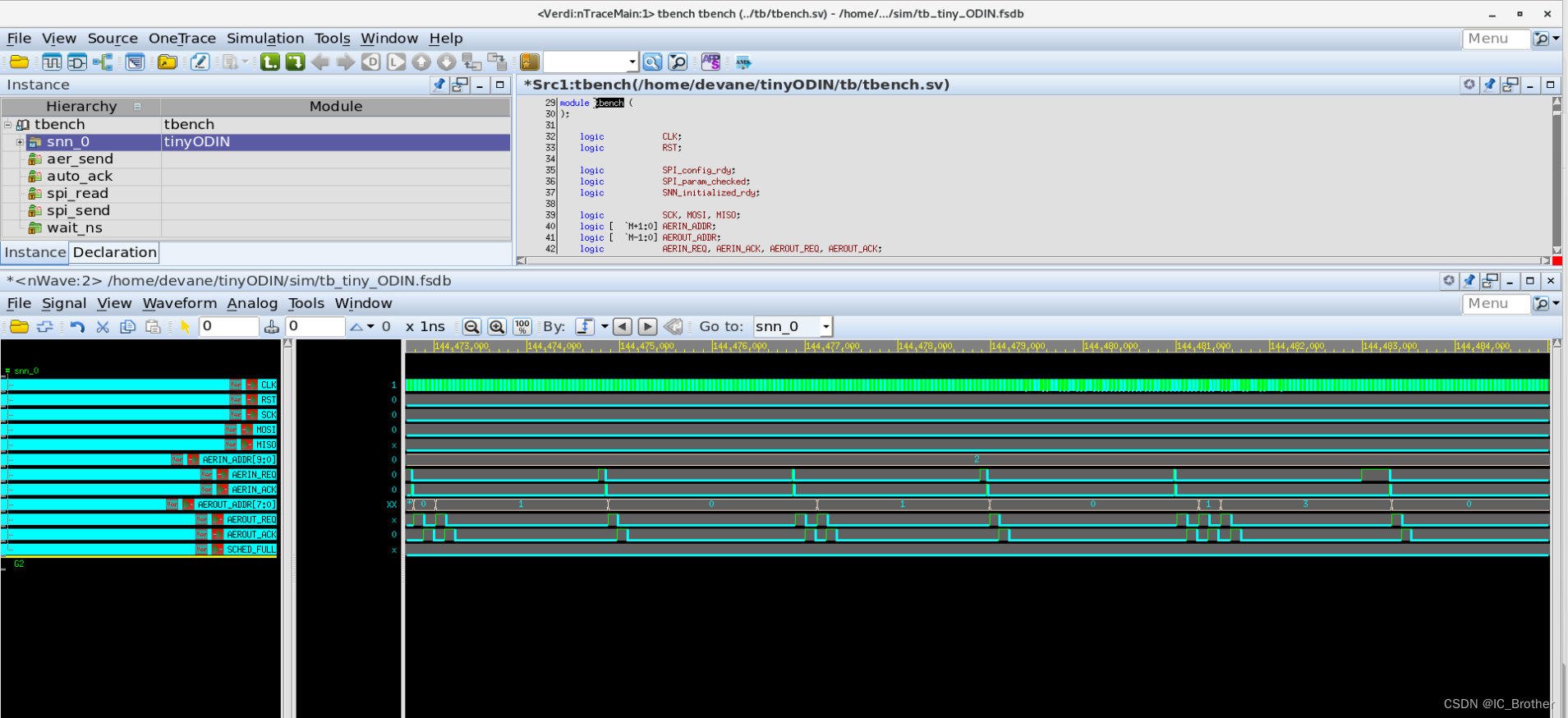

Wave&Coverage

配置SNN突触权重后,通过SPI完成事件输入,在Aerout ACk上可以采样到LIF单元对应状态。

整个项目的Coverage如下:

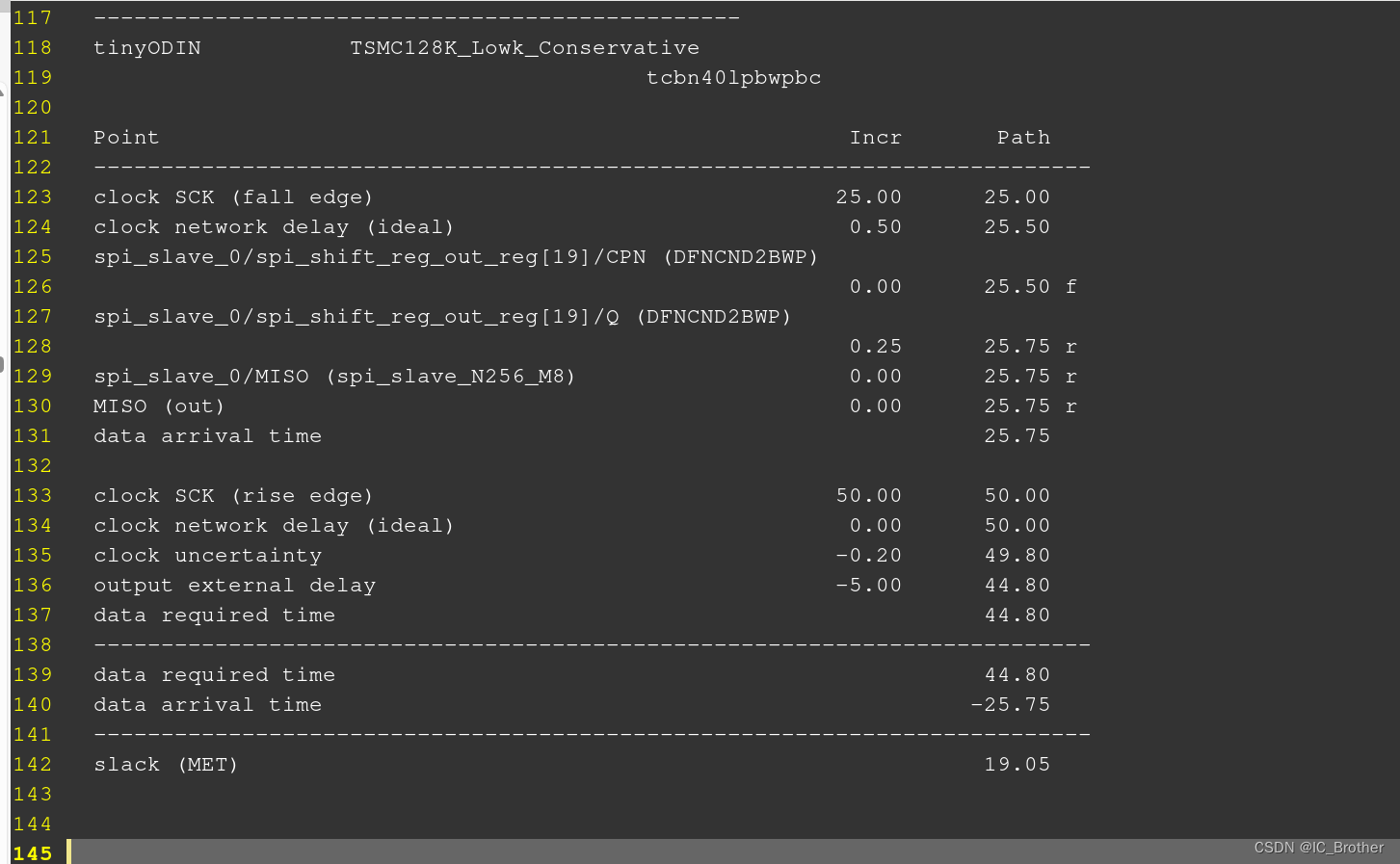

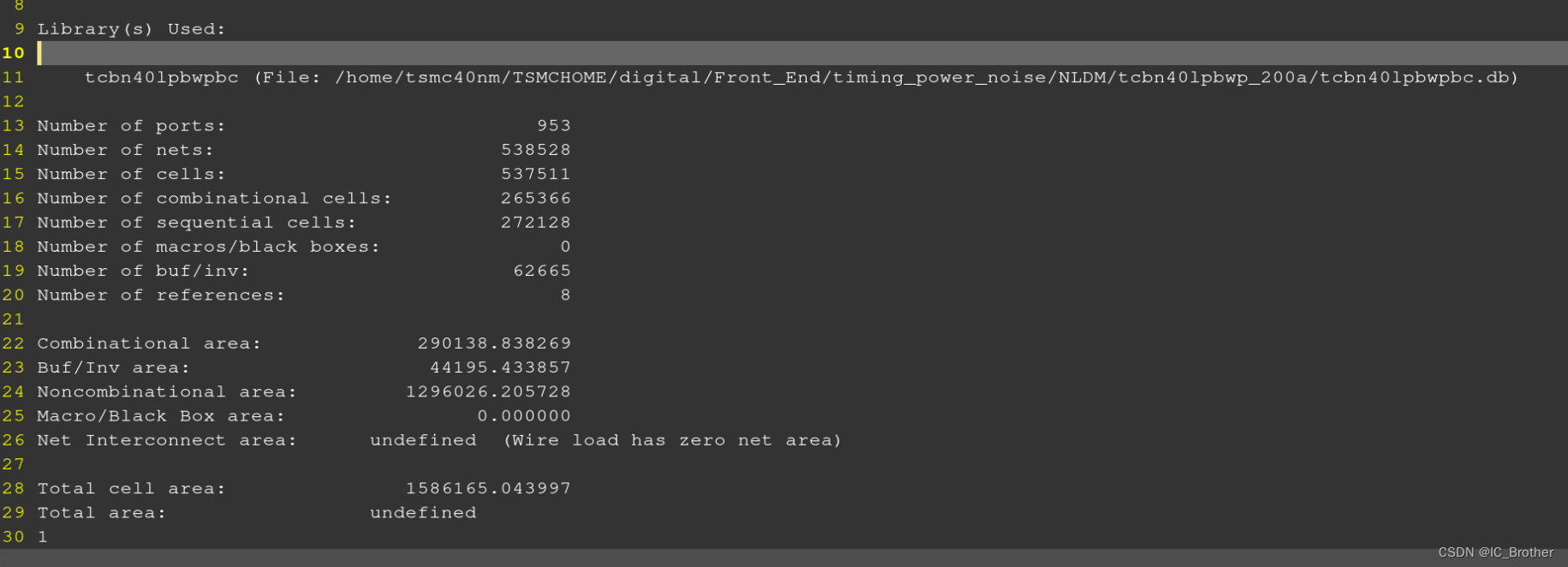

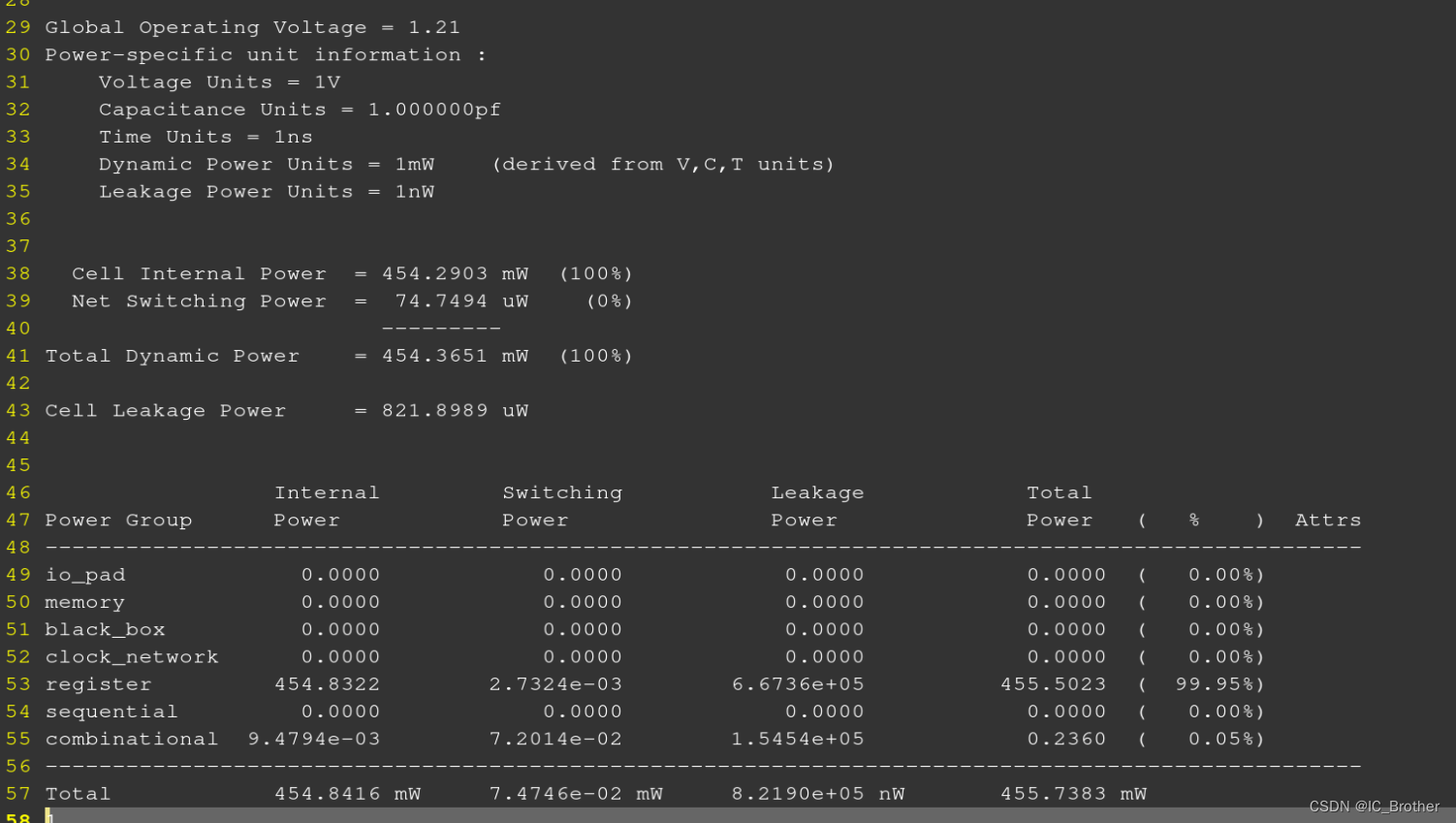

Timing,Area & Power

基于tsmc 40nm工艺完成综合,以下为相关报告。

Timing:

Area:

power:

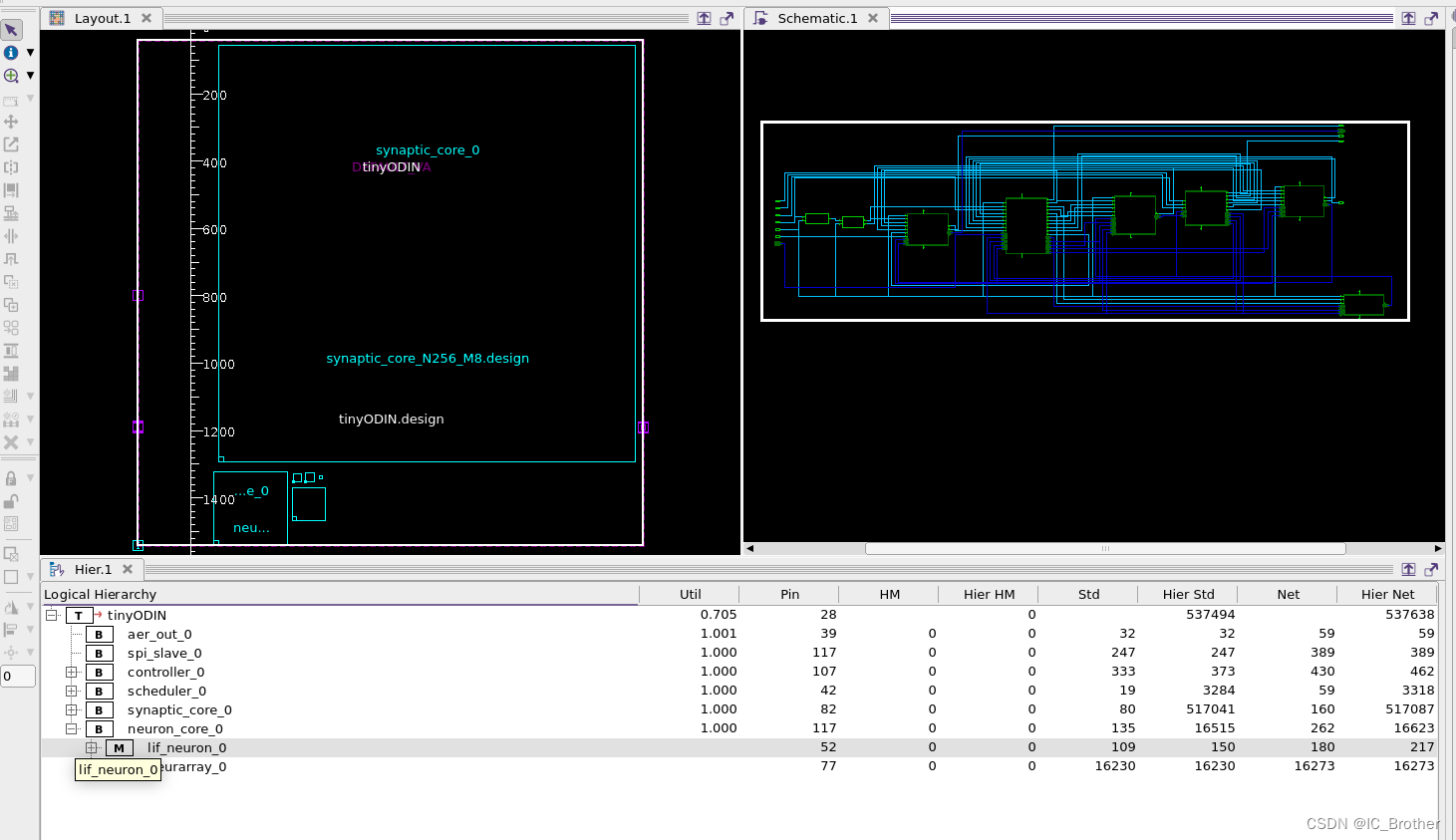

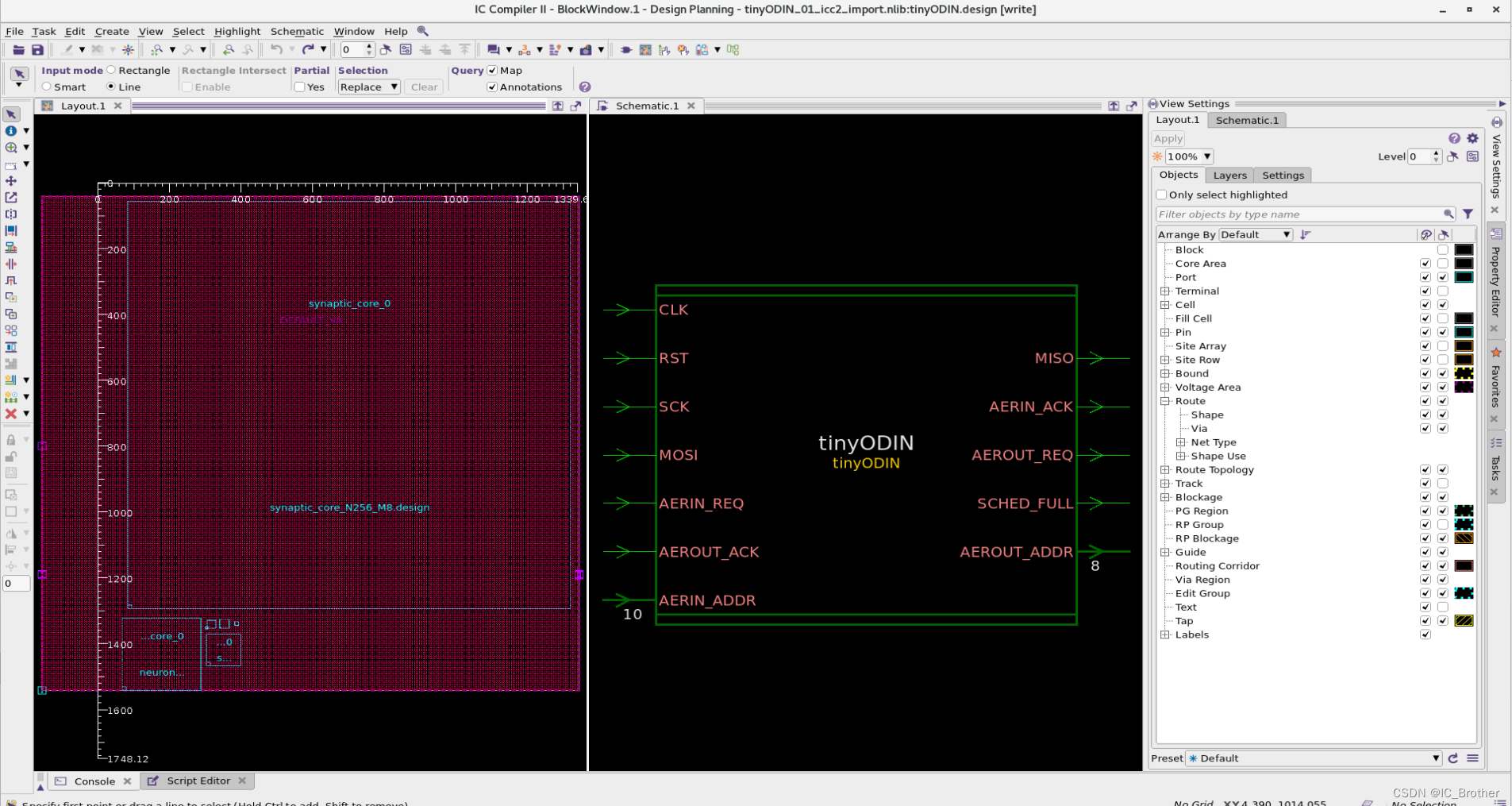

icc2布局如下:

ps:手动粗糙布局,也没有对应SRAM的IP,图一乐。

总结

项目涵盖了SNN硬件加速器的基础理论,Verilog实现和仿真和测试所需脚本和环境配置。

需要搭建完整的软件和硬件环境,相对先前列出的开源和初级项目来说,整体难度稍高,适合作为前期的提升项目。