Q:在上篇的异步复位D触发器中添加一个使能信号来实现带使能功能的异步复位D触发器。

A:只要复位信号为高电平(RST=1)且CLK为时钟上升沿, 如果使能信号也为高电平(EN=1),输入数据才会被存储。

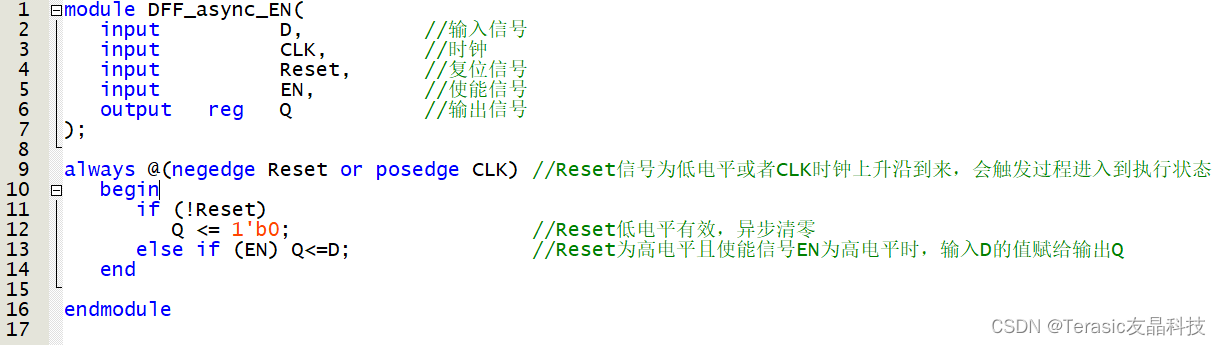

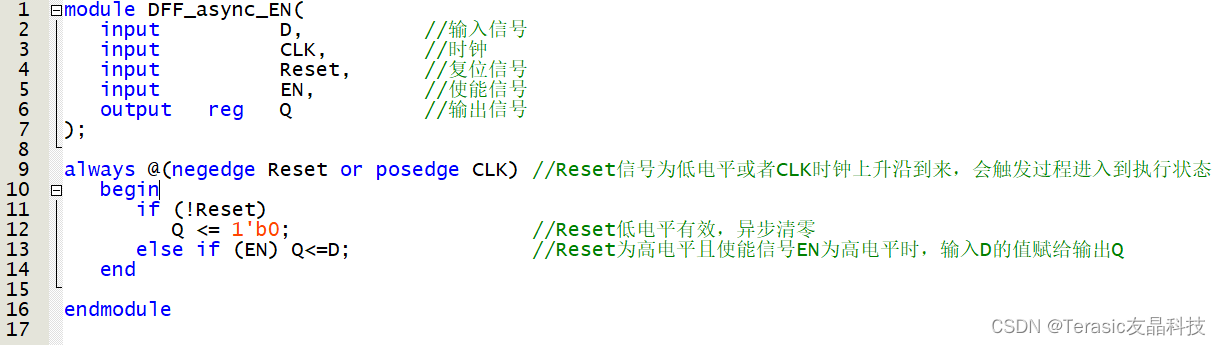

带使能功能的异步复位D触发器Verilog代码:

使用DE2-115开发板的SW[0]作为数据输入D,KEY[0]作为时钟输入CLK,KEY[1]作为异步复位信号,SW[1]作为使能信号,LEDR0显示触发器的输出值Q。ModelSim仿真结果:

Q:在上篇的异步复位D触发器中添加一个使能信号来实现带使能功能的异步复位D触发器。

A:只要复位信号为高电平(RST=1)且CLK为时钟上升沿, 如果使能信号也为高电平(EN=1),输入数据才会被存储。

带使能功能的异步复位D触发器Verilog代码:

使用DE2-115开发板的SW[0]作为数据输入D,KEY[0]作为时钟输入CLK,KEY[1]作为异步复位信号,SW[1]作为使能信号,LEDR0显示触发器的输出值Q。ModelSim仿真结果:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.rhkb.cn/news/294075.html

如若内容造成侵权/违法违规/事实不符,请联系长河编程网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!