SV:SystemVerilog

- 开启SV之路

数据类型

內建数据类型

-

四状态与双状态 :

- 四状态指0、1、X、Z,包括logic、integer、 reg、 wire。

- 双状态指0、1,包括bit、byte、 shortint、int、longint。

-

有符号与无符号 :

- 有符号:byte、shortint、int、longint、integer。

- 无符号:bit、logic、reg、wire。

-

关于数据类型使用的几个注意点 :

-

SV中虽然支持reg和wire,但对于 验证平台要尽量使用logic ,并且建议采样RTL信号时变量要使用logic类型。

-

实际工作中 使用最多的是logic和bit ,一般 需要计数和比较大小时会使用byte或int 。

-

尽量 避免两种不同数据类型变量进行操作 ,包括 有无符号、四状态双状态、不同位宽 ,如必须进行操作,请先转换为同一类型。

-

-

关于数据类型转换的几个注意点 :

- 四状态转换为双状态时, x和z转换为0 。

- 多位数据赋值给少位数据,则 高位被截取忽略 ;少位数据赋值给多位数据,双状态类型的 高位赋值为0 ,四状态类型的 高位赋值为x 。(以上指的是无符号类型)

- 有符号变量转无符号变量,直接赋值的话会将 原始比特数据 赋给无符号变量,但其原符号位失去含义;使用转换语句转换的话,会将有符号变量 取模 赋值给无符号变量。

- 总之,还是尽量避免数据类型间的转换,数据类型间的转换是容易出错的地方,需要格外注意。

-

数据类型转换操作 :

//静态转换(不对转换值进行检查):

unsigned_data = unsigned'(signed_data);

int_data = int'(real_data);

real_data = real'(int_data);//动态转换(仿真时对转换值进行检查,转换失败会报告):

//$cast(tgt, src);

$cast(unsigned_data, signed_data);//静态和动态转换都属于显示转换,不借助操作符的转换称为隐式转换

logic data0;

bit data1;

data1 = data0;

定宽数组

- 数组声明 :

//变量左侧为矢量宽度,右侧为维度,且从左至右代表维度从高到低//二维数组(习惯上左右顺序是从低到高,这对初始化很重要)

int data_a[0:15]; // 16个整数[0]...[15]

int data_a[16]; // 紧凑型声明//多维数组(左边为高维度)

int data_a[0:7] [0:3];

int data_a[8] [4]; // 紧凑的多维数组声明

int data_a[7][3] = 1; // 为最后一个元素赋值

- 数组的初始化和赋值 :

int data_a[4] = '{0,1,2,3}; //data_a[0]为0 ... data_a[3]为3

int data_a[0:3] = '{0,1,2,3}; //data_a[0]为0 ... data_a[3]为3

int data_a[4] = '{4{1}}; //全赋值为1

int data_a[4] = '{5,default:-1}; //data_a[0]为5,其他为-1

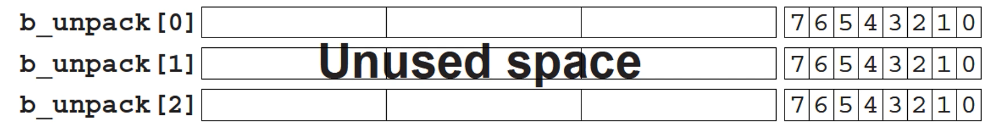

- 存储空间 :

bit [3][7:0] b_pack;

bit [7:0] b_unpack [3];

logic [3][7:0] b_pack;

logic [7:0] b_unpack [3];//变量左侧代表矢量宽度,右侧代表数组维度,也可以称为数组的合并与非合并,以上都可以代表24bit数据容量。

//二值逻辑bit声明,每bit位占用1bit空间,第一种声明占用1WORD空间,3x8bit,第二种声明占用3个WORD空间,3WORD x 1x8bit;

//四值逻辑logic声明,每bit位占用2bit空间,第一种声明占用2WORD空间,3x16bit,第二种声明占用3WORD空间,3WORD x 1x16bit。

//所以,在合适的时候选用合并数组,能够节省存储空间。(软件仿真时计算机空间占用都是以word为单位的)

- 数组操作之for和foreach循环 :

bit [31:0] src[5];

bit [31:0] dst[5];for(int i=0; i<$size(src); i++)src[i] = i;foreach (dst[j])dst[j] = src[j] * 2;

//$size(src)是获取最高维度变量个数,也可以指定维度$size(src,1),其中1代表最高,2次之...

//foreach语句会遍历数组变量,这也是最推荐的使用方法,多维度遍历可以使用foreach(dst[i,j])。

- 数组操作之复制和比较 :

bit [31:0] src[5] = '{0,1,2,3,4};

bit [31:0] dst[5] = '{4,3,2,1,0};

if(src == dst) $display("src == dst"); //比较数组dst = src; //数组复制src[0] = 5; //修改数组中某元素//赋值可以直接使用赋值符号“=”;

//直接进行数组的复制;

//比较,也可以使用“==”或“!=”来比较,不过结果仅限于内容相同或不相同。

动态数组

- 定宽数组类型宽度编译时已经确定,若在程序运行时确定数组宽度就要使用 动态数组 。

- 动态数组特点就是仿真运行时灵活调节数组的大小,也就是存储量。

- 动态数组开始时使用“[]”来声明,此时数组为空,其后使用“new[]”来分配空间,方括号中传递数组宽度。

- 调用“new[]”时也可以将数组名一并传递,将已有数组的值复制到新的数组中。

int dyn[];

int d2[]; //声明动态数组initial begindyn = new[5]; //分配5个元素foreach(dyn[j]) dyn[j] = j; //对元素初始化d2 = dyn; //复制动态数组,d2初始元素个数为零,复制后元素个数为5,且dyn和d2各自独立d2[0] = 5; //修改元素值,此时dyn[0]仍为0,d2[0]为5dyn = new[20](dyn); //分配20个数值并进行复制,也就是dyn初始值5个元素复制给了新的dyn低5个元素,高15个元素为0.dyn = new[100]; //重新分配100个数值,而旧值不复存在dyn.delete(); //删除所有元素

end

队列

- 队列结合了链表和数组的优点,可以在任何地方添加和删除元素,并且通过索引实现对任一元素的访问。

- 队列的声明是使用美元符号的下标:[ ] ,队列元素标号从 0 到 ],队列元素标号从0到 ],队列元素标号从0到。

- 队列不需要new[]去创建空间,只需要使用队列的方法为其增减元素,队列初始空间为零。

- 队列的简单使用是通过 push_back()和pop_front() 的结合来实现FIFO的用法。

int j = 1;

int q2[$] = {3,4};

int q[$] = {0,2,5}; //队列的赋值不需要单引号initial beginq.insert(1, j); //{0,1,2,5} 在1位置插入jq.insert(3, q2); //{0,1,2,3,4,5} 在3位置中插入队列q2q.delete(1); //{0,2,3,4,5} 删除队列中1位置元素//下列操作才是队列中最常用方法q.push_front(6); //{6,0,2,3,4,5} 在队列头部插入j = q.pop_back(); //{6,0,2,3,4} 在队列尾部弹出q.push_back(8); //{6,0,2,3,4,8} 在队列尾部插入j = q.pop_front(); //{0,2,3,4,8} 在队列头部弹出foreach(q[j])$display(q[j]); //打印整个队列q.delete(); //删除整个队列

end

关联数组

- 如果需要一个超大容量存储空间,而有相当部分数据不会被存储和访问,不管使用定宽数组还是动态数组,都会造成存储的浪费,这时候需要使用关联数组。

- 关联数组可以保存稀疏矩阵元素,当你对一个非常大的地址空间进行寻址时,该数组 只为写入的元素分配空间 ,所以关联数组需要的空间远小于定宽或动态数组。

- 此外关联数组的灵活应用,在其他高级语言中都有类似的存储结构,比如Perl语言中称为哈希(Hash),Python中称为词典(Dictionary),可以灵活赋予key和value。

bit [63:0] assoc[int]; //声明关联数组,关联数组中[]内声明数据类型,也就是index类型

int index = 1;repeat(64) begin //对稀疏分布的元素初始化assoc[index] = index;index = index <<1; //1 2 4 8 16 ......

endforeach(assoc[i]) //使用foreach变量关联数组,注意:并不一定按index大小顺序依次执行(可以使用sort排序)$display("assoc[%d] = %h", i, assoc[i]);//找到并删除第一个元素,使用if(assoc.first(index)) 可以判断数组是否为空

assoc.first(index); //将assoc第一个索引值赋给index

assoc.delete(index); //删除assoc的index索引元素

结构体

- sv中可以使用struct语句创建结构,与c语言类似。

- sv中struct功能较少,只可以定义一个 数据的集合 ,也就是将若干相关变量组合到一个struct结构定义中。

- 通过 使用typedef和struct,可以定义新的数据类型 ,可利用新的数据类型声明变量。

//非合并结构

typedef struct {bit[7:0] r;bit[7:0] g;bit[7:0] b;

} pixel_str; //使用typedef和struct创建新的数据类型 pixel_strpixel_str my_pixel; //使用新的数据类型声明变量

my_pixel = '{8'h10, 8'h20, 8'h30}; //结构体赋值,此时赋值与声明时一一对应//合并结构

typedef struct {bit[7:0] r,bit[7:0] g,bit[7:0] b;

} pixel_str; //使用typedef和struct创建新的数据类型 pixel_strpixel_str my_pixel; //使用新的数据类型声明变量

my_pixel = {8'h10, 8'h20, 8'h30}; //结构体赋值,此时赋值与声明时一一对应

- 关于赋值时什么时候使用单引号:

- 合并型存储的不需要使用单引号,就好比数据的拼接,队列是合并型存储的。

- 非合并型存储需要使用单引号,如数组和结构体。

枚举类型

- 规范的操作码和指令有利于代码的编写和维护,如ADD、WRITE、IDEL等。

- 枚举类型enum经常 和typedef搭配使用 ,由此便于用户自定义枚举类型的共享使用。

- 枚举类型 保证避免一些非期望值的出现 ,增加代码可维护性和降低设计风险。

typedef enum {INIT, DECODE, IDLE} fsmstate_e; //声明枚举类型和自定义数据类型

fsmstate_e pstate, nstate; //通过自定义枚举数据类型 声明变量case(pstate) //枚举类型主要应用于状态机IDEL: nstate = INIT;INIT: nstate = DECODE;default: nstate = IDLE;

endcase$display("Next state is %s", nstate.name()); //显示状态名

字符串

- verilog语言中是不存在字符串的,而sv中添加了字符串string类型。

- 所有相关的字符串处理,都使用string来保存和处理。

- 字符串处理相关的格式化函数可以 使用 s f o r m a t f ( ) ,如果只是打印输出,可以直接使用 sformatf() ,如果只是打印输出,可以直接使用 sformatf(),如果只是打印输出,可以直接使用display()。

string s1, s2; //声明字符串,此时为空。

int i1, i2;initial begini1 = 2005;s1.itoa(i); // integer converted to strings2 = "IEEE";$display(s2.tolower()); //显示 ieee (转小写)s2 = {s2, "-P1800"}; //字符串拼接, "IEEE-P1800"s2 = $sformatf("%s%s", s1, "-P1800"); //字符串拼接, "IEEE-P1800"i2 = s2.len(); //获取字符串长度$display("@%t: %s", $time, $sformatf("%s %d", s2, 42)); //$sformatf返回字符串

end

过程块

- 过程块有两种:initial和always。

- initial是 不可综合的 ,为验证而生,always是 可综合的 ,代表硬件电路。

- always是 硬件行为 ,可综合,使用时需要 区分时序电路描述和组合电路描述 。

- initial是 软件行为 , 块内语句 顺序执行,且只执行一次 。

- initial块和always块之间,以及不同initial块,不同always块,在 仿真一开始都是同时执行 的。

- 在verilog时代,所有的测试都放在initial块中,并且为了便于统一管理,建议 放在同一个initial块中 。

- module、interface可视为 硬件域 ,program、class可视为 软件域 ,区分硬件域和软件域对理解initial和always很有帮助。

- initial块可以放在module、interface和program中;always块只能放在module、interface中。

- 对于过程块,使用 begin…end 将其作用域包住,对于控制语句和循环语句,同样适用。

-

module 和 interface:这些是Verilog中用于描述硬件行为的构造。module通常用于描述硬件组件,如处理器、内存或其他功能单元,而interface则用于定义组件之间的通信协议。这些都属于硬件域,因为它们直接对应于硬件电路的行为。

-

program 和 class:这些是SystemVerilog(Verilog的一个超集)中引入的构造,主要用于描述软件行为。program通常用于定义测试程序,而class则用于创建可重用的对象。这些都属于软件域,因为它们更多地关注于描述仿真过程中的控制和数据流。

-

initial块:如上所述,initial块中的代码仅在仿真开始时执行一次。在硬件测试中,initial块通常用于初始化测试环境、生成激励信号、以及检查响应是否符合预期。由于测试通常需要在仿真开始时立即进行,并且只执行一次,因此将测试代码放在initial块中是合适的。

-

always块:与initial块不同,always块中的代码会在仿真期间不断重复执行。**它通常用于描述硬件的周期性行为,如时钟信号、中断处理等。**在软件仿真中,always块也可以用于实现循环和条件逻辑。

举个例子:

- 硬件域示例

假设我们有一个简单的Verilog module,描述了一个数字加法器:

module adder( input [7:0] a, b, output [7:0] sum

); assign sum = a + b;

endmodule

这个module属于硬件域,因为它直接对应于一个加法器的硬件实现。

- 软件域示例

在SystemVerilog中,我们可以使用program和class来编写测试程序:

program test_adder; adder uut; // 实例化加法器模块 initial begin // 初始化测试 uut.a = 8'h12; uut.b = 8'h34; // 等待一段时间让加法器完成计算 #10; // 检查结果 if (uut.sum == 8'h46) begin $display("Test passed!"); end else begin $display("Test failed!"); end // 更多测试... end

endprogram

在这个例子中,program属于软件域,因为它用于描述测试程序的行为。我们使用initial块来初始化测试环境、生成激励信号,并检查结果是否符合预期。

综上所述,将测试代码放在initial块中,尤其是在Verilog时代,是一种常见的做法,因为它符合测试在仿真开始时立即执行的需求。

而随着SystemVerilog的引入,我们有更多的构造(如program和class)来支持更复杂的软件仿真和测试场景。

方法(函数与任务)

函数function

- 可以在参数列表指定输入参数(input)、输出参数(output)、输入输出参数(inout)或者引用参数(ref),如果不指明默认为input。

- 可以有返回值,也可以无返回值(void)。

- 函数其他属性:

- 默认数据类型为logic。

- 数组可以作为形式参数传递。

- function可以返回或不返回结果,返回结果需要使用关键字return,不返回需要声明为void function。

- 只有数据变量可以在形式参数列表被声明为ref类型,而线网类型则不能声明为ref类型。

- 使用ref时,有时为了保护参数对象只被读取不被修改,可以通过const的方式限定ref声明的参数。

- 在声明参数时,可以设置默认值(input a=10),同时如果在调用时省略参数的传递,则函数中使用默认值。

function int double_f1(input int a);return 2*a;

endfunctionfunction void double_f2(constraint ref int a, ref int b);b = 2*a;

endfunctioninitial beginint a;int b;double_f2(a, b);$display("double of %0d is %0d", 10, double_f1(10));$display("double of %0d is %0d", 10, b);

end

任务task

任务相比函数更加灵活,且有以下不同点:

- task无法通过return返回结果(也无需加void),只能通过input、output、inout或ref的参数来返回。

- task内 可以使用耗时语句 ,而function不能。常见的耗时语句如: @event、wait event、#delay 等。

task double_t1(input [31:0] a, output [31:0] b); //不指明方向则默认为inputb = 2*a;

endtasktask double_t2(constraint ref int a, ref int b);b = 2*a;

endfunction

使用建议

- 初学者傻瓜式用法,可以 全部采用task来定义方法 ,因为它可以内置耗时语句,也可不以内置耗时语句。

- 经验者要区分两种方法, 非耗时方法使用function,耗时方法使用task ,也就是function中完成纯粹的逻辑运算,而task更多完成需要耗时的信号采样或者驱动等场景。

- 调用function:在function和task内均可以调用其他function;用task,如果被调用task内使用了耗时语句,只能在task调用。

变量的声明周期

- sv中数据的生命周期分为 动态(automatic)和静态(static) 。

- 局部变量 的生命周期与其所在域共存亡,也就是在function/task中的临时变量, 在其被调用结束后,临时变量的生命周期也将终结 。

- 全局变量 在程序执行 开始到结束一直存在 。

- 如果数据变量被声明为automatic,那么在进入该进程/方法后,automatic变量会被创建,离开该进程/方法后,automatic变量被销毁。而static在仿真开始时被创建,而在进程/方法执行过程中,不会被销毁,且可以 被多个进程和方法所共享 。

- module内全部是静态变量,代表真实的电路结构。

对于automatic方法,其内部所有变量默认也是automatic。 - 对于static方法,其内部所有变量默认也是static。

- 对于static变量, 声明时应该对其做初始化 ,而初始化只会伴随它的生命周期执行一次,不会随着方法调用而多次初始化。

- 在module、program、interface声明的变量,以及其他在task/function之外声明的变量,默认是静态变量,存在于是整个仿真阶段。

设计例化和连接

模块定义

module xprop (

// Outputs

out1,

// Inputs

clk, sel, din0

);

input clk;

input sel;

input [7:0] din0;output out1;//......

//......endmodule

模块例化

module testbench;

//......

//......xprop dut(// Outputs.out1 (out1),// Inputs.clk (clk),.sel (sel),.din0 (din0));

endmodule

模块连接

模块连接就是将硬件电路在测试平台进行例化,传统的verilog验证方法,在initial过程块产生激励,驱动硬件电路完成仿真。