在 Xilinx FPGA 设计中,BUFG 是一个不带使能功能的全局时钟缓冲器(Global Clock Buffer),它是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUFG 单元,否则在布局布线时会报错。

一、CLOCK_BUFFER_TYPE

强制逻辑优化(Mandatory Logic Optimization,简称 MLO)在 link_design (在Vivado Design Suite中,link_design 命令是设计流程中的一个关键步骤。它负责将综合后的网表文件和约束文件整合起来,形成一个完整的、针对特定目标器件的设计)的开始阶段发生,支持使用 CLOCK_BUFFER_TYPE 属性来插入全局时钟缓冲器。

- 对于 7 系列设备,支持的值是 BUFG。

- 对于 UltraScale、AMD UltraScale+™ 和 Versal 设备,支持的值包括 BUFG 和 BUFGCE。

- 对于所有架构,可以使用值 NONE 来通过 MLO 和 opt_design 禁止全局时钟缓冲器的插入。

- 对于 BUFG 和 BUFGCE(带使能功能的全局时钟缓冲器),MLO 会插入相应的缓冲器类型来驱动指定的网络。

使用 CLOCK_BUFFER_TYPE 的优势在于可以通过 XDC 约束来控制缓冲器的插入,从而无需修改设计源代码或网表。使用 CLOCK_BUFFER_TYPE 插入的缓冲器不受任何限制,因此必须谨慎使用该属性,以避免在设计中引入过多的全局时钟,这可能会导致布局失败。

在优化过程中,应当仔细考虑何时以及在哪里使用全局时钟缓冲器。全局时钟缓冲器的主要目的是提高时钟信号的驱动能力和稳定性,确保时钟信号能够准确地传播到设计的每个角落。然而,过度使用全局时钟缓冲器可能会增加设计的复杂性和功耗,并可能导致布局和布线阶段的困难。

因此,在使用 CLOCK_BUFFER_TYPE 属性时,应该根据设计的具体需求和约束来仔细选择插入缓冲器的位置。通常,全局时钟缓冲器应该被放置在时钟树的关键节点上,以便最大化其效果并最小化对设计其他部分的影响。此外,还应该注意避免在设计中创建过多的全局时钟域,因为这可能会导致时钟管理和同步方面的问题。

二、BUFG 优化

MLO会保守地在时钟网络和高扇出非时钟网络(例如设备范围内的复位信号)上插入全局时钟缓冲器。

- 在 Versal 设备上,对于高扇出的非时钟网络,会插入 BUFG_FABRIC 时钟缓冲器。

- 对于 7 系列设计,只要不超过总共 12 个全局时钟缓冲器的限制,就会插入时钟缓冲器。

- 对于 UltraScale、UltraScale+ 和 Versal 设计,只要不超过总共24 个全局时钟缓冲器的限制(不包括 BUFG_GT 缓冲器),就会插入时钟缓冲器。

- 对于非时钟网络:

• 扇出必须大于 25,000。

• 由该网络驱动的逻辑的时钟周期必须低于特定设备/速度等级的限制。 - 对于 fabric 驱动的时钟网络,扇出必须为 30 或更大。

注意:为了防止在特定网络上执行 BUFG 优化,可以将该网络的 LOCK_BUFFER_TYPE 属性设置为 NONE。此外,在强制逻辑优化过程中,也可能发生一些必要的时钟缓冲器插入操作,以确保设计的合法性。

三、MBUFG 优化

对于 Versal 设备,新的多时钟缓冲器(MBUFG)在其 O1、O2、O3、O4 输出上提供了时钟输入的 1、2、4、8 分频时钟。MBUFG 的时钟输出都使用相同的全局时钟路由资源,并且只在到达 BUFDIV_LEAF 路由通过块时才进行分频。由 MBUFG 驱动的时钟消耗的路由资源更少,并且由于公共节点更接近源和目标,因此由相同 MBUFG 驱动的时钟之间的同步跨时钟域(CDC)路径的时钟偏斜最小化。

MBUFG 优化将由公共驱动器或时钟修改块(CMB)如 MMCM、DPLL 或 XPLL 驱动的并行时钟缓冲器转换为 MBUFG。如果并行时钟的分频因子是公共时钟的 1、2、4、8 分频,则会发生这种转换。对于由 CMB 驱动的时钟,相位偏移必须为 0,占空比必须为 50%。如果由 BUFG 驱动的时钟网络具有冲突的约束,如 CLOCK_DELAY_GROUP 或 USER_CLOCK_ROOT,则也会阻止转换。只有当转换不会破坏时序约束时,才会进行转换。以下转换受支持:

• 连接到 CMB 的并行 BUFGCE 转换为 MBUFGCE。

• 连接到公共时钟驱动器的并行 BUFGCE_DIV 转换为 MBUFGCE。

• 连接到公共时钟驱动器的并行 BUFG_GT 转换为 MBUFG_GT。

除了使用 -mbufg_opt 选项的全局优化外,还可以使用 MBUFG_GROUP 属性来控制选定 BUFG 到 MBUFG 的转换。必须在直接连接到时钟缓冲器的网段上设置 MBUFG_GROUP 约束。以下示例显示了应用于两个时钟网络的属性,这两个网络由时钟缓冲器直接驱动:

set_property MBUFG_GROUP grp1 [get_nets -of [get_pins {BUFG_inst_0/O

BUFG_inst_1/O}]

在上面的 Tcl 命令中,MBUFG_GROUP 属性被设置为 grp1,并应用于与 BUFG_inst_0/O 和 BUFG_inst_1/O 这两个引脚直接相连的网段。这样,Vivado 会在优化过程中考虑将这些 BUFG 转换为 MBUFG。

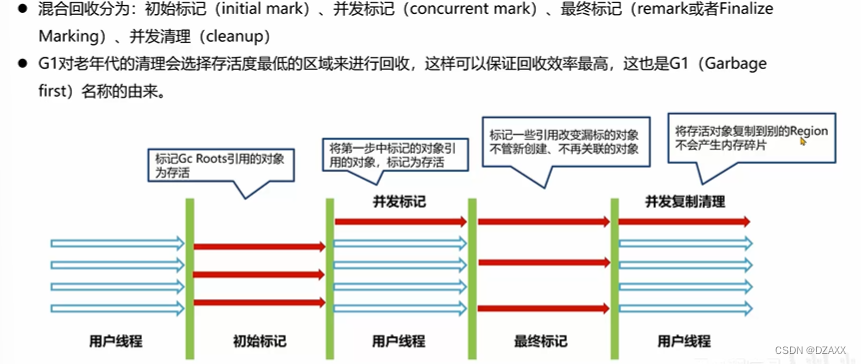

图1中所示的是一个MMCM(混合模式时钟管理器)驱动多个BUFGCE(带使能功能的全局时钟缓冲器)缓冲器的场景。由 CLKOUTn 驱动的时钟是 CLKOUT1 驱动时钟的 1、2、4、8 分频整数倍。

在 MBUFG 优化之后,这四个 BUFGCE 被转换为一个单独的 MBUFGCE,并且原本由 CLKOUT1 驱动的时钟连接到 MBUFGCE 的 I 引脚。原本由 BUFGCEs 驱动的负载现在连接到 MBUFGCE 的 O1、O2、O3、O4 引脚。

这样的转换可以节省全局时钟路由资源,减少时钟偏斜,并简化时钟网络的设计。由于 MBUFGCE 提供了多个分频输出,因此可以方便地为不同的时钟域提供所需的时钟频率,同时保持较低的时钟偏斜和路由复杂性。

在进行这种优化时,Vivado 工具会检查时钟网络的约束和时序要求,以确保转换是安全的,并且不会破坏设计的时序性能。如果转换可能导致时序问题或违反其他设计约束,Vivado 将不会执行此优化。因此,在进行 MBUFG 优化时,最好对设计进行充分的时序验证和仿真,以确保最终设计的正确性和性能。