平台:vivado2018.3

具体内容见ug571-ultrascale-selectio

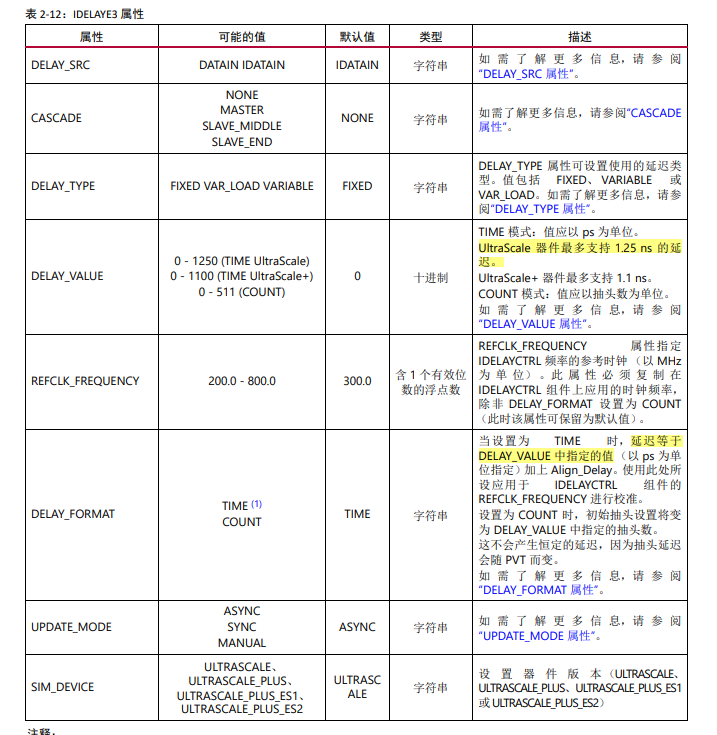

IDELAYE3

在调试超高速信号的时候,需要使用iodelay+iserdes来调试校准输入信号。例如外部某ADC采样率为5GHZ,外部ADC使用2.5GHZ的时钟去采集输入信号。为了实现采集,adc芯片使用了4个1.25ghz采样率的小ADC来采集。但是由于FPGA的工艺,在FPGA内部无法处理高达1.25ghz的信号。外部信号采用并行数据输入,在双边沿采集信号。输入随路时钟为625mhz的双边沿数据。但是对于一般的工程,内部时钟跑到625mhz对于FPGA的时序要求太高。所以我们将625mhz的时钟通过idelay+iserdes的结构。将625mhz的ddr数据转换为312.5mhz的4路单边沿数据。由于芯片采用的并行数据输入,在pcb布局,fpga引脚这些问题上,导致并行输入信号在进入FPGA内部的时间不一致,导致我们采集的输入数据就会出现亚稳态,可能提前也可能延后。这时候我们就需要使用iodelay来对数据进行校准,保证时钟每次采集的数据都是数据的正中心。以确保数据不会出错。

感兴趣的可以看我的另外一篇关于iodelay的文章。

IDELAY输入延迟分析-CSDN博客

那么625mhz的ddr数据如何转换为312.5mhz的呢?在FPGA中拥有serdes可以将输入的串行数据转换为并行数据。今天我们就来通过仿真简单介绍一下iodelay和iserdes。

关于IODELAY3

可以使用 IDELAYE3 原语延迟除时钟以外的任何输入信号,然后将其直接转发到器件逻辑,或者使用输入/输出互联 (IOI) 内部的单数据速率 (SDR) 时钟或双倍数据速率 (DDR) 时钟将其寄存到简单的触发器、IDDDR 或 ISERDESE3 中。不 应使用 IDELAYE3 来延迟时钟,因为 IDELAY 无法直接布线到全局时钟缓存。如必须延迟时钟,请使用 MMCM 或 PLL 生成时钟,并使用精细相移功能来延迟时钟。

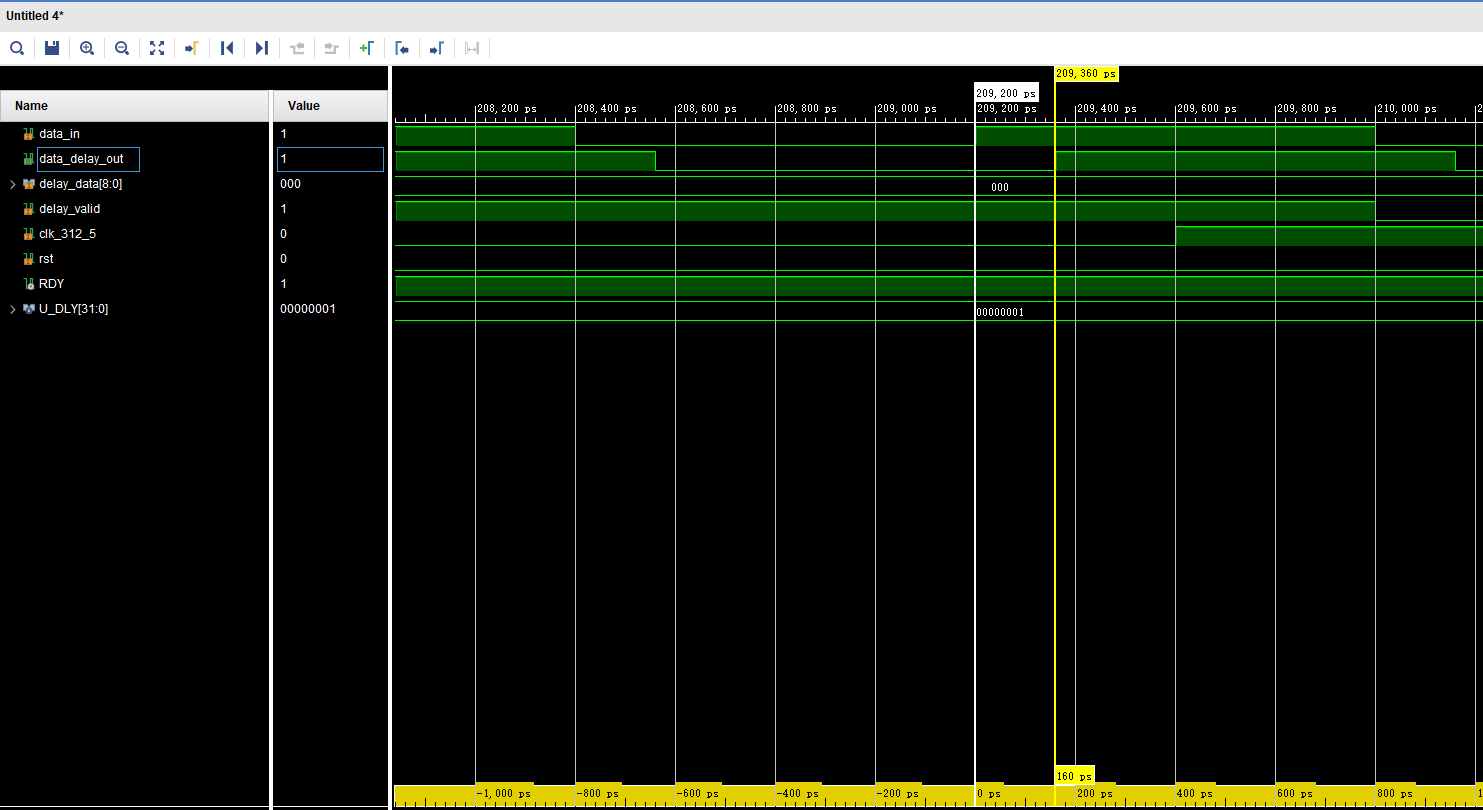

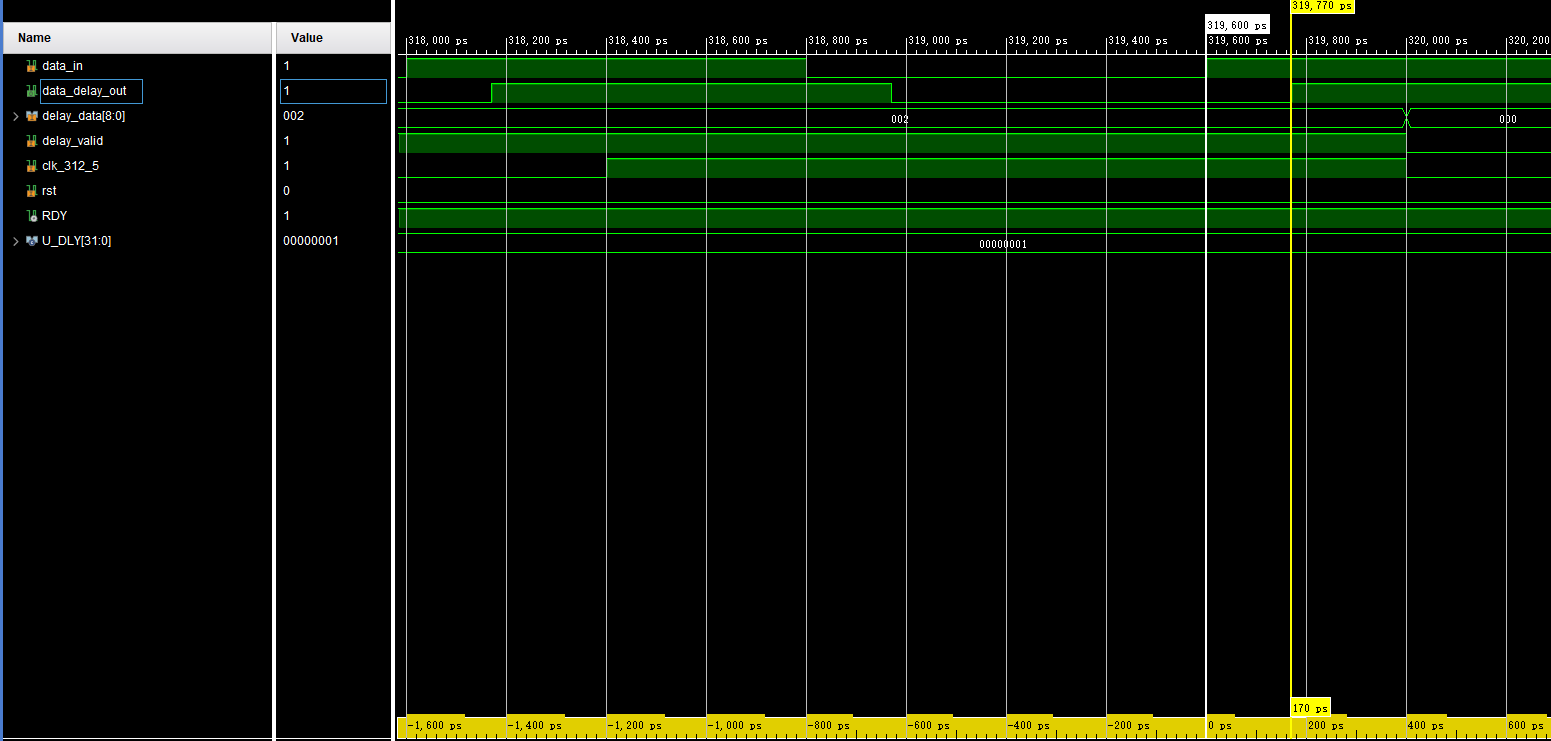

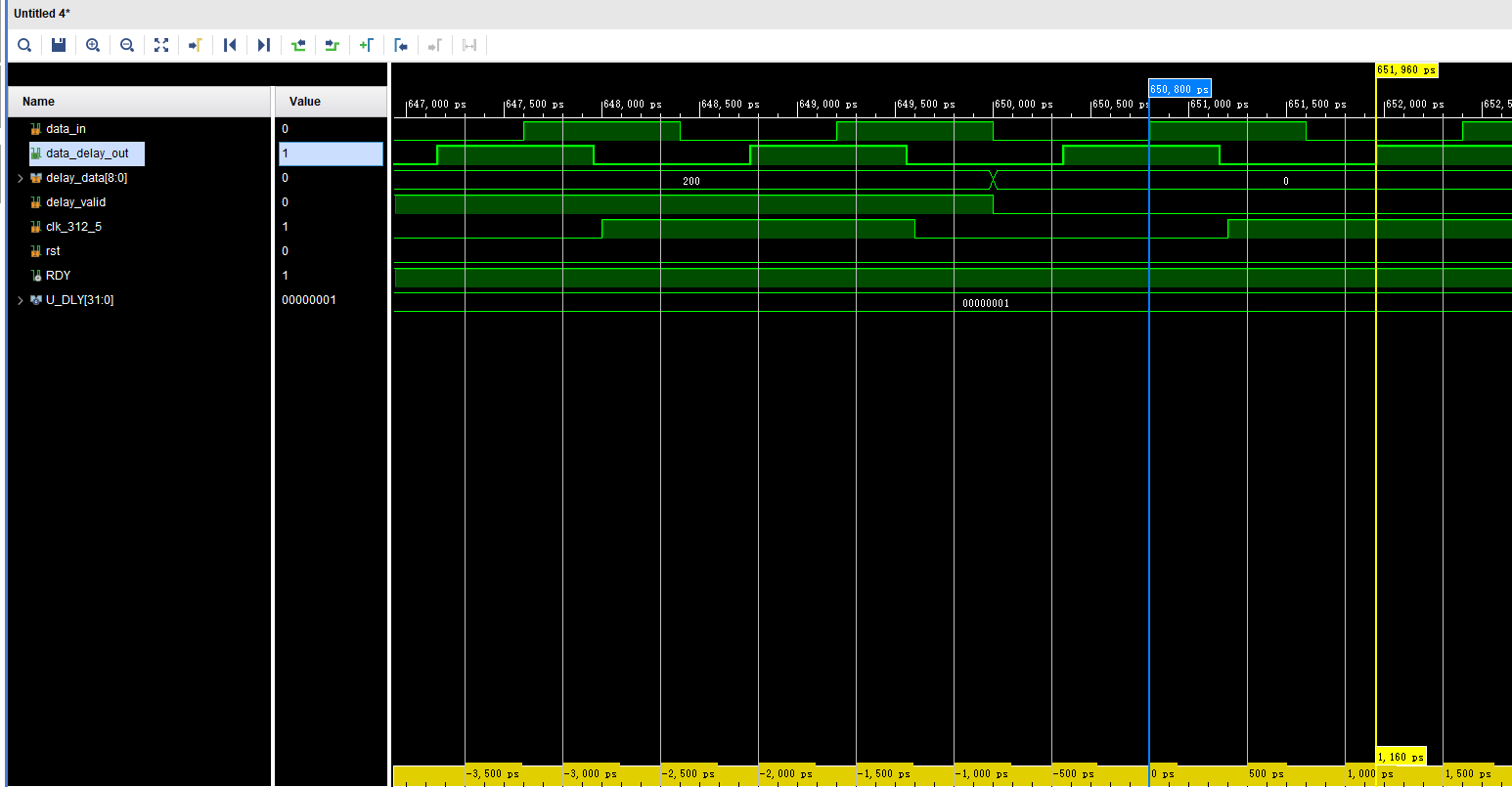

需要注意的是,IDELAY3原语包含512抽头系数。仿真实测每个taps实际为5ps。仿真测试接入IDELAY3产生的固有延迟为160ps。

IDELAY3拥有两种模式。

COUNT模式和TIME模式。

COUNT模式不需要IDELAYCTRL,无校准,只是记数tap的个数(最多512个taps)

TIME模式需要IDELAYCTRL,有校准。

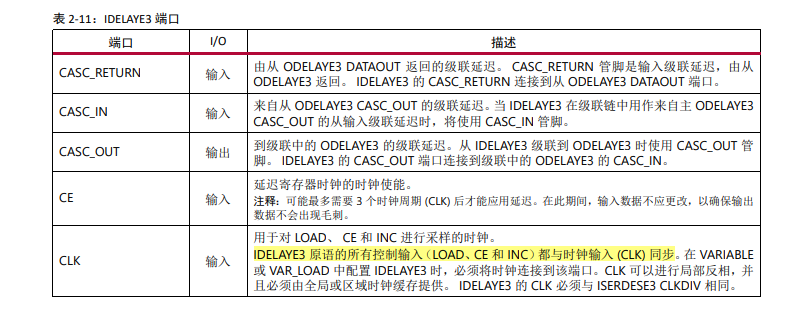

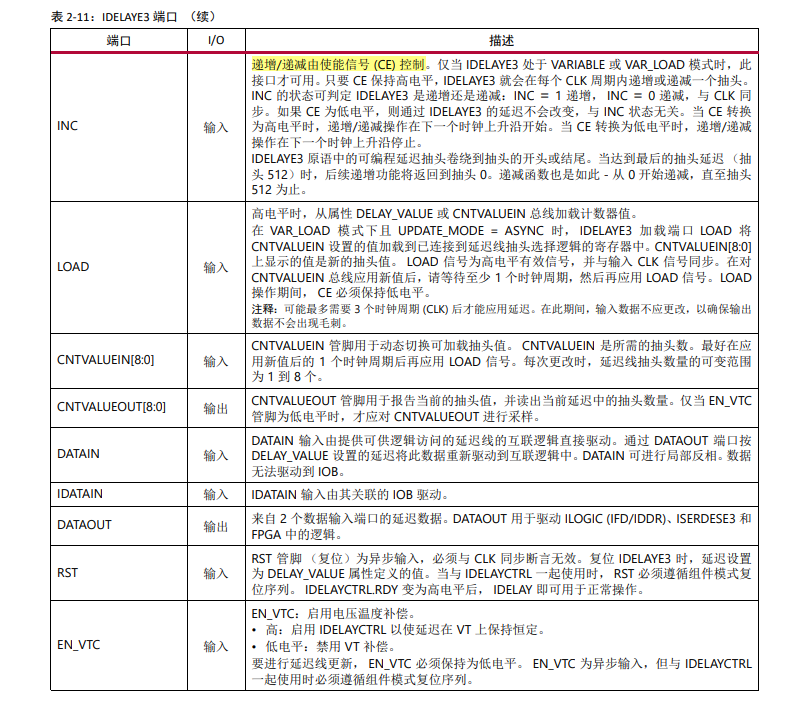

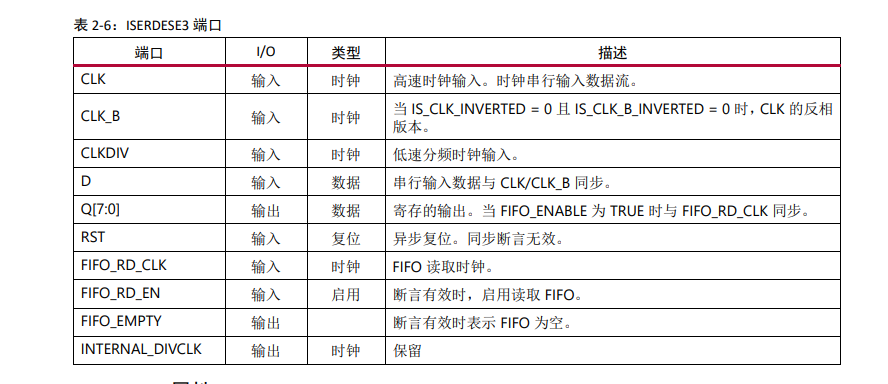

端口介绍

关于ISERDESE3

UltraScale器件中的ISERDESE3是具有特定时控和逻辑功能的串并转换器,便于实现高速源同步应用。

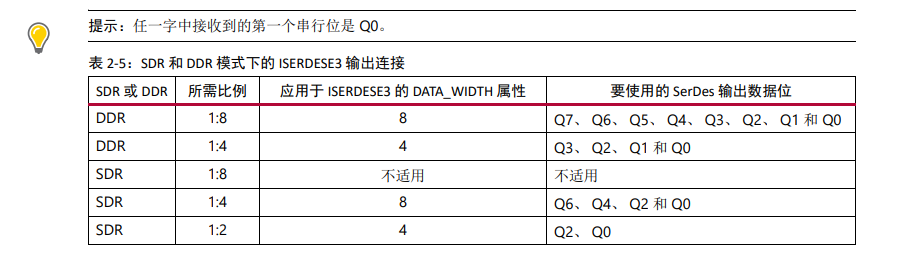

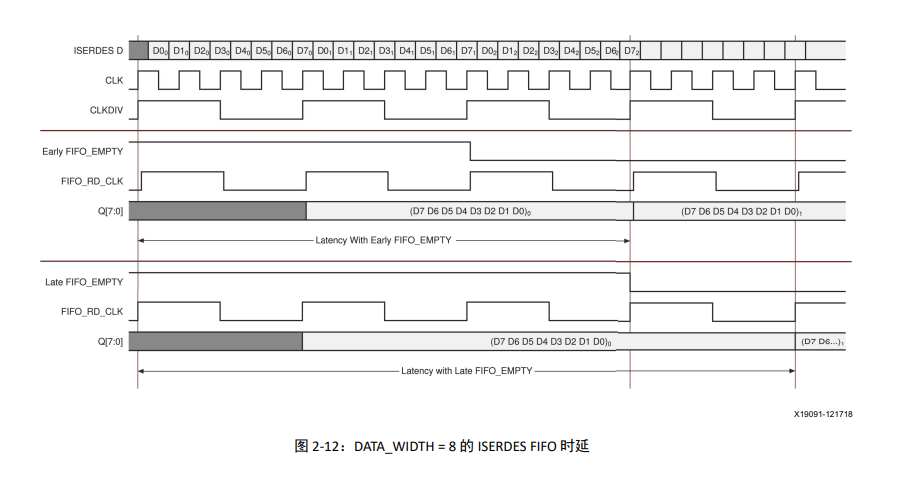

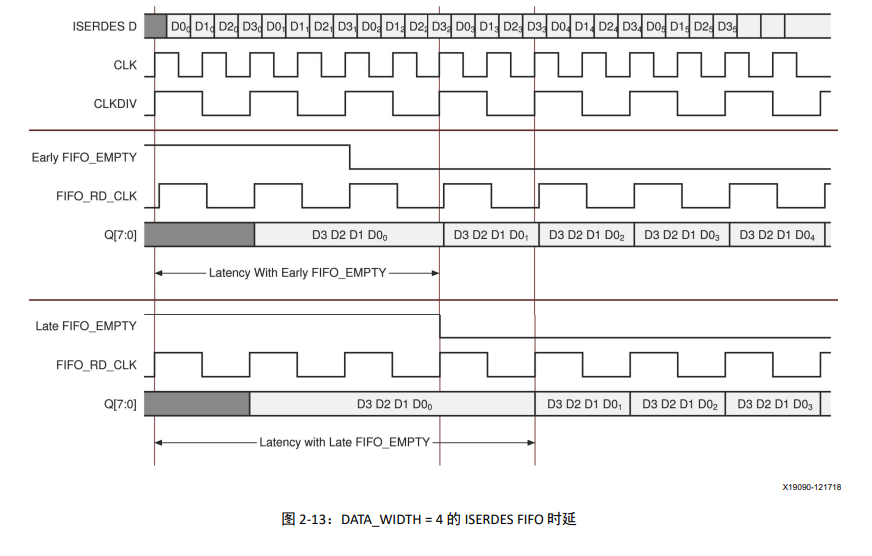

ISERDESE3可在SDR数据捕获中将传入信号按2或4位进行解串,而在DDR数据捕获模式中则可以按4或8位进行解串。当用于SDR数据捕获时,每隔一个数据输出管脚即为有效输出。例如,当使用SDR时钟作为1:4解串器时,数据宽度应设置为8,接收到的数据取自 Q0、Q2、Q4和Q6。 ISERDES还包含一个较浅的八元素FIFO。可用于跨时钟域传输。

ISERDES还包含一个较浅的八元素FIFO。可用于跨时钟域传输。

ISERDES可以定义串并转换器宽度。为4位和8位。

ISERDES的端口介绍

ISERDES的属性

下面我们在逻辑中做仿真。模拟外部输入的625mhz的DDR数据,通过调节idelay和使用iserdes将输入的串行信号转换位并行数据。

代码仿真

使用idelay,设置idelay时钟位312.5mhz。输入625mhz的串行ddr数据。

// *********************************************************************************/

// Project Name :

// Author : i_huyi

// Email : i_huyi@qq.com

// Creat Time : 2024/4/1 16:22:39

// File Name : .v

// Module Name :

// Called By :

// Abstract :

//

// CopyRight(c) 2020, xxx xxx xxx Co., Ltd..

// All Rights Reserved

//

// *********************************************************************************/

// Modification History:

// 1. initial

// *********************************************************************************/

// *************************

// MODULE DEFINITION

// *************************

`timescale 1 ns / 1 ps

module io_delay3#(

parameter U_DLY = 1)(

//serdes data in and Parallel data out

input wire data_in ,

output wire data_delay_out ,

//iodelay

input wire[8:0] delay_data ,//延迟值

input wire delay_valid ,//延迟值有效

//system signal

input wire clk_312_5 ,//312.5

input wire rst );

//--------------------------------------

// localparam

//--------------------------------------//--------------------------------------

// register

//--------------------------------------//--------------------------------------

// wire

//--------------------------------------//--------------------------------------

// assign

//--------------------------------------//------------------------------------------------------------

//------------------------------------------------------------

//------------------------------------------------------------

//------------------------------------------------------------

IDELAYCTRL #(.SIM_DEVICE ("ULTRASCALE" )// Must be set to "ULTRASCALE"

)

IDELAYCTRL_inst (.RDY (RDY ),// 1-bit output: Ready output.REFCLK (clk_312_5 ),// 1-bit input: Reference clock input.RST (rst )// 1-bit input: Active high reset input. Asynchronous assert, synchronous deassert to// REFCLK.);

//------------------------------------------------------------

//------------------------------------------------------------

IDELAYE3 #(.CASCADE ("NONE" ),// Cascade setting (MASTER, NONE, SLAVE_END, SLAVE_MIDDLE).DELAY_FORMAT ("TIME" ),// Units of the DELAY_VALUE (COUNT, TIME).DELAY_SRC ("IDATAIN" ),// Delay input (DATAIN, IDATAIN).DELAY_TYPE ("VAR_LOAD" ),// Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD).DELAY_VALUE (0 ),// Input delay value setting.IS_CLK_INVERTED (1'b0 ),// Optional inversion for CLK.IS_RST_INVERTED (1'b0 ),// Optional inversion for RST.REFCLK_FREQUENCY (312.5 ),// IDELAYCTRL clock input frequency in MHz (200.0-2667.0).SIM_DEVICE ("ULTRASCALE" ),// Set the device version (ULTRASCALE, ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1,// ULTRASCALE_PLUS_ES2).UPDATE_MODE ("ASYNC" )// Determines when updates to the delay will take effect (ASYNC, MANUAL, SYNC)

)

IDELAYE3_inst (.CASC_OUT ( ),// 1-bit output: Cascade delay output to ODELAY input cascade.CNTVALUEOUT ( ),// 9-bit output: Counter value output.DATAOUT (data_delay_out ),// 1-bit output: Delayed data output.CASC_IN (1'b0 ),// 1-bit input: Cascade delay input from slave ODELAY CASCADE_OUT.CASC_RETURN (1'b0 ),// 1-bit input: Cascade delay returning from slave ODELAY DATAOUT.CE (1'b0 ),// 1-bit input: Active high enable increment/decrement input.CLK (clk_312_5 ),// 1-bit input: Clock input.CNTVALUEIN (delay_data ),// 9-bit input: Counter value input.DATAIN (1'b0 ),// 1-bit input: Data input from the logic.EN_VTC (~delay_valid ),// 1-bit input: Keep delay constant over VT.IDATAIN (data_in ),// 1-bit input: Data input from the IOBUF.INC (1'b1 ),// 1-bit input: Increment / Decrement tap delay input.LOAD (delay_valid ),// 1-bit input: Load DELAY_VALUE input.RST (rst )// 1-bit input: Asynchronous Reset to the DELAY_VALUE

);

//------------------------------------------------------------

//------------------------------------------------------------//------------------------------------------------------------

//------------------------------------------------------------

endmodule

使用iserdes,ddr数据输入。输出比例为1:4。

// *********************************************************************************/

// Project Name :

// Author : i_huyi

// Email : i_huyi@qq.com

// Creat Time : 2024/4/1 16:32:49

// File Name : .v

// Module Name :

// Called By :

// Abstract :

//

// CopyRight(c) 2020, xxx xxx xxx Co., Ltd..

// All Rights Reserved

//

// *********************************************************************************/

// Modification History:

// 1. initial

// *********************************************************************************/

// *************************

// MODULE DEFINITION

// *************************

`timescale 1 ns / 1 ps

module iserdes3#(

parameter U_DLY = 1)(

//serdes data in and Parallel data out

input wire data_in ,

output wire[3:0] data_out ,

//system signal

input wire clk_312_5 ,//625

input wire clk_625_p ,//625mhz

input wire clk_625_n ,

input wire rst );

//--------------------------------------

// localparam

//--------------------------------------//--------------------------------------

// register

//--------------------------------------//--------------------------------------

// wire

//--------------------------------------//--------------------------------------

// assign

//--------------------------------------//------------------------------------------------------------

//------------------------------------------------------------

ISERDESE3 #(.DATA_WIDTH (4 ),// Parallel data width (4,8).FIFO_ENABLE ("FALSE" ),// Enables the use of the FIFO.FIFO_SYNC_MODE ("FALSE" ),// Always set to FALSE. TRUE is reserved for later use..IS_CLK_B_INVERTED (1'b0 ),// Optional inversion for CLK_B.IS_CLK_INVERTED (1'b0 ),// Optional inversion for CLK.IS_RST_INVERTED (1'b0 ),// Optional inversion for RST.SIM_DEVICE ("ULTRASCALE" )// Set the device version (ULTRASCALE, ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1,ULTRASCALE_PLUS_ES2)

)

ISERDESE3_inst (.FIFO_EMPTY ( ),// 1-bit output: FIFO empty flag.INTERNAL_DIVCLK ( ),// 1-bit output: Internally divided down clock used when FIFO is, disabled (do not connect).Q (data_out ),// 8-bit registered output.CLK (clk_625_p ),// 1-bit input: High-speed clock.CLKDIV (clk_312_5 ),// 1-bit input: Divided Clock.CLK_B (clk_625_n ),// 1-bit input: Inversion of High-speed clock CLK.D (data_in ),// 1-bit input: Serial Data Input.FIFO_RD_CLK ( ),// 1-bit input: FIFO read clock.FIFO_RD_EN ( ),// 1-bit input: Enables reading the FIFO when asserted.RST (rst )// 1-bit input: Asynchronous Reset

);

//------------------------------------------------------------

//------------------------------------------------------------//------------------------------------------------------------

//------------------------------------------------------------

endmodule

顶层例化两个模块。

// *********************************************************************************/

// Project Name :

// Author : i_huyi

// Email : i_huyi@qq.com

// Creat Time : 2024/4/1 15:53:53

// File Name : .v

// Module Name :

// Called By :

// Abstract :

// iserdes + iodelay

//

// CopyRight(c) 2020, xxx xxx xxx Co., Ltd..

// All Rights Reserved

//

// *********************************************************************************/

// Modification History:

// 1. initial

// *********************************************************************************/

// *************************

// MODULE DEFINITION

// *************************

`timescale 1 ns / 1 ps

module io_delay_iserdes#(

parameter U_DLY = 1)(

//serdes data in and Parallel data out

input wire data_in ,

output wire[3:0] data_out ,

//iodelay

input wire[8:0] delay_data ,//延迟值

input wire delay_valid ,//延迟值有效

//system signal

input wire clk_312_5 ,//625

input wire clk_625_p ,//625mhz

input wire clk_625_n ,

input wire rst );

//--------------------------------------

// localparam

//--------------------------------------//--------------------------------------

// register

//--------------------------------------//--------------------------------------

// wire

//--------------------------------------//--------------------------------------

// assign

//--------------------------------------

io_delay3 u_io_delay3 (

//serdes data in .data_in (data_in ),.data_delay_out (data_delay_out ),

//iodelay.delay_data (delay_data ),.delay_valid (delay_valid ),

//system signal.clk_312_5 (clk_312_5 ),.rst (rst ));//------------------------------------------------------------

//------------------------------------------------------------

iserdes3 U_iserdes3(

//serdes data in and Parallel data out .data_in (data_delay_out ),.data_out (data_out ),

//system signal.clk_312_5 (clk_312_5 ),.clk_625_p (clk_625_p ),.clk_625_n (clk_625_n ),.rst (rst ));//------------------------------------------------------------

//------------------------------------------------------------

//

endmodule

添加仿真文件

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/04/01 16:43:25

// Design Name:

// Module Name: vtf_io_delay_iserdes

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module vtf_io_delay_iserdes;

//

wire [9:0] adc_di_p ;//iodelay

reg [8:0] delay_data ;//延迟值

reg delay_valid ;//延迟值有效

//system signal

reg clk_312_5 ;//625

reg clk_625_p ;//625mhz

reg clk_625_n ;

reg rst ;reg data_clk ;wire [3:0] data_out[9:0] ; wire [9:0] data_p0 ;

wire [9:0] data_p1 ;

wire [9:0] data_p2 ;

wire [9:0] data_p3 ;//-----------------------------------------------------------

//-----------------------------------------------------------

assign data_p0 = { data_out[9][0],data_out[8][0],data_out[7][0],data_out[6][0],data_out[5][0],data_out[4][0],data_out[3][0],data_out[2][0],data_out[1][0],data_out[0][0]};

assign data_p1 = { data_out[9][1],data_out[8][1],data_out[7][1],data_out[6][1],data_out[5][1],data_out[4][1],data_out[3][1],data_out[2][1],data_out[1][1],data_out[0][1]};

assign data_p2 = { data_out[9][2],data_out[8][2],data_out[7][2],data_out[6][2],data_out[5][2],data_out[4][2],data_out[3][2],data_out[2][2],data_out[1][2],data_out[0][2]};

assign data_p3 = { data_out[9][3],data_out[8][3],data_out[7][3],data_out[6][3],data_out[5][3],data_out[4][3],data_out[3][3],data_out[2][3],data_out[1][3],data_out[0][3]};//-----------------------------------------------------------

//-----------------------------------------------------------

parameter WIDTH = 10;

//-----------------------------------------------------------

//-----------------------------------------------------------genvar i;generatefor (i = 0; i<=(WIDTH-1); i = i +1) begin : adc_ch_di_pio_delay_iserdes u_io_delay_iserdes(//serdes data in and Parallel data out .data_in (adc_di_p[i] ),.data_out (data_out[i] ),//iodelay.delay_data (delay_data ),.delay_valid (delay_valid ),//system signal.clk_312_5 (clk_312_5 ),.clk_625_p (clk_625_p ),.clk_625_n (clk_625_n ),.rst (rst ));endendgenerate

//-----------------------------------------------------------

//-----------------------------------------------------------initial

begindelay_data =0;delay_valid =0;data_clk =0;clk_312_5 =0;clk_625_p =0;clk_625_n =1;rst =1;#100;rst =0;#100;delay_data =9'd0;delay_valid =1'b1;#10;delay_data =9'd0;delay_valid =1'b0;#100;delay_data =9'd2;delay_valid =1'b1;#10;delay_data =9'd0;delay_valid =1'b0;#100;delay_data =9'd3;delay_valid =1'b1;#10;delay_data =9'd0;delay_valid =1'b0;#100;delay_data =9'd4;delay_valid =1'b1;#10;delay_data =9'd0;delay_valid =1'b0;#100;delay_data =9'd200;delay_valid =1'b1;#10;delay_data =9'd0;delay_valid =1'b0;endreg [9:0] data_cnt ;always@(posedge data_clk or posedge rst)

beginif(rst == 1'b1)begindata_cnt <= 10'd0;endelse begindata_cnt <= data_cnt + 10'h1;end

end

//-----------------------------------------------------------

//-----------------------------------------------------------

//产生数据

assign adc_di_p[0] = data_cnt[0];

assign adc_di_p[1] = data_cnt[1];

assign adc_di_p[2] = data_cnt[2];

assign adc_di_p[3] = data_cnt[3];

assign adc_di_p[4] = data_cnt[4];

assign adc_di_p[5] = data_cnt[5];

assign adc_di_p[6] = data_cnt[6];

assign adc_di_p[7] = data_cnt[7];

assign adc_di_p[8] = data_cnt[8];

assign adc_di_p[9] = data_cnt[9];always #1.6 clk_312_5 = ~clk_312_5;

always #0.8 clk_625_p = ~clk_625_p;

always #0.8 clk_625_n = ~clk_625_n;

always #0.4 data_clk = ~data_clk;endmodule

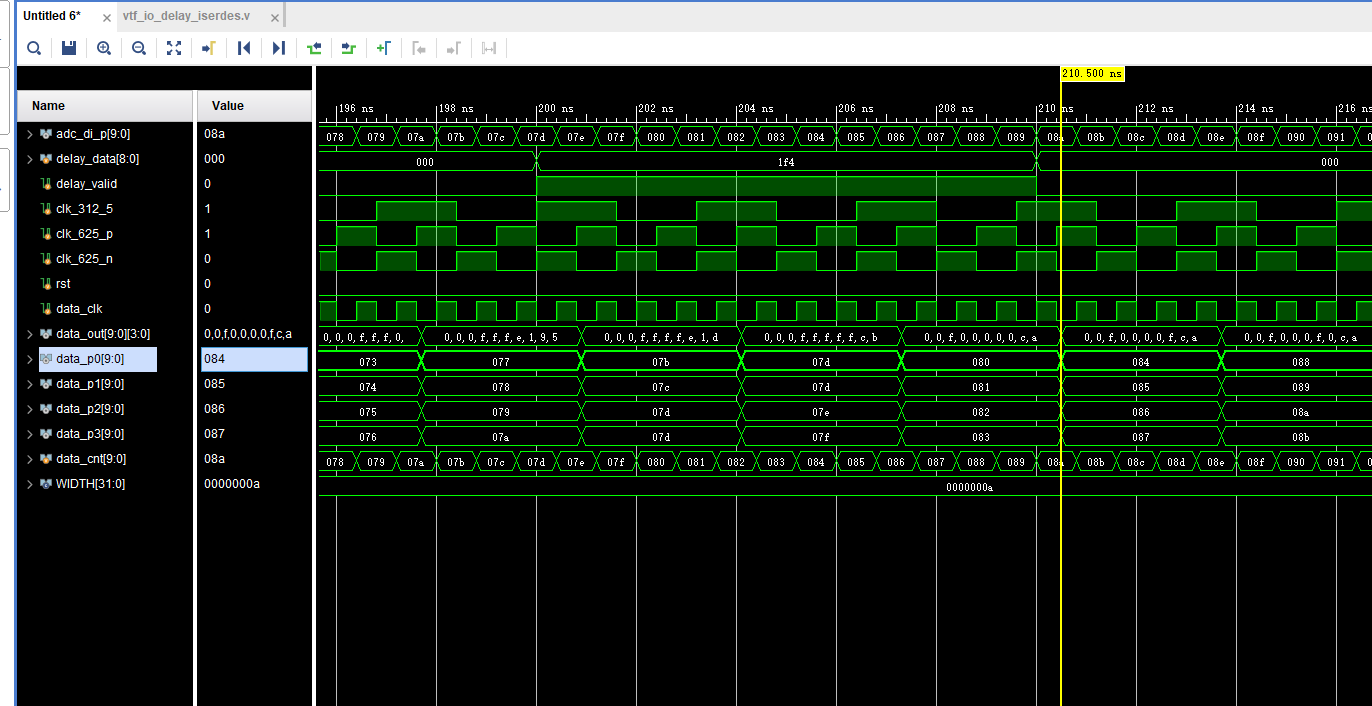

在仿真文件中,我们模式外部ADC采集输入的并行数据。使用1.25ghz时钟将数据产生。产生的数据将通过并行的十根数据线发送到idelay+iserdes模块分别进行解串。解串后的数据为单bit的312.5mhz的四组并行数据。在仿真顶层我们需要将该数据装换为10bit的312.5mhz数据。所以这里例化十个解串模块。将其解串后的数据进行拼合。就将原始的10bit的1.25ghz的数据转换为了四组312.5mhz的10bit数据流。接下来具体看一下效果。

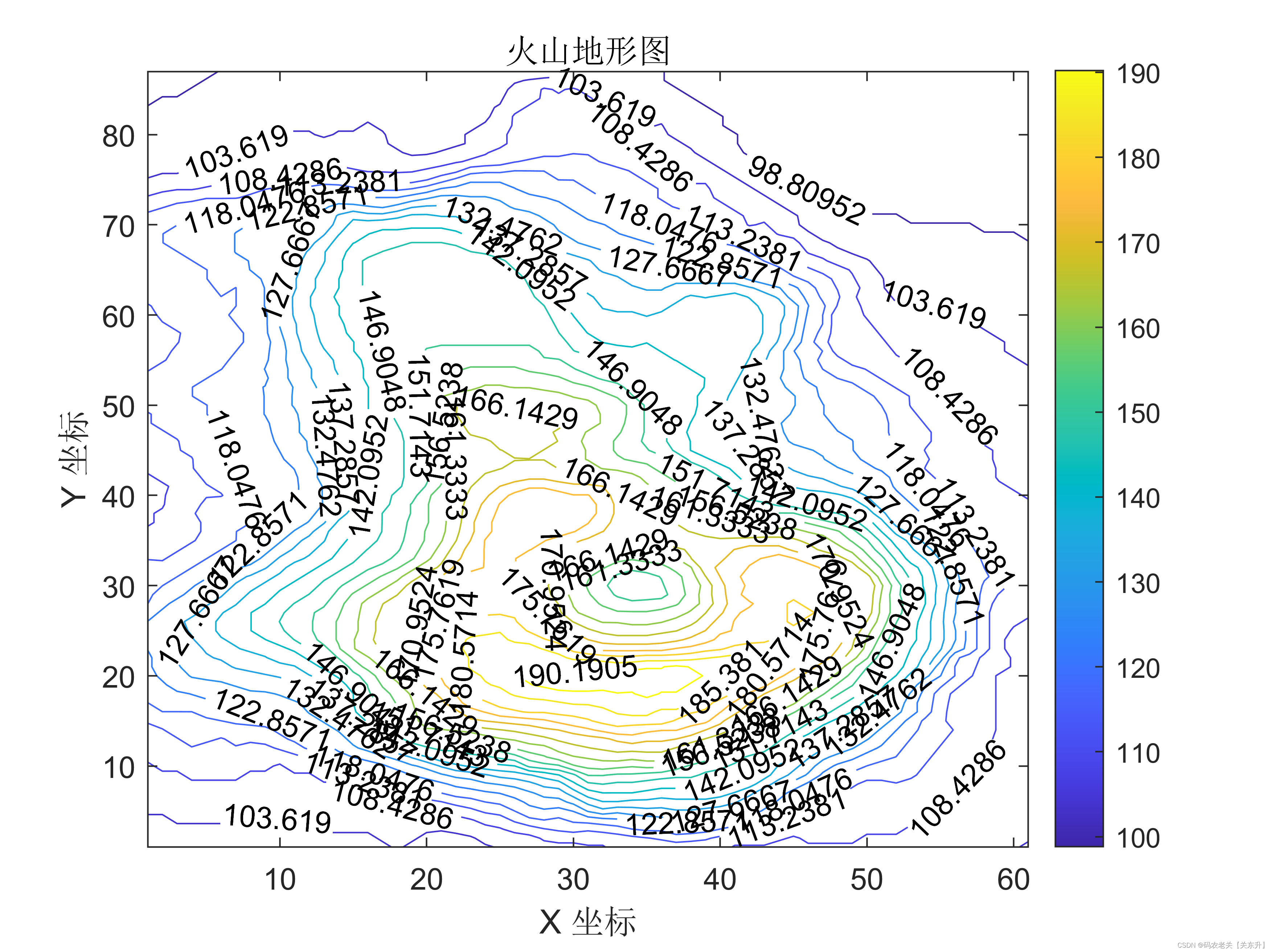

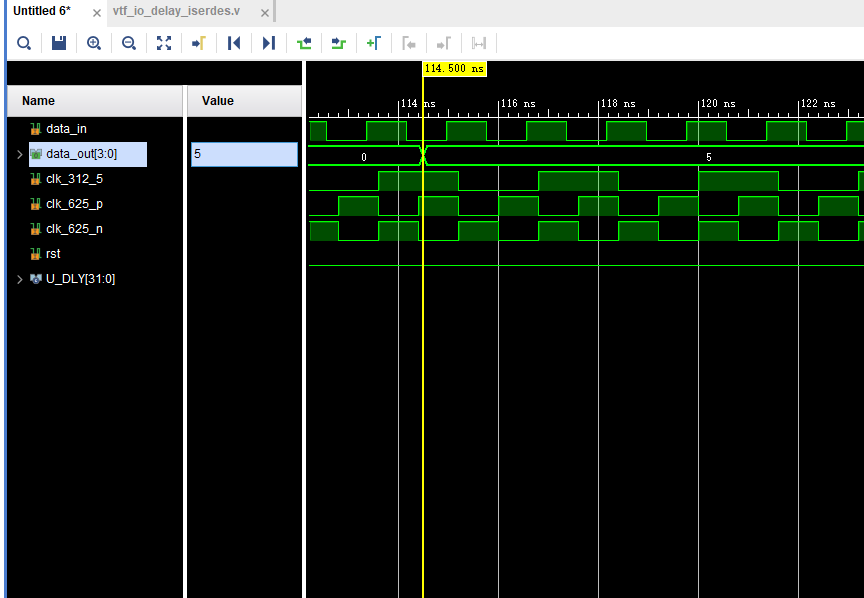

idelay调节。调节tap为0。可以看到调节后的数据较输入原始数据延迟了160ps。

idelay调节。调节tap为2。可以看到调节后的数据较输入原始数据延迟了170ps。

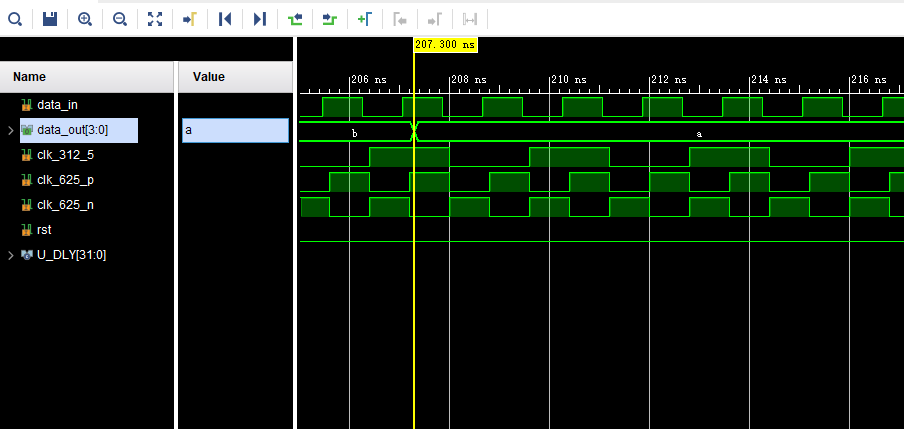

idelay调节。调节tap为200。可以看到调节后的数据较输入原始数据延迟了1160ps。

iserdes解串出来的数据。

为了验证每个通道到达iserdes数据的先后顺序不一致。我们在仿真时,将输入的bit0,作为单独的一路数据,延迟tap设置为500。

设置仿真。

io_delay_iserdes u_io_delay_iserdes0(//serdes data in and Parallel data out .data_in (adc_di_p[0] ),.data_out (data_out[0] ),//iodelay.delay_data (9'd500 ),.delay_valid (delay_valid ),//system signal.clk_312_5 (clk_312_5 ),.clk_625_p (clk_625_p ),.clk_625_n (clk_625_n ),.rst (rst ));genvar i;generatefor (i = 1; i<=(WIDTH-1); i = i +1) begin : adc_ch_di_pio_delay_iserdes u_io_delay_iserdes(//serdes data in and Parallel data out .data_in (adc_di_p[i] ),.data_out (data_out[i] ),//iodelay.delay_data (delay_data ),.delay_valid (delay_valid ),//system signal.clk_312_5 (clk_312_5 ),.clk_625_p (clk_625_p ),.clk_625_n (clk_625_n ),.rst (rst ));endendgenerate bit0进过iserdes解串出来的并行数据。idelay=0;

bit0进过iserdes解串出来的并行数据。idelay=500;

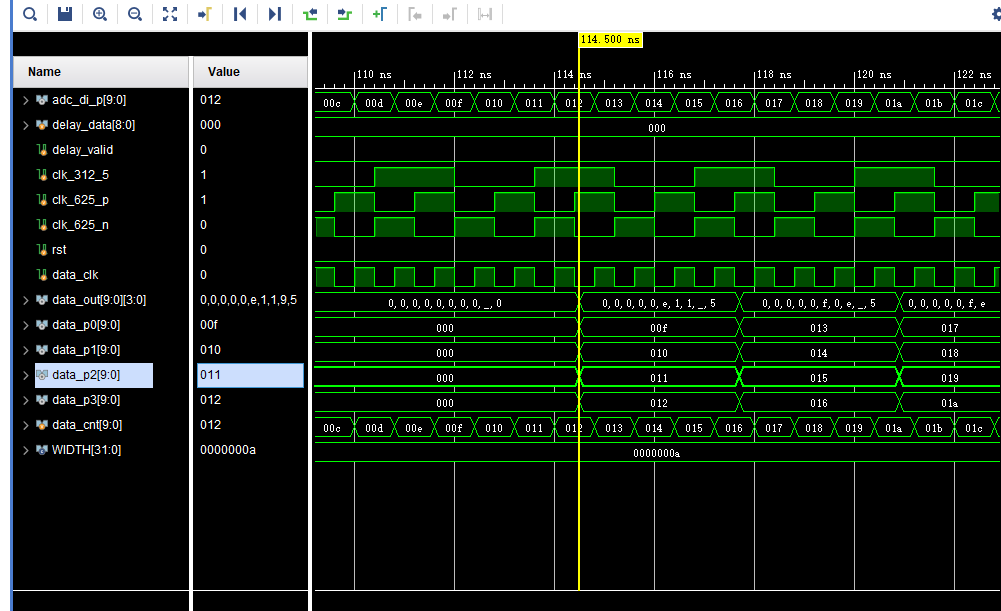

经过idelay和iserdes还原出来的数据。在调节idelay之前。输入10bit并行数据,可以看到输出的数据为00f,010,011,012,与输入的1.25ghz数据一致。

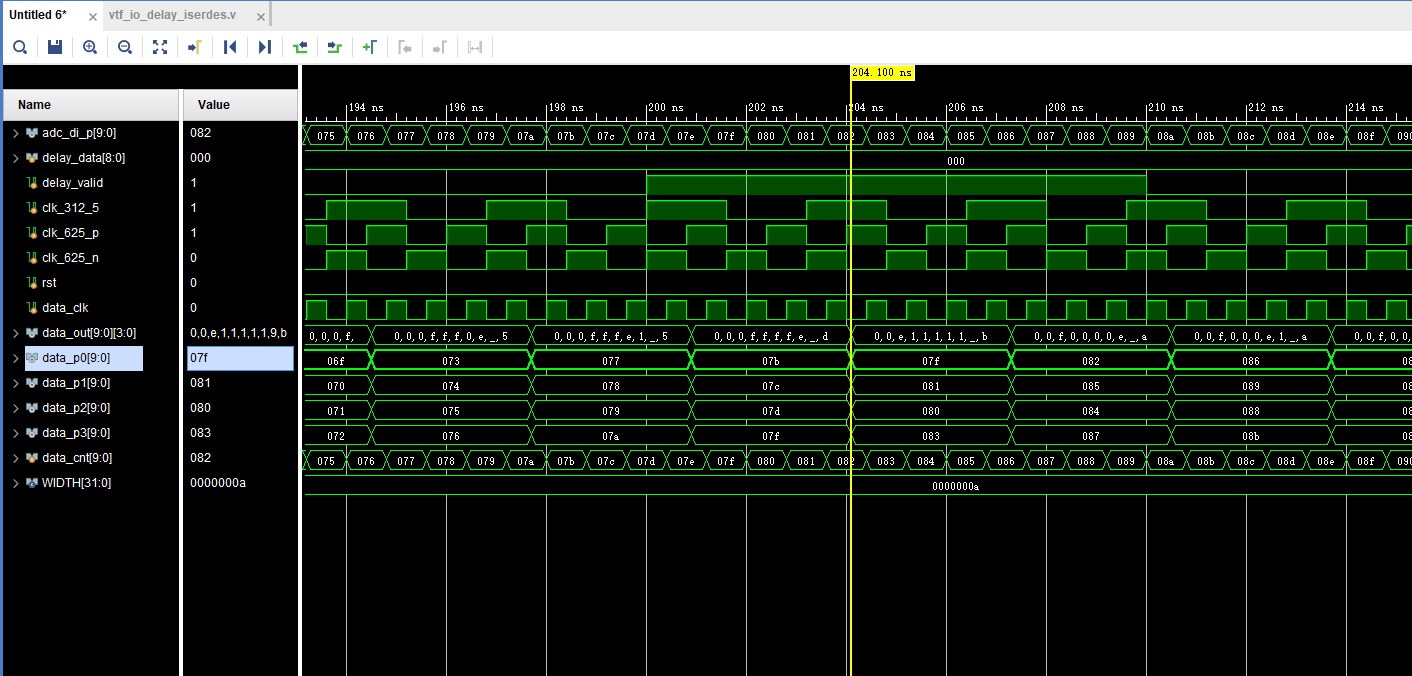

经过idelay和iserdes还原出来的数据。在调节idelay之后。输入10bit并行数据,可以看到输出的数据为07f,081,080,083,与输入的1.25ghz数据不一致。数据已经错误。

这时再将所有通道idelay延迟设置为500taps。观察解串后的数据。

genvar i;generatefor (i = 0; i<=(WIDTH-1); i = i +1) begin : adc_ch_di_pio_delay_iserdes u_io_delay_iserdes(//serdes data in and Parallel data out .data_in (adc_di_p[i] ),.data_out (data_out[i] ),//iodelay.delay_data (delay_data ),.delay_valid (delay_valid ),//system signal.clk_312_5 (clk_312_5 ),.clk_625_p (clk_625_p ),.clk_625_n (clk_625_n ),.rst (rst ));endendgenerate

//-----------------------------------------------------------

//-----------------------------------------------------------initial

begindelay_data =0;delay_valid =0;data_clk =0;clk_312_5 =0;clk_625_p =0;clk_625_n =1;rst =1;#100;rst =0;#100;delay_data =9'd500;delay_valid =1'b1;#10;delay_data =9'd0;delay_valid =1'b0;end解串后的数据。在idelay写入时,存在几个周期的数据错误。在idelay生效后,解串出来的数据与原始数据一致。解串成功。