目录

- 1、前言

- 免责声明

- 2、相关方案推荐

- FPGA帧差算法单个目标图像识别+目标跟踪

- 3、详细设计方案

- 设计原理框图

- 运动目标检测原理

- OV5640摄像头配置与采集

- OV7725摄像头配置与采集

- RGB视频流转AXI4-Stream

- VDMA图像缓存

- 多目标帧差算法图像识别+目标跟踪模块

- 视频输出

- Xilinx系列FPGA工程源码架构

- Altera系列FPGA工程源码架构

- 4、工程代码1详解-->OV5640输入HDMI输出,Xilinx--Artix7版本

- 5、工程代码2详解-->OV5640输入HDMI输出,Xilinx--Kintex7版本

- 6、工程代码3详解-->OV5640输入HDMI输出,Xilinx--Zynq7010版本

- 7、工程代码4详解-->OV7725输入HDMI输出,Xilinx--Zynq7010版本

- 8、工程代码5详解-->OV5640输入HDMI输出,Xilinx--Zynq7020版本

- 9、工程代码6详解-->OV7725输入HDMI输出,Xilinx--Zynq7020版本

- 10、工程代码7详解-->OV5640输入LCD输出,Xilinx--Zynq7020版本

- 11、工程代码8详解-->OV7725输入LCD输出,Xilinx--Zynq7020版本

- 12、工程代码9详解-->OV5640输入HDMI输出,Xilinx--Zynq7100版本

- 13、工程代码10详解-->OV7725输入HDMI输出,Xilinx--Zynq7100版本

- 14、工程代码11详解-->OV5640输入HDMI输出,Altera--Cyclone IV版本

- 15、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 16、上板调试验证并演示

- 准备工作

- OV5640输入版本工程演示

- OV7725输入版本工程演示

- LCD显示屏输出版本工程演示

- 17、福利:工程源码获取

FPGA高端项目:FPGA帧差算法多目标图像识别+目标跟踪,提供11套工程源码和技术支持

1、前言

本设计使用Xilinx系列FPGA实现帧差算法的多目标运动物体图像识别+目标跟踪,可实时识别多个目标的运动物体,并将其在画面中框出来实时锁定,可模拟无人机空中侦查,发现目标并实时锁定跟踪,然后可操作发射导弹将其摧毁,也可在地面实时搜索空中目标,如搜索无人机,一单发现即锁定,然后可将其画面回传控制室,然后驱离或击落,也可作为公路车流、广场人流实时统计监控,甚至可以作为家里监控老鼠报警器,一单鼠洞有老鼠移动,则实时识别并报警。。。

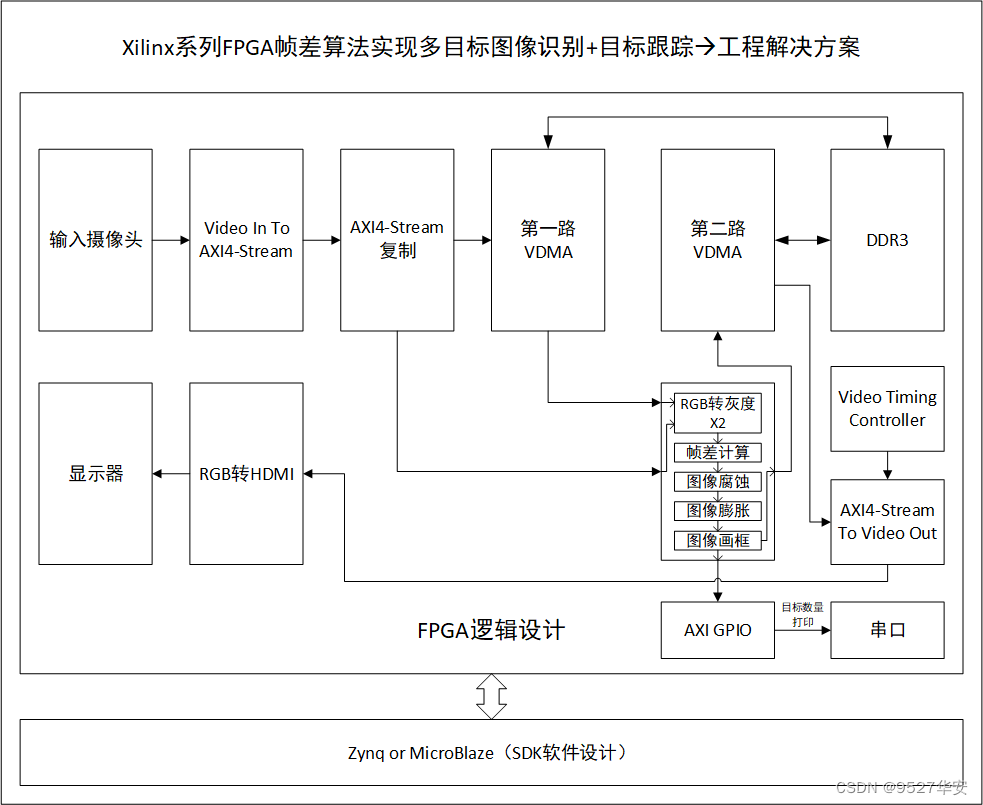

本设计使用Xilinx系列FPGA实现实时识别跟踪多目标运动物体应用,输入源为各类Sensor,可以是廉价的ov5640、ov7725等,也可以是HDMI接口的Sensor(可以用笔记本电脑作为输入模拟),FPGA通过i2纯、总线配置Sensor,然后采集Sensor视频数据,然后调用Xilinx官方的Video In To AXI4-Stream IP核将RGB视频转换为AXI4-Stream视频流;然后调用Xilinx官方的AXI4-Stream Broadcaster将AXI4-Stream视频流复制为2份,其中一份先经过Xilinx官方的VDMA缓存后读出,作为帧差算法的第一帧来源,另外一份和VDMA缓存后读出的AXI4-Stream视频流一起被送入帧差多目标识别跟踪算法模块,该模块是一个集成设计模块,包含了RGB转灰度、帧差提取、图像腐蚀、图像膨胀、多目标识别标记等模块,最后输出用红框标记的运动目标图像;然后调用Xilinx官方的Video Timing Controller和AXI4-Stream To Video Out IP核将AXI4-Stream视频流转换为RGB视频流;然后调用自研的RGB转HDMI模块将视频输出显示器显示即可;

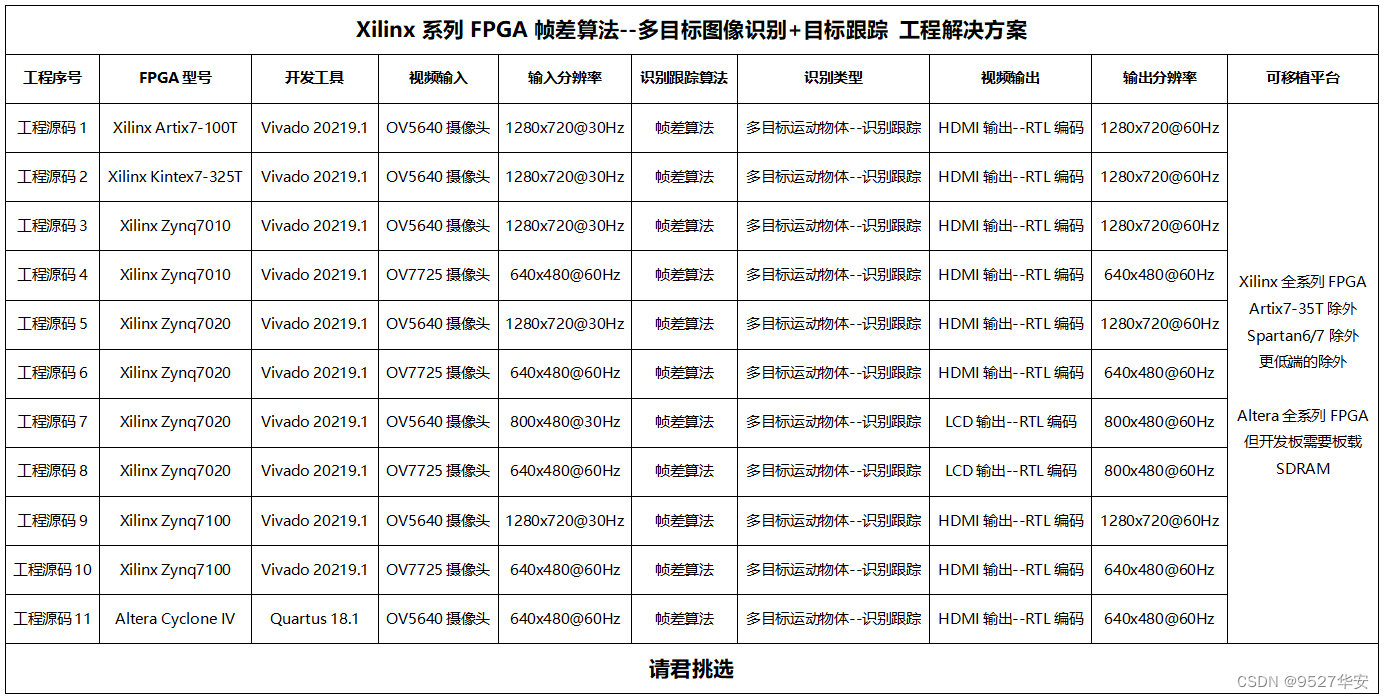

提供vivado2019.1和Quartus 18.1版本的工程源码共计11套,详情见下表:

这里说明一下提供的11套工程源码的作用和价值,如下:

工程源码1

使用开发板的FPGA型号为Xilinx–Artix7–100T;输入源为ov5640摄像头,输入分辨率为1280x720@30Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为1280x720@60Hz;HDMI编码方式为纯verilog代码方案;适用于Xilinx–Artix7系列FPGA开发板使用;

工程源码2

使用开发板的FPGA型号为Xilinx–Kintex7–325T;输入源为ov5640摄像头,输入分辨率为1280x720@30Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为1280x720@60Hz;HDMI编码方式为纯verilog代码方案;适用于Xilinx–Kintex7系列FPGA开发板使用;

工程源码3

使用开发板的FPGA型号为Xilinx–Zynq7010;输入源为ov5640摄像头,输入分辨率为1280x720@30Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为1280x720@60Hz;HDMI编码方式为纯verilog代码方案;适用于Xilinx–Zynq7000系列FPGA开发板使用;

工程源码4

使用开发板的FPGA型号为Xilinx–Zynq7010;输入源为ov7725摄像头,输入分辨率为640x480@60Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为640x480@60Hz;HDMI编码方式为纯verilog代码方案;适用于Xilinx–Zynq7000系列FPGA开发板使用;

工程源码5

使用开发板的FPGA型号为Xilinx–Zynq7020;输入源为ov5640摄像头,输入分辨率为1280x720@30Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为1280x720@60Hz;HDMI编码方式为纯verilog代码方案;适用于Xilinx–Zynq7000系列FPGA开发板使用;

工程源码6

使用开发板的FPGA型号为Xilinx–Zynq7020;输入源为ov7725摄像头,输入分辨率为640x480@60Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为640x480@60Hz;HDMI编码方式为纯verilog代码方案;适用于Xilinx–Zynq7000系列FPGA开发板使用;

工程源码7

使用开发板的FPGA型号为Xilinx–Zynq7020;输入源为ov5640摄像头,输入分辨率为800x480@30Hz;经过帧差多目标运动物体识别跟踪算法后,以4.3寸屏LCD接口输出,输出分辨率为800x480@60Hz;LCD编码方式为纯verilog代码方案;适用于Xilinx–Zynq7000系列FPGA开发板使用;

工程源码8

使用开发板的FPGA型号为Xilinx–Zynq7020;输入源为ov7725摄像头,输入分辨率为640x480@60Hz;经过帧差多目标运动物体识别跟踪算法后,以4.3寸屏LCD接口输出,输出分辨率为800x480@60Hz;LCD编码方式为纯verilog代码方案;适用于Xilinx–Zynq7000系列FPGA开发板使用;

工程源码9

使用开发板的FPGA型号为Xilinx–Zynq7100;输入源为ov5640摄像头,输入分辨率为1280x720@30Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为1280x720@60Hz;HDMI编码方式为纯verilog代码方案;适用于Xilinx–Zynq7000系列FPGA开发板使用;

工程源码10

使用开发板的FPGA型号为Xilinx–Zynq7100;输入源为ov7725摄像头,输入分辨率为640x480@60Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为640x480@60Hz;HDMI编码方式为纯verilog代码方案;适用于Xilinx–Zynq7000系列FPGA开发板使用;

工程源码11

使用开发板的FPGA型号为Altera–Cyclone IV–EP4CE10F17C8;输入源为ov5640摄像头,输入分辨率为640x480@60Hz;经过帧差多目标运动物体识别跟踪算法后,以HDMI接口输出,输出分辨率为640x480@60Hz;HDMI编码方式为纯verilog代码方案;适用于Altera–Cyclone系列FPGA开发板使用;

本文详细描述了Xilinx系列FPGA帧差算法实现多目标图像识别+目标跟踪,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

FPGA帧差算法单个目标图像识别+目标跟踪

本设计是Xilinx系列FPGA帧差算法实现多目标图像识别+目标跟踪,适用于跟踪多个运动目标,也有适用于只跟踪单个目标的方案,即FPGA帧差算法单个目标图像识别+目标跟踪方案,该方案我之前专门推出过博客介绍,感兴趣的可以去看看,博客地址如下:

点击直接前往

3、详细设计方案

设计原理框图

工程源码设计原理框图如下:

运动目标检测原理

运动目标检测原理:先将RGB图像转为灰度图只取亮度分量y,如果一个物体是运动的,那么前后两张或几张灰度图的同一位置的像素值应该是变化的,试想,如果是静止物体,比如一幅画,那么任意时刻,同一位置像素点的值不变才对,如果运动了,像素点的值自然也就改变了,很好理解,这个叫做帧差算法,这里的像素点差值有个范围,叫做阈值,cdn上有大佬说70~100是理想值。

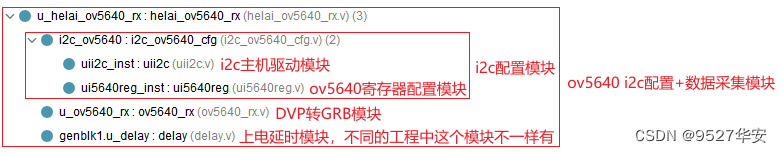

OV5640摄像头配置与采集

视频输入源由多种方案可供选择,比如廉价的OV5640、OV7725摄像头等;工程源码1、2、3、5、7、9、11使用OV5640摄像头,ov5640需要i2c配置才能使用,需要i2c配置分辨率,然后将DVP接口的两个时钟一个像素的GRB565视频数据采集为一个时钟一个像素的RGB565或者RGB888视频数据;以工程7为例,ov5640i2c配置及采集代码如下,其他工程与之类似:

注意!!4.3寸LCD屏输出的工程源码,OV5640摄像头配置由SDK软件代码完成,与上述的有FPGA纯verilog配置方式不一样;

OV7725摄像头配置与采集

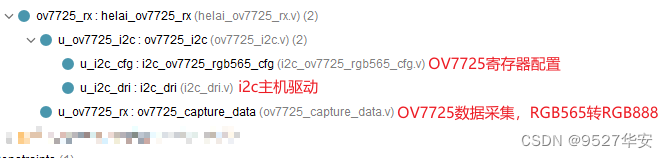

视频输入源由多种方案可供选择,比如廉价的OV5640、OV7725摄像头等;工程源码4、6、8、10使用OV7725摄像头,OV7725需要i2c配置才能使用,需要i2c配置分辨率,然后将DVP接口的两个时钟一个像素的GRB565视频数据采集为一个时钟一个像素的RGB565或者RGB888视频数据;以工程8为例,OV7725配置及采集代码如下,其他工程与之类似:

注意!!4.3寸LCD屏输出的工程源码,OV7725摄像头配置由SDK软件代码完成,与上述的有FPGA纯verilog配置方式不一样;

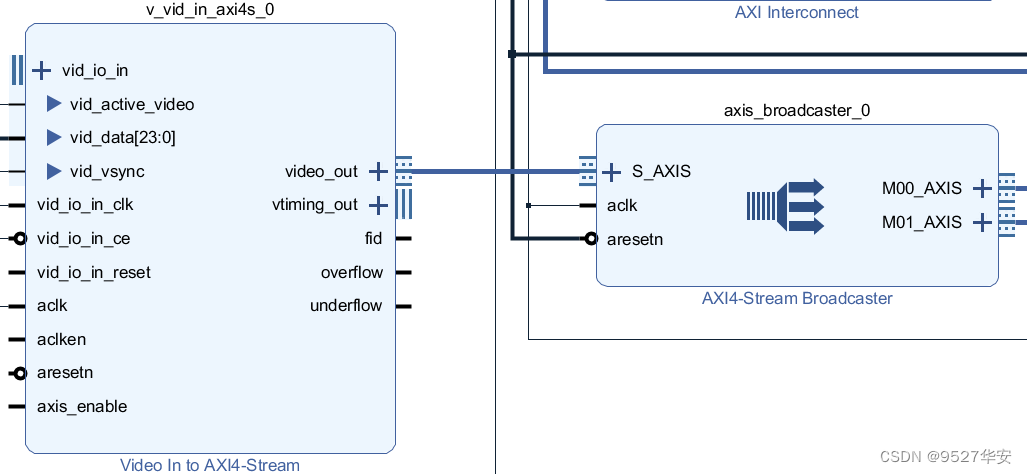

RGB视频流转AXI4-Stream

采集到的摄像头视频是RGB888视频流,调用Xilinx官方的Video In To AXI4-Stream IP核将RGB视频转换为AXI4-Stream视频流;后调用Xilinx官方的AXI4-Stream Broadcaster将AXI4-Stream视频流复制为2份,其中一份先经过Xilinx官方的VDMA缓存后读出,作为帧差算法的第一帧来源,另外一份和VDMA缓存后读出的AXI4-Stream视频流一起被送入帧差多目标识别跟踪算法模块;这里要将RGB888视频流转AXI4-Stream是因为需要用到Xilinx官方的VDMA图像缓存方案,VDMA的用户接口必须是AXI4-Stream;调用Video In To AXI4-Stream与AXI4-Stream Broadcaster如下:

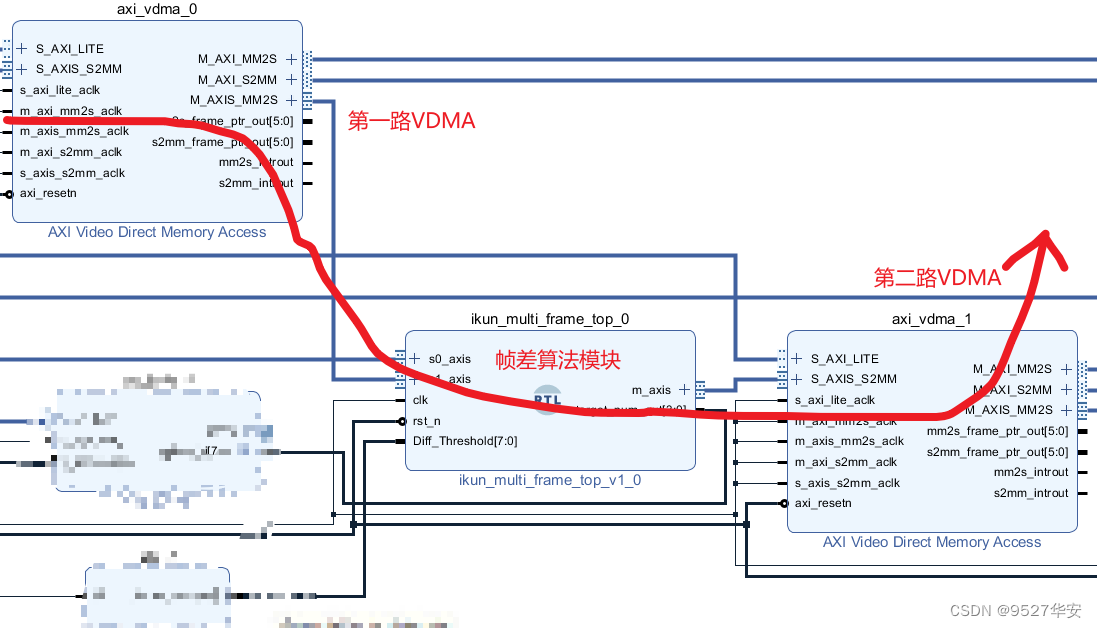

VDMA图像缓存

这里需要调用两路VDMA,一路用于缓存第一帧视频,作为帧差算法的第一帧来源,经过帧差算法后再调用第二路VDMA,用于缓存后输出图像,架构如下:

多目标帧差算法图像识别+目标跟踪模块

该模块具体性能表现如下:

1:支持多个运动目标识别跟踪,最多支持16个目标;

2:代码精简,集成度高;

3:时序收敛,稳定性强;

4:参数化配置,可在parameter参数中配置图像分辨率;

5:用户接口为AXI4-Stream,方便与Xilinx系列FPGA对接;

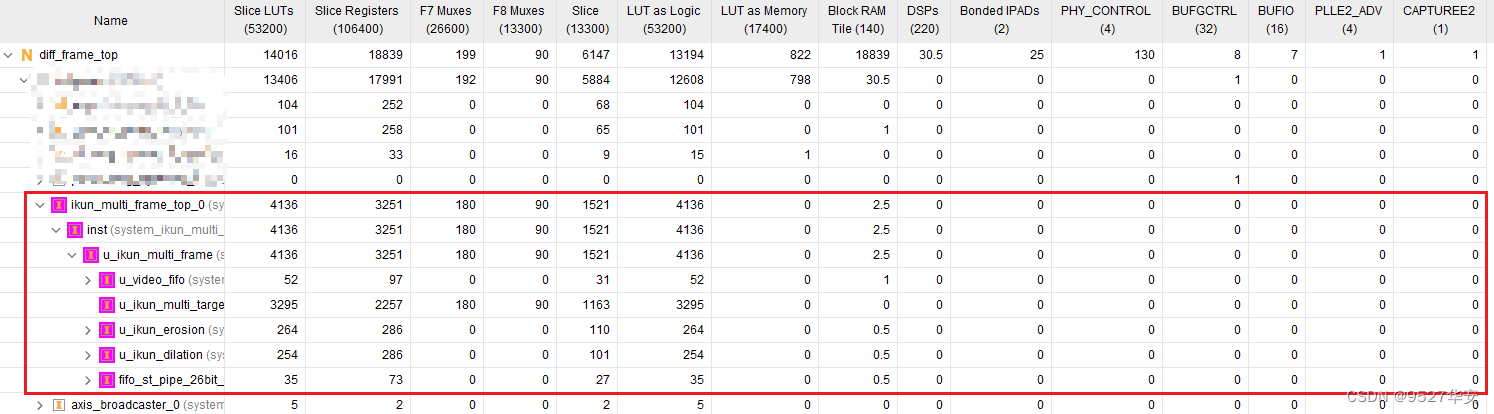

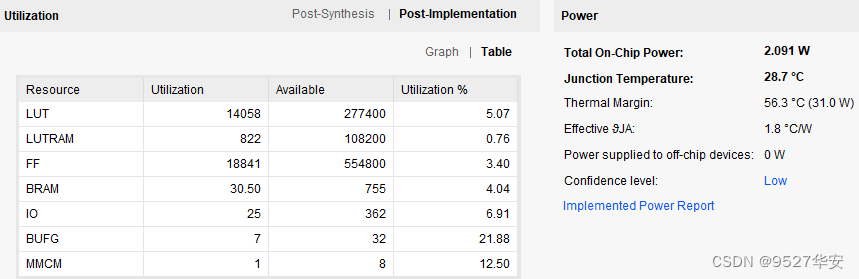

6:资源占用很小,如下:

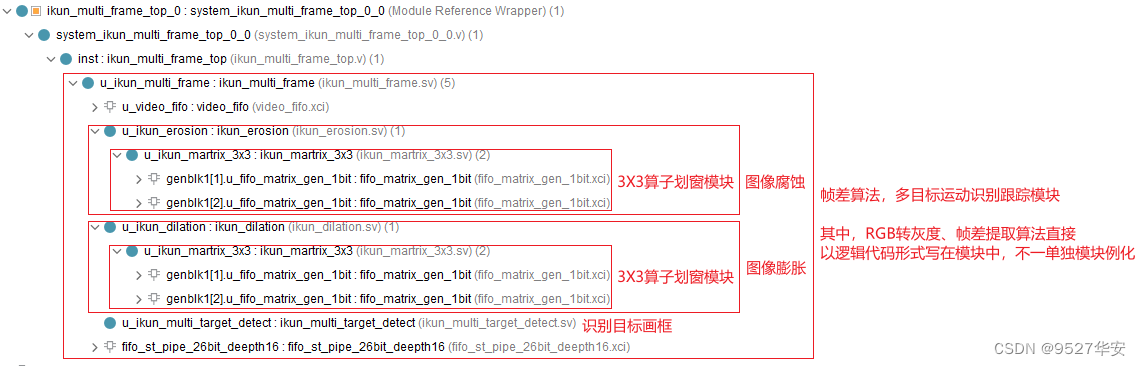

该模块是整个工程的核心,是一个集成设计模块,包含了RGB转灰度、帧差提取、图像腐蚀、图像膨胀、多目标识别标记等模块,最后输出用红框标记的运动目标图像;模块代码架构如下:

该模块有两个用户接口用户控制,如下:

input [ 7:0] Diff_Threshold , //帧差阈值,默认75 output [ 3:0] target_num_out , //最终目标数目

其中:

Diff_Threshold为帧差阈值,默认75 ,工程里通过一个VIO进行动态配置,正常情况下不需要配置;

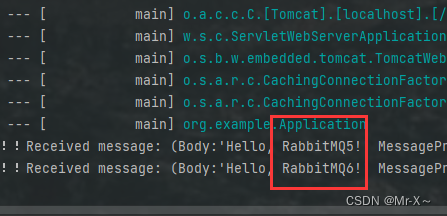

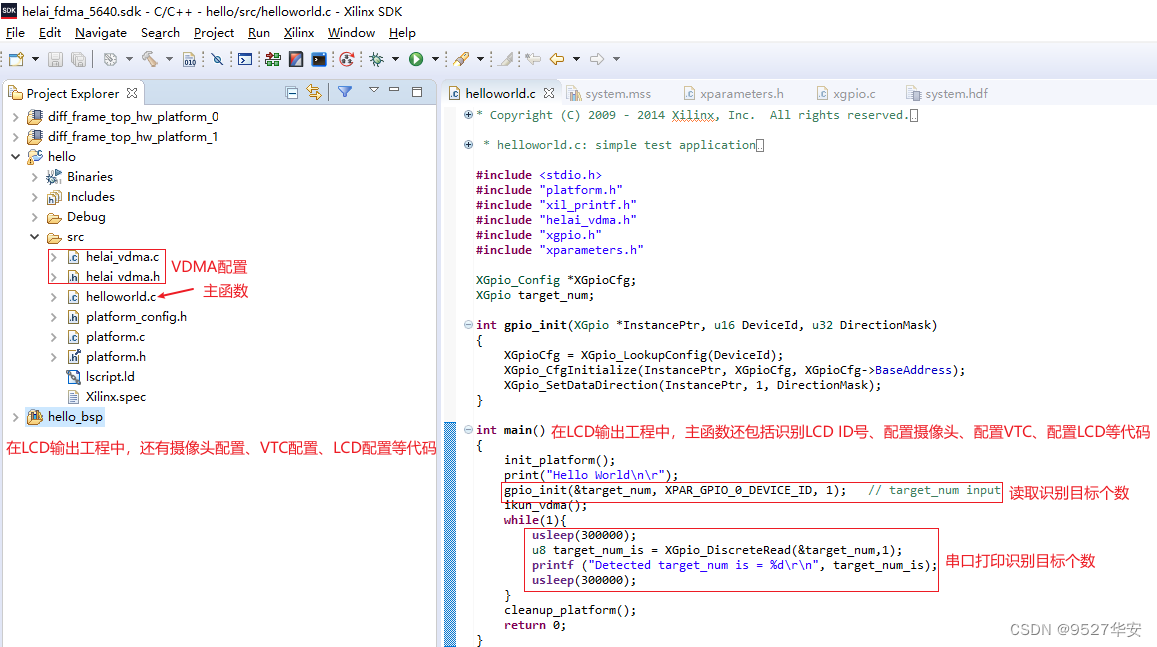

target_num_out 为最终识别到的目标个数,输出给用户查看,工程里通过一个AXI GPIO对该接口进行采集,并在SDK代码里通过串口打印输出该数值给用户查看,也就是说,串口会实时打印识别到的运动目标个数,在SDK软件代码的while()死循环中,设置的是300ms打印一次;

视频输出

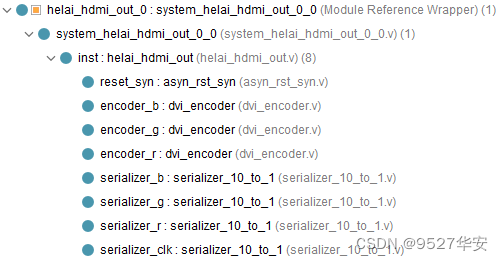

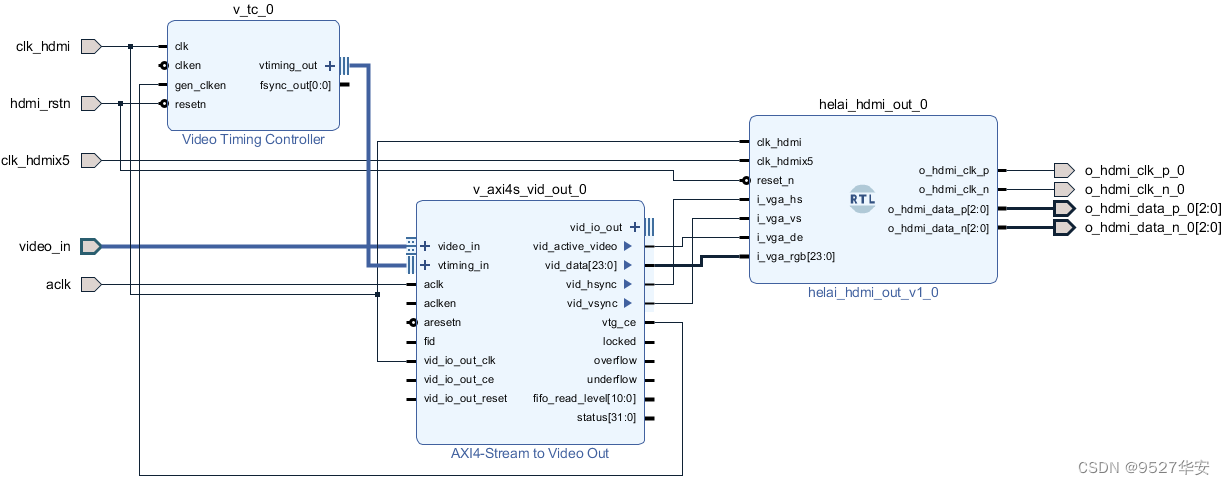

采用Xilinx官方经典的Video Timing Controller+AXI4-Stream To Video Out方案,其中Video Timing Controller IP核为输出系统提供标准的VGA时序,AXI4-Stream To Video Out IP核将AXI4-Stream视频流转换为RGB视频流;最终的输出接口采用了HDMI或者LCD方案,用户根据自己的硬件情况选择哪一种;HDMI输出采用纯verilog编码实现的RGB转HDMI模块,代码架构如下,LCD方案与之类似:

工程中将Video Timing Controller、AXI4-Stream To Video Out、HDMI输出集成到了一起做了模块封装,如下,LCD输出方案则没有封装:

注意!!

由于LCD显示方案为了适应不同分辨率的LCD显示屏,Video Timing Controller采用了动态配置方案,通过SDK软件代码根据识别到的LCD分辨率做动态调整,该方案通过AXI4_Lite接口动态配置MMCM源语的寄存器,与DRP接口配置效果一样;该方案有漂亮国某知名高校研发推广,被国内各大友商采用。。。

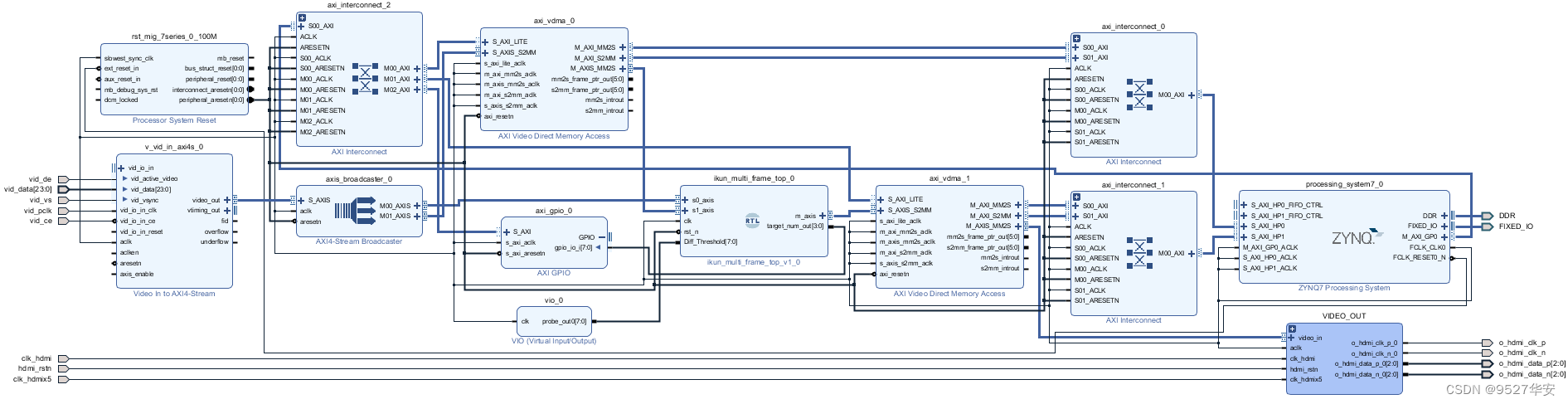

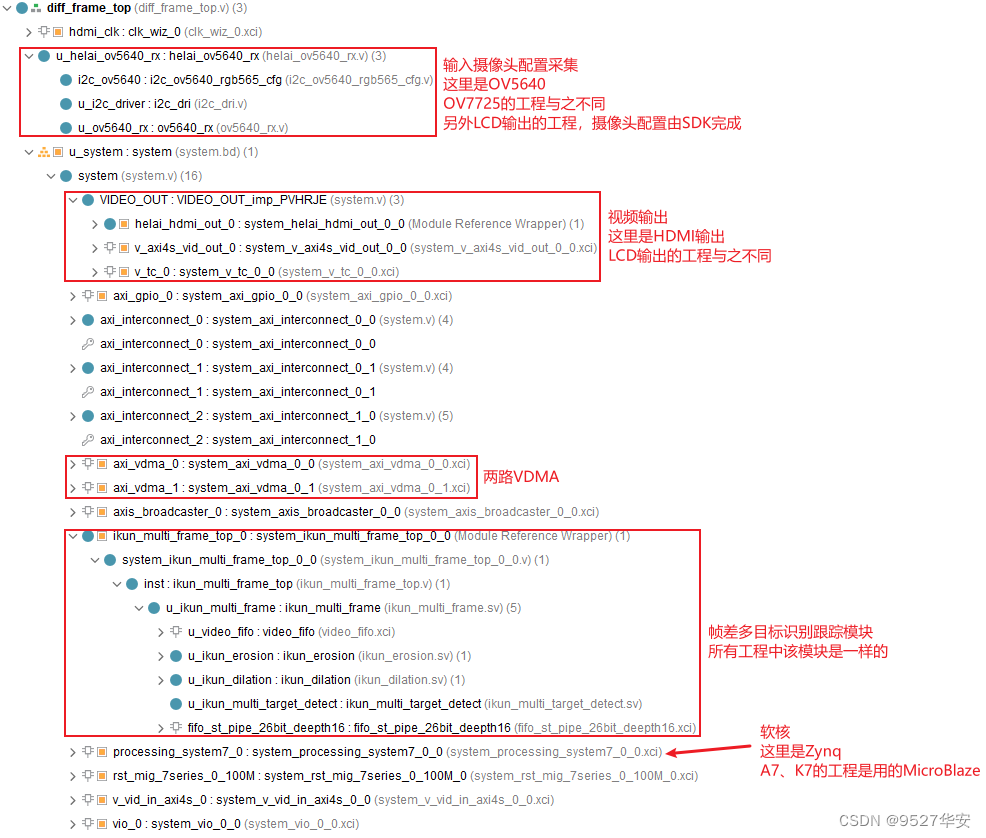

Xilinx系列FPGA工程源码架构

Xilinx系列FPGA工程源码架构由两部分组成,一是Block Design搭建的PL端FPGA逻辑设计,二是由SDK搭建的PS端软件设计;PL端FPGA逻辑设计主要负责视频采集、算法、视频输出等部分工作;PS端软件设计主要负责各种IP初始化、配置等部分工作;

以工程7为例,Block Design设计如下,其他工程与之类似:

综合后的RTL代码架构如下:

以工程7为例,SDK软件设计如下,其他工程与之类似:

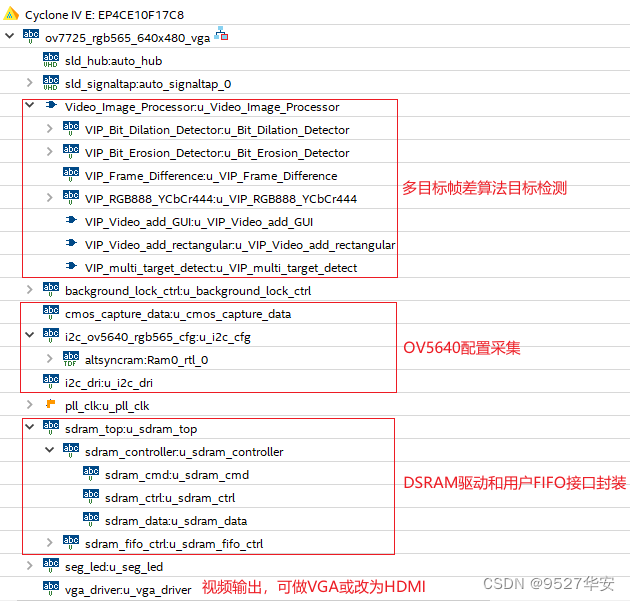

Altera系列FPGA工程源码架构

Altera系列FPGA工程源码架构如下:

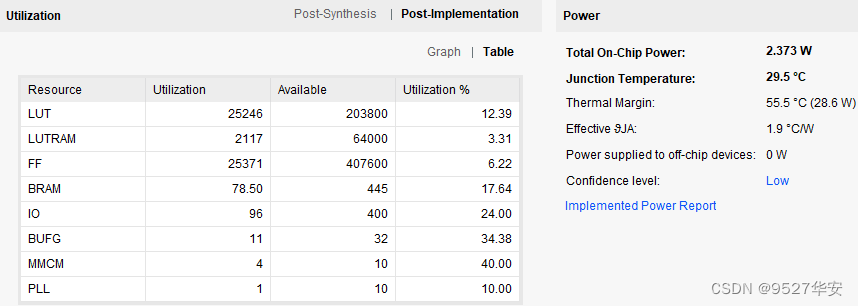

4、工程代码1详解–>OV5640输入HDMI输出,Xilinx–Artix7版本

开发板FPGA型号:Xilinx–Artix7–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率1280x720@30Hz;

输出:HDMI,纯verilog编码,分辨率1280x720@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

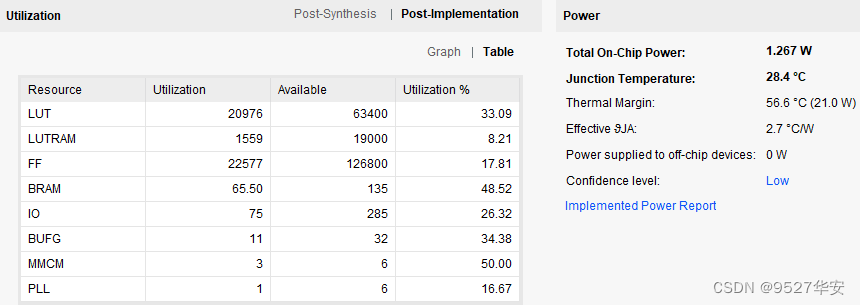

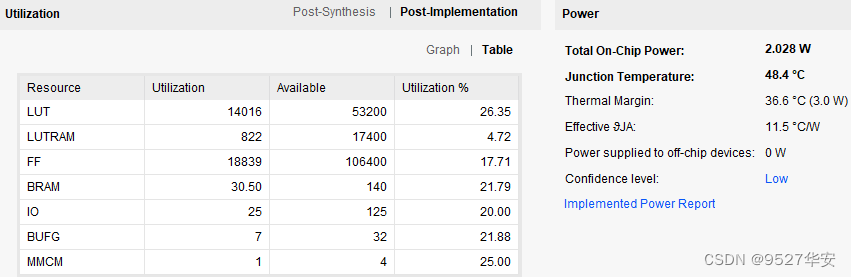

工程的资源消耗和功耗如下:

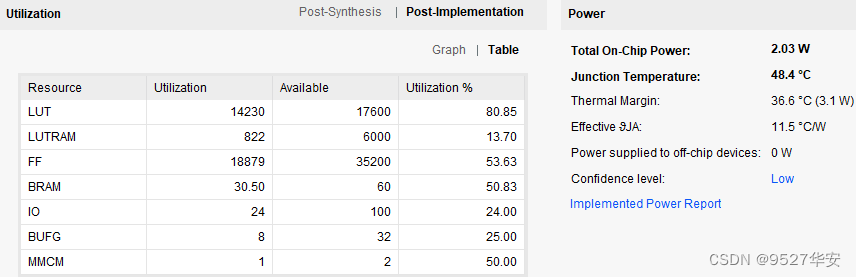

5、工程代码2详解–>OV5640输入HDMI输出,Xilinx–Kintex7版本

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率1280x720@30Hz;

输出:HDMI,纯verilog编码,分辨率1280x720@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

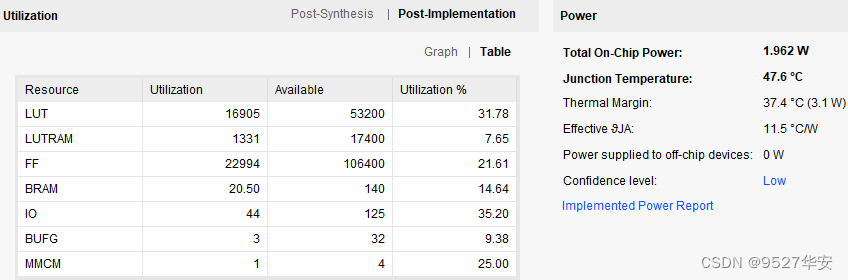

工程的资源消耗和功耗如下:

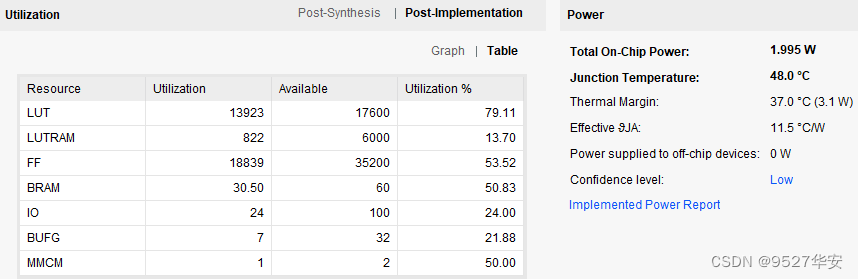

6、工程代码3详解–>OV5640输入HDMI输出,Xilinx–Zynq7010版本

开发板FPGA型号:Xilinx–Zynq7010–xc7z010clg400-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率1280x720@30Hz;

输出:HDMI,纯verilog编码,分辨率1280x720@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

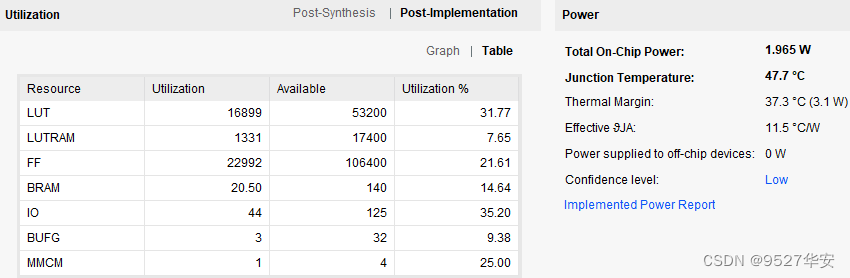

工程的资源消耗和功耗如下:

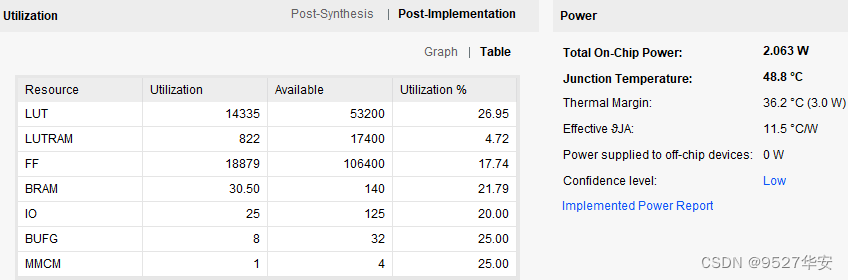

7、工程代码4详解–>OV7725输入HDMI输出,Xilinx–Zynq7010版本

开发板FPGA型号:Xilinx–Zynq7010–xc7z010clg400-2;

开发环境:Vivado2019.1;

输入:OV7725摄像头,分辨率640x480@60Hz;

输出:HDMI,纯verilog编码,分辨率640x480@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

工程的资源消耗和功耗如下:

8、工程代码5详解–>OV5640输入HDMI输出,Xilinx–Zynq7020版本

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率1280x720@30Hz;

输出:HDMI,纯verilog编码,分辨率1280x720@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

工程的资源消耗和功耗如下:

9、工程代码6详解–>OV7725输入HDMI输出,Xilinx–Zynq7020版本

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV7725摄像头,分辨率640x480@60Hz;

输出:HDMI,纯verilog编码,分辨率640x480@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

工程的资源消耗和功耗如下:

10、工程代码7详解–>OV5640输入LCD输出,Xilinx–Zynq7020版本

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率800x480@30Hz;

输出:4.3寸LCD屏,纯verilog编码,分辨率800x480@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

工程的资源消耗和功耗如下:

11、工程代码8详解–>OV7725输入LCD输出,Xilinx–Zynq7020版本

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV7725摄像头,分辨率640x480@60Hz;

输出:4.3寸LCD屏,纯verilog编码,分辨率800x480@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

工程的资源消耗和功耗如下:

12、工程代码9详解–>OV5640输入HDMI输出,Xilinx–Zynq7100版本

开发板FPGA型号:Xilinx–Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率1280x720@30Hz;

输出:HDMI,纯verilog编码,分辨率1280x720@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

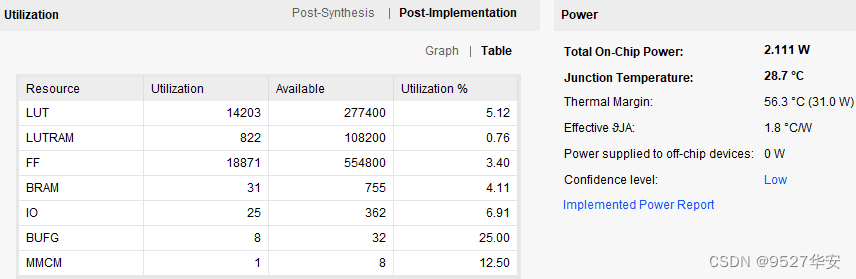

工程的资源消耗和功耗如下:

13、工程代码10详解–>OV7725输入HDMI输出,Xilinx–Zynq7100版本

开发板FPGA型号:Xilinx–Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:OV7725摄像头,分辨率640x480@60Hz;

输出:HDMI,纯verilog编码,分辨率640x480@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Xilinx系列FPGA工程源码架构》小节内容;

工程的资源消耗和功耗如下:

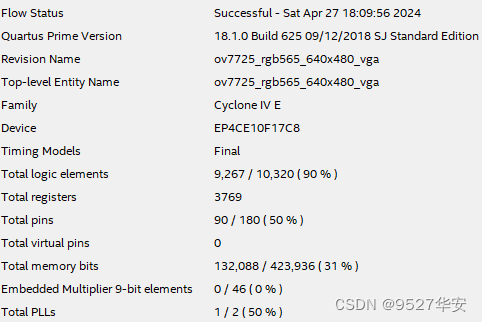

14、工程代码11详解–>OV5640输入HDMI输出,Altera–Cyclone IV版本

开发板FPGA型号:Altera–Cyclone IV–EP4CE10F17C8;

开发环境:Quartus (Quartus Prime 18.1) ;

输入:OV5640摄像头,分辨率640x480@60Hz;

输出:HDMI,纯verilog编码,分辨率640x480@60Hz;

图像处理:帧差算法多目标图像识别+目标跟踪;

工程作用:掌握FPGA帧差算法多目标图像识别+目标跟踪的设计方法;

工程Block Design和工程代码架构请参考第3章节《Altera系列FPGA工程源码架构》小节内容;

工程的资源消耗和功耗如下:

15、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

16、上板调试验证并演示

准备工作

需要如下器材设备:

1、FPGA开发板;

2、OV5640或OV7725摄像头;

2、HDMI连接线和显示器;

OV5640输入版本工程演示

工程1、2、3、5、7、9、11使用OV5640输入,帧差算法多目标图像识别+目标跟踪输出效果如下:

OV5640输入FPGA帧差算法多目标图像识别+目标跟踪

OV7725输入版本工程演示

工程4、6、8、10使用OV5640输入,帧差算法多目标图像识别+目标跟踪输出效果如下:

OV7725输入FPGA帧差算法多目标图像识别+目标跟踪

LCD显示屏输出版本工程演示

工程7、8使用LCD显示屏输出效果如下:

FPGA帧差算法多目标图像识别+目标跟踪LCD输出

17、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

![[1688]jsp工资投放管理系统Myeclipse开发mysql数据库web结构java编程计算机网页项目](https://img-blog.csdnimg.cn/direct/195fc40685b24f6dba108d6f0e9bcf71.png)