系列文章目录

文章目录

- 系列文章目录

- 前言

- Qsys

- Nios II

- hello world 实例

- Platform Design

- Nios II程序设计

前言

利用Quartus中的Qsys工具,可以实现在FPGA里面跑嵌入式的功能

Qsys

Altera 公司将主控制器、数字信号处理模块、存储器及其控制模块、各种接口协议等模块,通过硬件描述语言实现并封装成 IP 核。 用户可以在 Qsys 中直接调用这些 IP 核,从而节省了自己去Verilog编程的时间。

Qsys可以重构SoC(System on Chip, 片上系统),可以增减构成系统的 IP核或修改已有 IP 核的参数。

SOPC( System On a Programmable Chip, 也就是可编程片上系统)

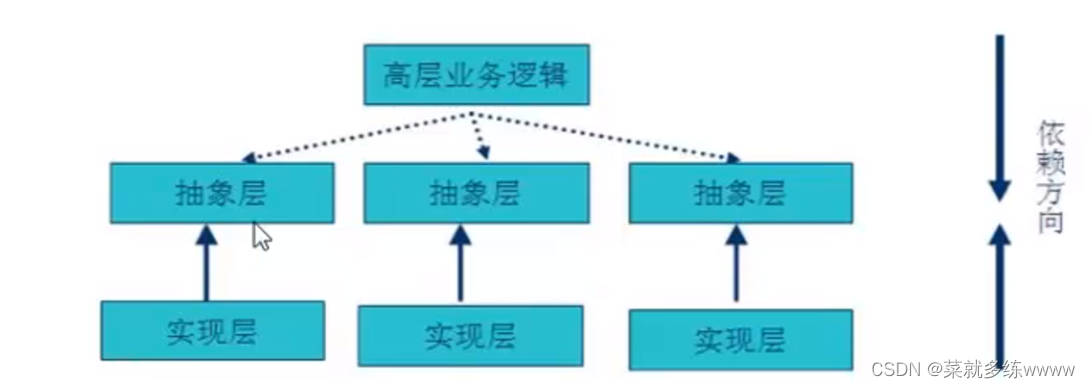

Qsys 即Platform Designer,用Qsys来创建硬件环境,不同于 ARM、单片机等处理器的固定硬件环境,通常是指以 Nios II 处理器为核心的嵌入式系统。

Nios II

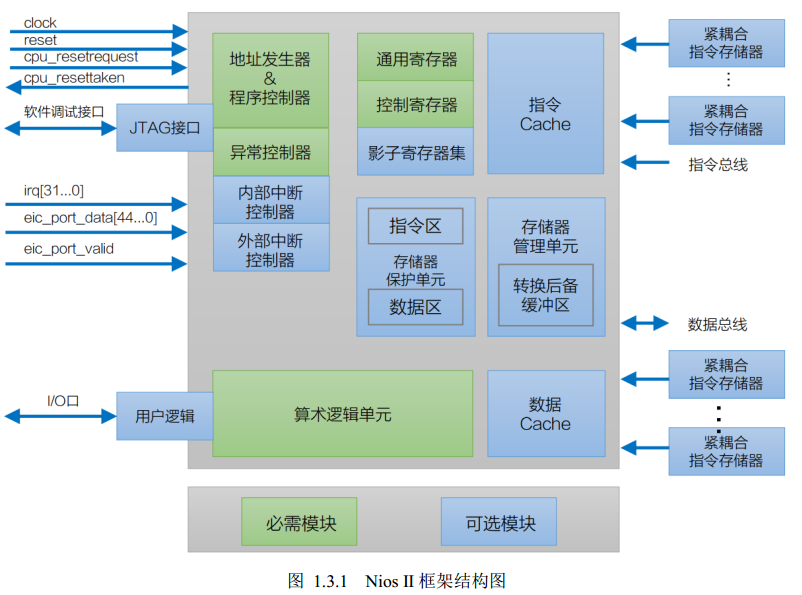

Nios II 是应用于 Intel FPGA 的嵌入式软核处理器,在一片 FPGA 内部构建多个 Nios II 处理器,它们可以作为主CPU,也可以是协处理器,在同一芯片内部协调有序地完成整个复杂系统的各项功能。32 位 RISC 架构(精简指令集架构) 处理器。

Nios II 处理器为用户提供了 Nios II/e(经济型) 、 Nios II/s(标准型) 、 Nios II/f(快速型) 三种内核,占用FPGA的资源依次增多,但运行速度也依次增强。

hello world 实例

Platform Design

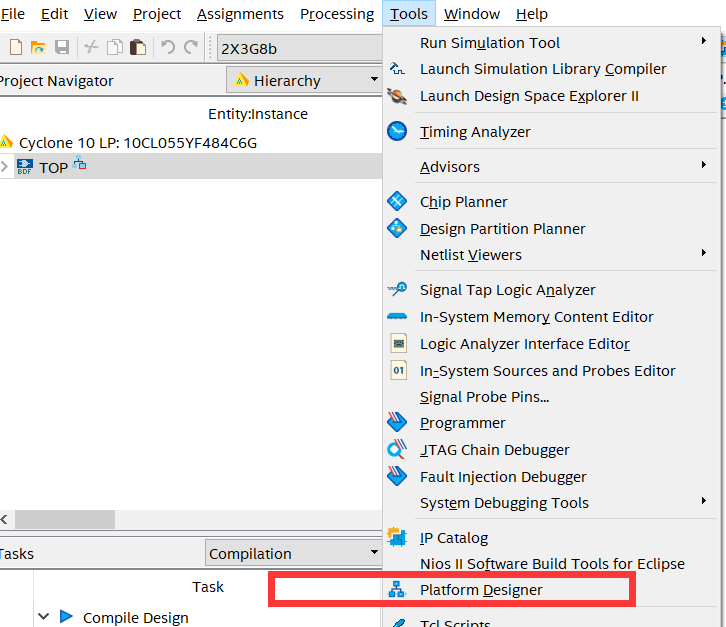

打开设计平台

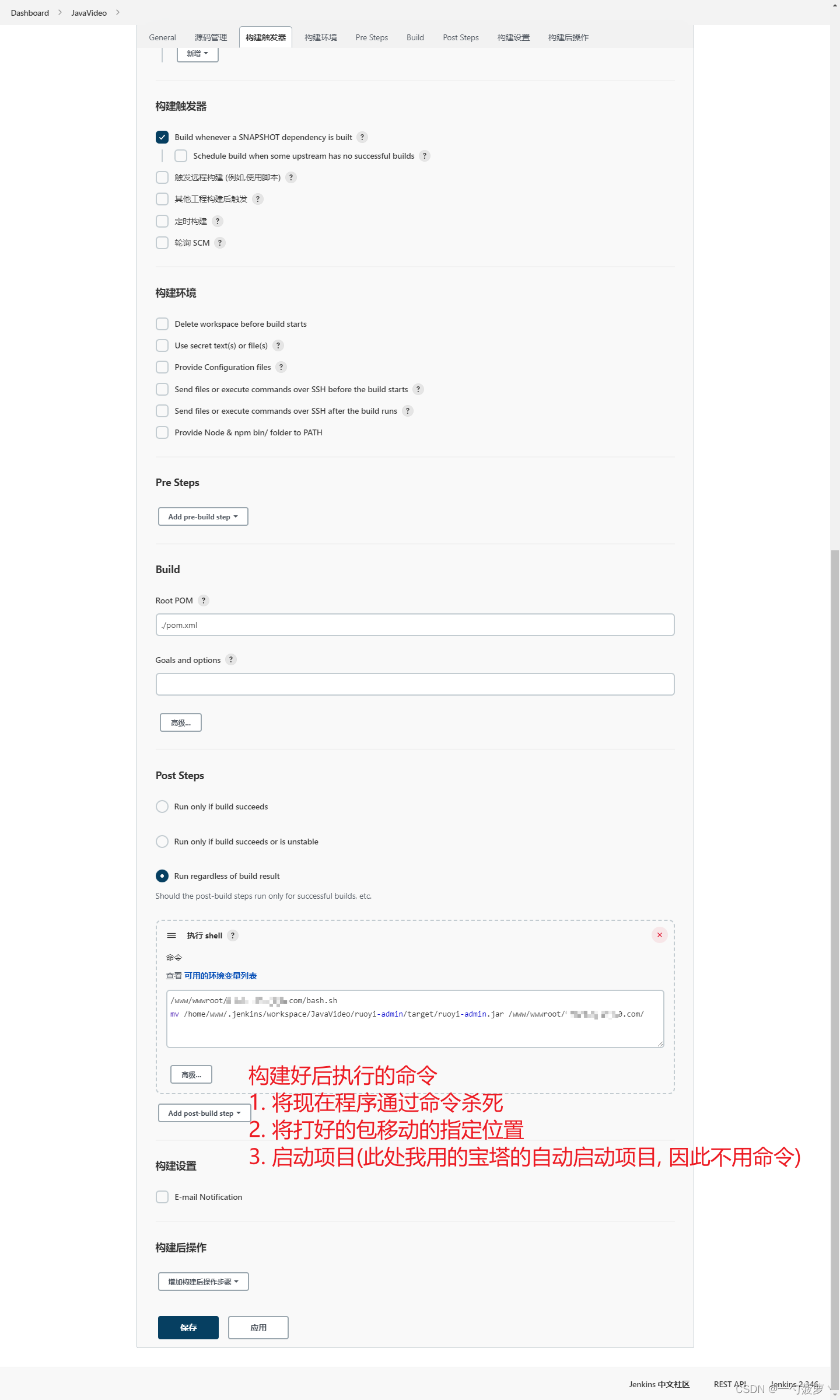

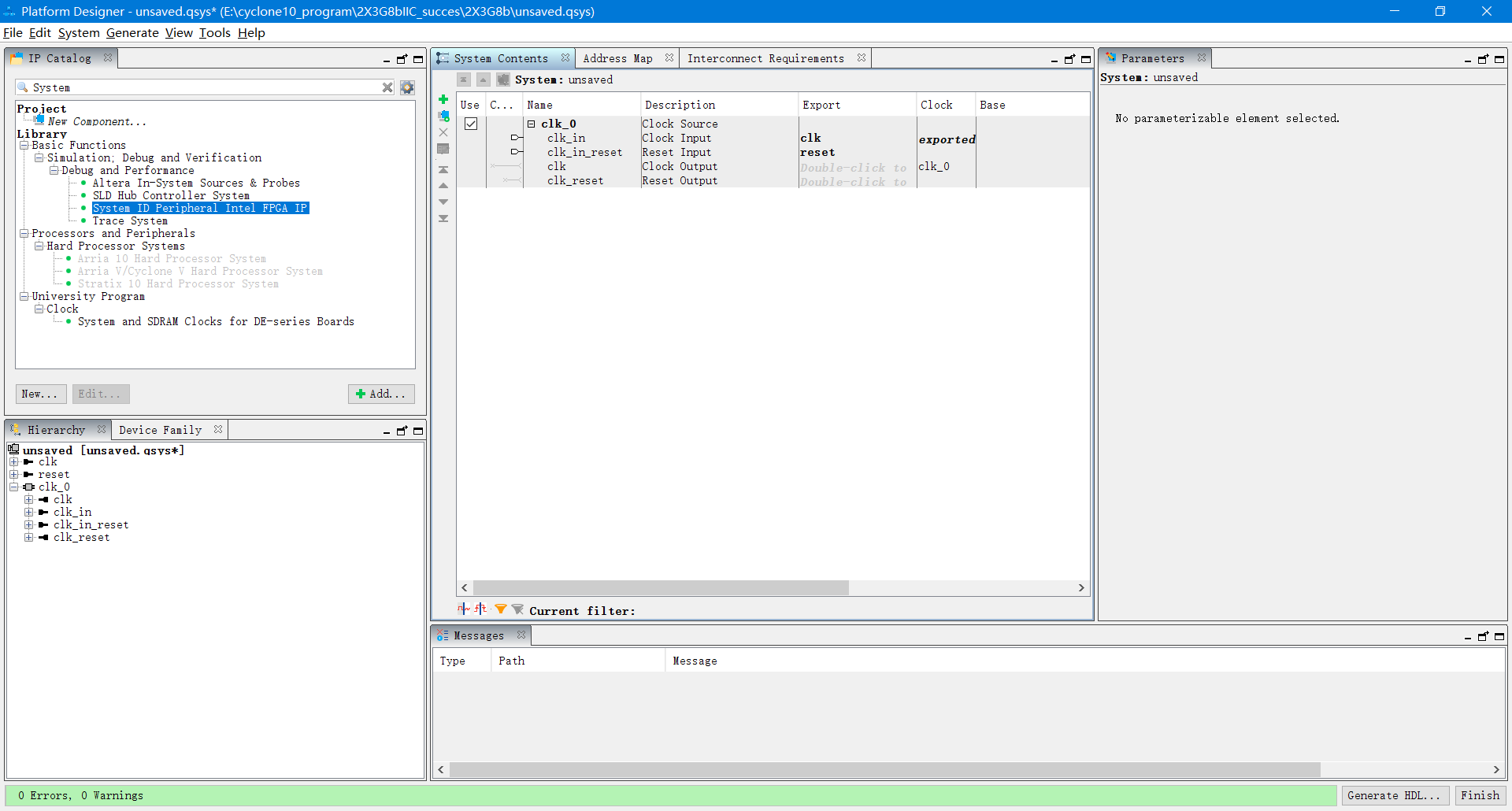

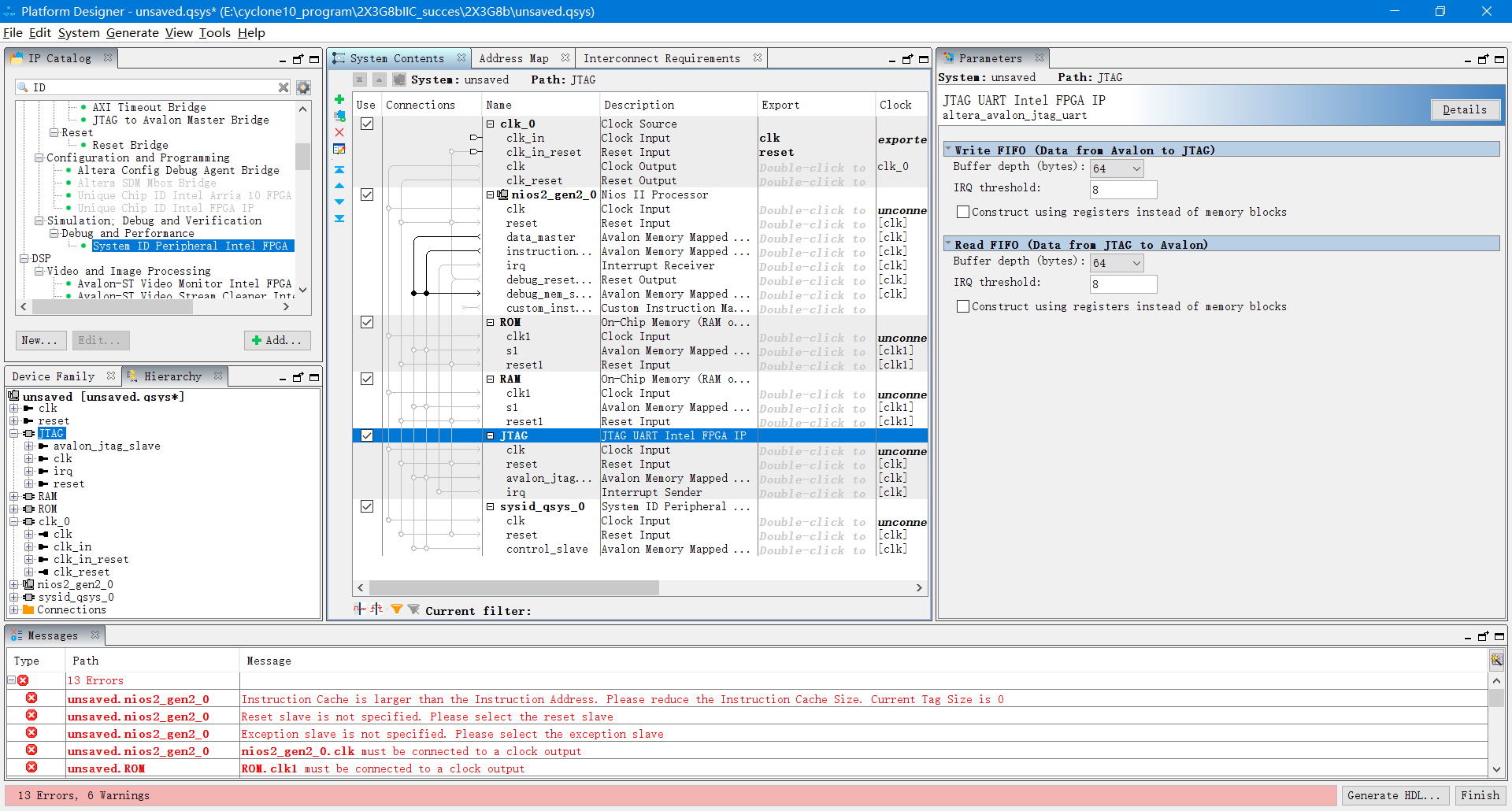

之后在左上角的IP Catalog界面搜索添加Nios II Processor、On-Chip Memory (设置为ROM,10240)、On-Chip Memory (设置为RAM,20480)、JTAG UART、System ID Peripheral。之后更改名字。

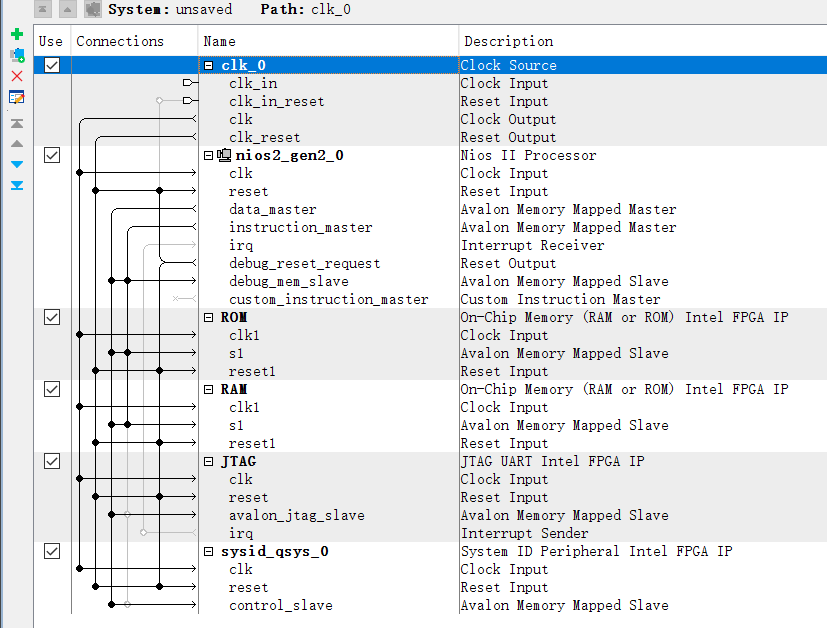

在“Connections”一栏中相应的结点,可以实现连线,连接后各结点处的空心圆会变成实心的点,同时相应的连线由浅灰色变成黑色。

按照这样的连接方式:

clk IP 核的时钟信号―clk‖和复位信号―clk_reset‖与其余的各个 IP 核都连接起来。

Nios II 处理器 IP 核的数据主端口data_master和指令主端口instruction_master:

数据主端口与所有的外设 IP 核连接

指令主端口只连接存储器 IP 核

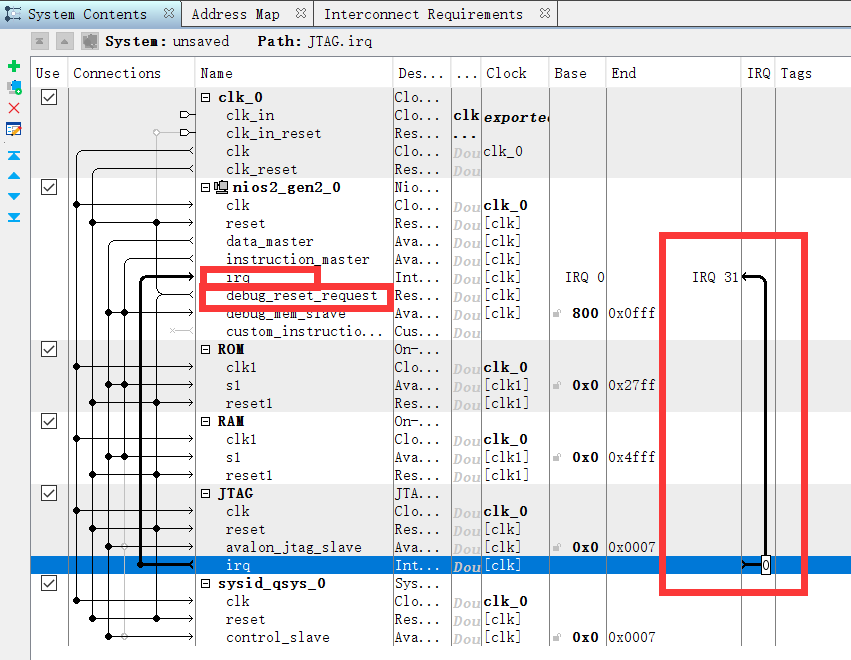

Nios II 处理器 IP 核的jtag_debug_module_reset信号:连接起来并在“IRQ”一栏将 jtag_uartIP 核的中断信号与 Nios II 处理器连接起来。

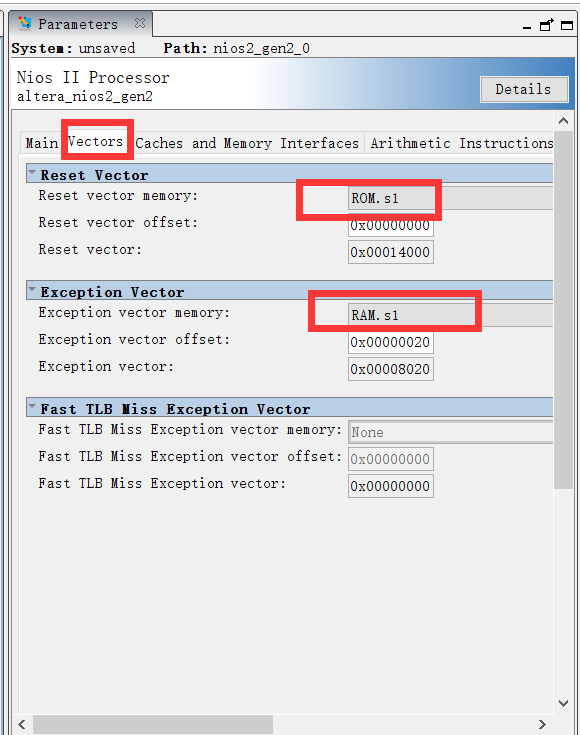

设置NIOS的IP核,在Vector一栏中,指定复位地址(ResetVector) , 一般我们选择使用非易失性存储器来存储复位代码。复位地址是由所选存储器的基地址和偏移地址“Reset vector offset”共同计算出来的。

在“Exception Vector”一栏我们需要指定存储异常处理代码的存储器, 同时指定异常地址。 一般我们选择读写速度较快的存储器(多数为易失性存储器) 用来存储异常处理代码,异常地址是同样是由所选存储器的基地址和偏移地址“Exception vectoroffset”共同计算出来的,在异常事件发生时,程序从异常地址开始运行。

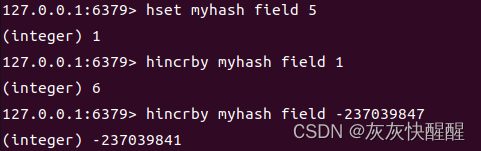

然后,我们进入基地址分配阶段。点击菜单栏中的【System】→【Assign Base Addresses】, Qsys 工具会自动为各个 IP 核分配基地址。 之后generate生成就行了。

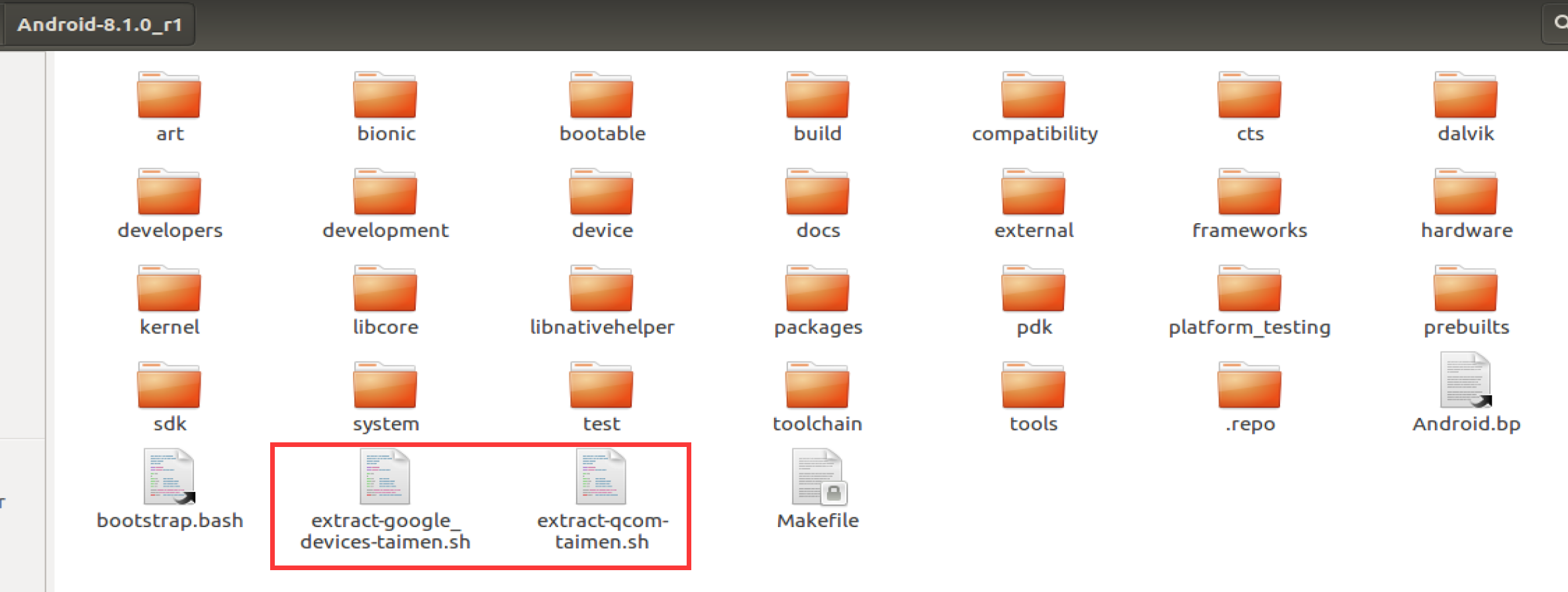

之后把生成的qip文件添加了项目中:

Unused Pins, 设置为高阻输入(As inputtri-state)

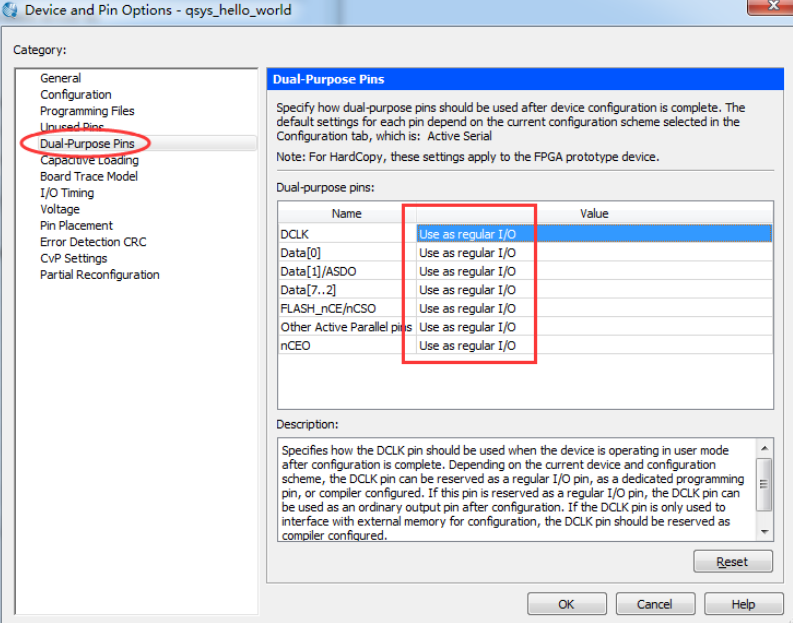

Dual-Purpose Pins,全部设置为 Use asregular I/O ,这个不太明白是啥意思

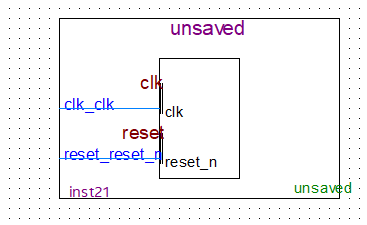

之后就可以调用:(名字忘记改了),然后给他一个设置频率所对应的时钟核复位,编译

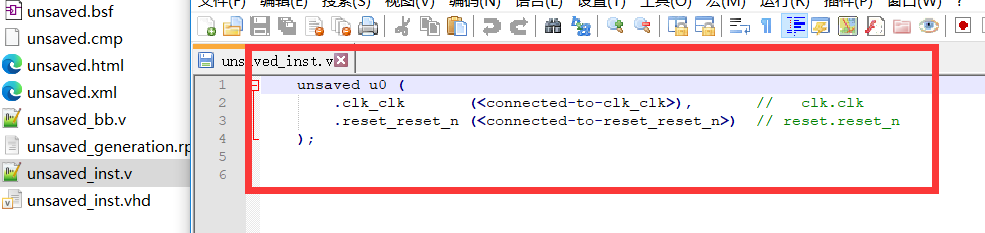

在生成的文件中可以查看verilog例化代码

Nios II程序设计

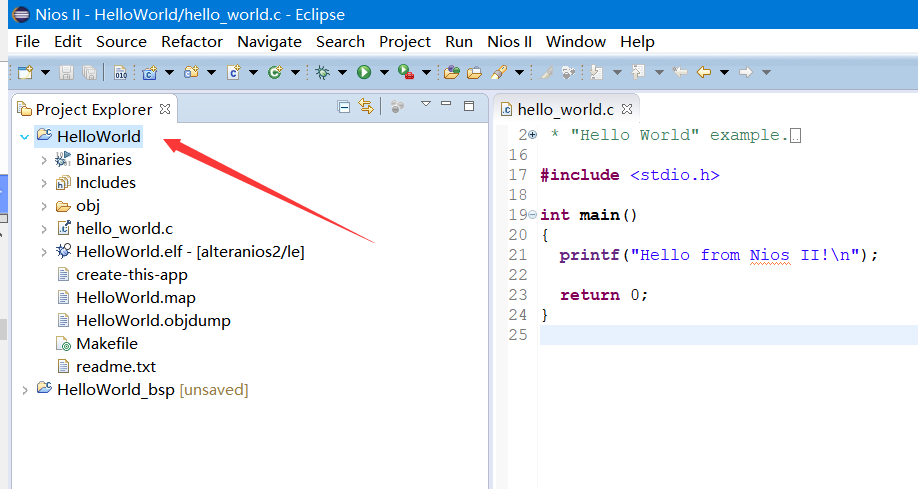

Quartus II 软件菜单栏中的【Toos】中的【Nios II SBT for Eclipse】

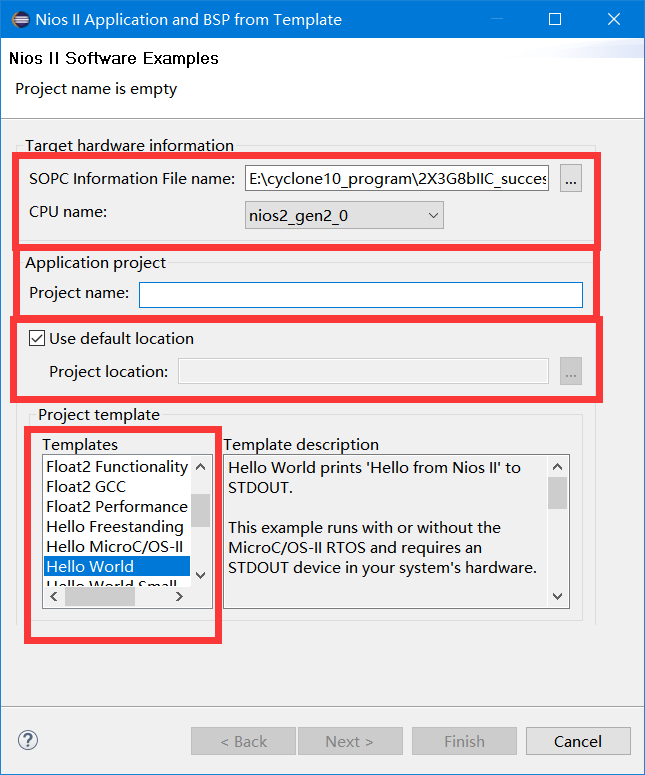

单击菜单栏中的【File】→【New】→【Nios II Application and BSP from Template】来新建 Nios II 工程

在第一栏中,选择我们利用Platform Design生成的.sopcinfo文件,之后CPU name会自动识别,这里可以命名项目核路径,默认会与.sopcinfo生成在一个路径下,生成一个software文件,最下方可以选择项目模板。

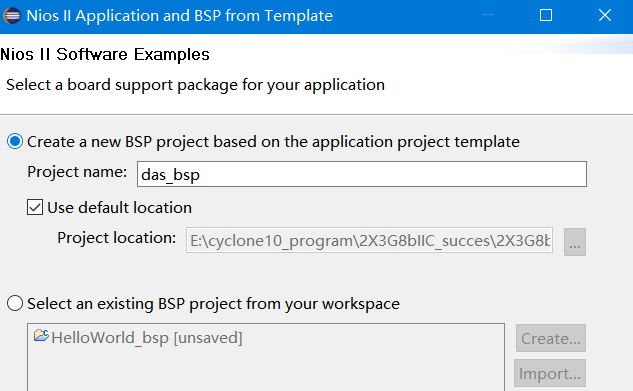

next之后,可以看到工具会自动创建板级支持包BSP(Board Support Package)

对项目,右键,build project,发现有报错,显示RAM容量不够,但我们分配了20KB的

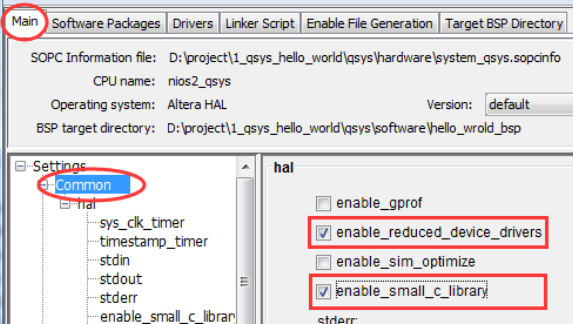

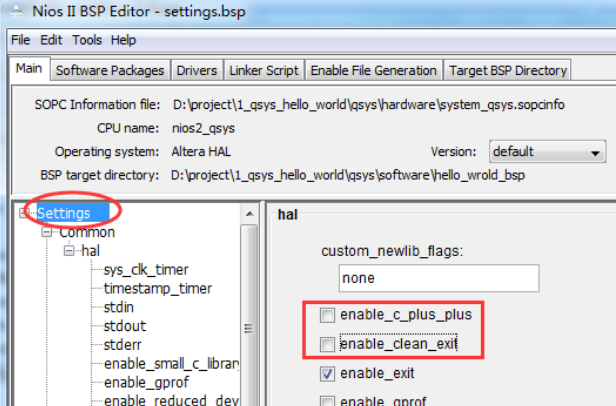

右键项目,选择【Nios II】→【BSP Editor】,会出现Nios II BSP Editor界面

勾选:

取消勾选:

enable_reduced_device_drivers: BSP 为处理器的外设提供了两个版本的驱动库:一种是执行速度快,但代码量比较大的版本;另一种是封装小的版本 。默认使用的大代码量的,通过选项可以选另一种。

enalbe_small_c_library:完整的 ANSIC 标准库通常不适用于嵌入式系统, BSP 提供了一系列经过裁剪的 ANSI C 标准库,占用资源比较少,我们可以通过【enalbe_small_c_library】选项来选择精简的 ANSI C标准库。

enable_c_plus_plus: 我们使用 C 语言来编写软件程序,因此不需要使能 C++。

enable_clean_exit:当选中该选项时,系统库在主函数 main()返回时会调用 exit()。调用 exit()时,首先会清理 I/O 的缓冲区,然后再调用_exit()。当不选中该选项时,系统库会只调用_exit(),这样将会节省程序空间。对于嵌入式系统程序来说,一般都不会从 main()返回,所以可以不勾选该选项。

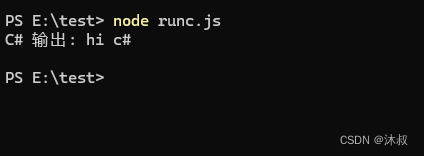

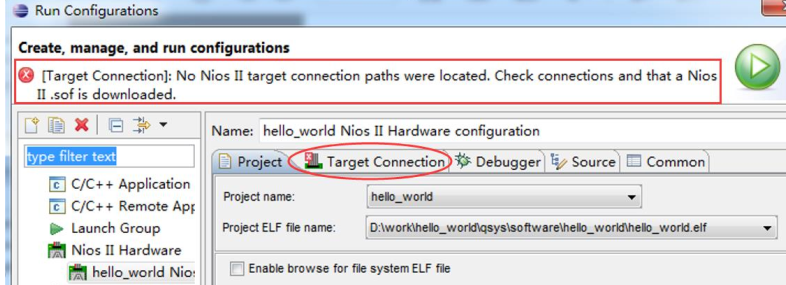

之后就可以下载程序了,先下载.sof文件,之后右键工程,然后点击【Run As】→【Nios II Hardware】

在“Target Connection‖标签页中点击【Refresh Connections】按钮, 这时软件便会自动识别我们开发板上的 Qsys 系统,并显示 Qsys 系统的相关信息。我们接着点击【Apply】→【Run】

在软件下方的Nios II Console中会打印Hello,World信息,说明下载成功