目录

- 1.前言

- 2.浮点数的形式

- 3.举例说明

- 4.浮点数四则运算

微信公众号含更多FPGA相关源码:

1.前言

前面讲了定点表示法,定点表示法有一个主要的限制,那就是它不能有效地表示非常大或非常小的数,因为小数点的位置是固定的。为了解决这个问题,人们发明了浮点表示法,其中小数点的位置是浮动的,可以根据需要移动以表示不同大小的数。

2.浮点数的形式

浮点数制可以在更大的动态范围内提供更高的分辨率,通常当定点数由于受其精度和动态范围所限不能胜任时,浮点数就能够为之提供解决方案。当然,同时也在速度和复杂程度方面带来了损失,大多数浮点数制都遵循单精度或者双精度的IEEE浮点数标准。标准浮点数字长由一个符号位S、指数e和无符号(小数)的规格化尾数m构成。其格式如下:

| 符号位 | 指数 | 无符号尾数 |

|---|---|---|

| S | e | m |

浮点数字长的代数表达式如下:

X = ( − 1 ) S × 1. m × 2 e − b i a s X=(-1)^S \times 1.m \times2^{e-bias} X=(−1)S×1.m×2e−bias

IEEE单精度和双精度格式的其他参数请参阅下表。

IEEE 浮点数标准:

| 单 精 度 | 双 精 度 | |

|---|---|---|

| 字长 | 32 | 64 |

| 尾数 | 23 | 52 |

| 指数 | 8 | 11 |

| 编移 Bias | 127 | 1023 |

| 范围 | 2 138 = 3.8 × 1 0 38 2^{138}=3.8\times10^{38} 2138=3.8×1038 | 2 1024 9 × 1 0 307 2^{1024}~9\times10^{307} 21024 9×10307 |

根据国际标准 IEEE 754,任意一个二进制浮点数 X 可以表示成下面的形式:

X = ( − 1 ) S × m × 2 e X=(-1)^S \times m \times2^e X=(−1)S×m×2e

其中, ( − 1 ) s (-1)^s (−1)s表示符号位,当 s = 0 , X s=0,X s=0,X为正数;当 s = 1 , X s=1,X s=1,X为负数。

M表示有效数字,大于等于1,小于2。

2 e 2^e 2e表示指数位。

3.举例说明

举例来说,十进制的 5.0,写成二进制是 101.0,相当于 1.01×2^2。那么,按照上面 V 的格式,可以得出 s=0,M=1.01,E=2。

十进制的 - 5.0,写成二进制是 - 101.0,相当于 - 1.01×2^2。那么,s=1,m=1.01,e=2。

IEEE 754 规定,对于 32 位的浮点数,最高的 1 位是符号位 s,接着的 8 位是指数 e,剩下的 23 位为有效数字 m。

对于 64 位的浮点数,最高的 1 位是符号位 S,接着的 11 位是指数 e,剩下的 52 位为有效数字 m。

IEEE 754 对有效数字 m 和指数 e,还有一些特别规定。

前面说过,1≤m<2,也就是说,m 可以写成 1.xxxxxx 的形式,其中 xxxxxx 表示小数部分。IEEE 754 规定,在计算机内部保存 m 时,默认这个数的第一位总是 1,因此可以被舍去,只保存后面的 xxxxxx 部分。比如保存 1.01 的时候,只保存 01,等到读取的时候,再把第一位的 1 加上去。这样做的目的,是节省 1 位有效数字。以 32 位浮点数为例,留给 m 只有 23 位,将第一位的 1 舍去以后,等于可以保存 24 位有效数字。

至于指数 E,情况就比较复杂。首先,e 为一个无符号整数 (unsigned int)。这意味着,如果 e 为 8 位,它的取值范围为 0255;如果 e 为 11 位,它的取值范围为 02047。但是,我们知道,科学计数法中的 e 是可以出现负数的,所以 IEEE 754 规定,e 的真实值必须再减去一个中间数,对于 8 位的 E,这个中间数是 127;对于 11 位的 e,这个中间数是 1023。

比如,2^10 的 e 是 10,所以保存成 32 位浮点数时,必须保存成 10+127=137,即 10001001。

然后,指数 e 还可以再分成三种情况:

(1) e 不全为 0 或不全为 1。这时,浮点数就采用上面的规则表示,即指数 e 的计算值减去 127 (或 1023),得到真实值,再将有效数字 m 前加上第一位的 1。

(2) e 全为 0。这时,浮点数的指数 e 等于 1-127 (或者 1-1023),有效数字 m 不再加上第一位的 1,而是还原为 0.xxxxxx 的小数。这样做是为了表示 ±0,以及接近于 0 的很小的数字。

(3) e 全为 1。这时,如果有效数字 m 全为 0,表示 ± 无穷大 (正负取决于符号位 s);如果有效数字 M 不全为 0,表示这个数不是一个数 (NaN)。

4.浮点数四则运算

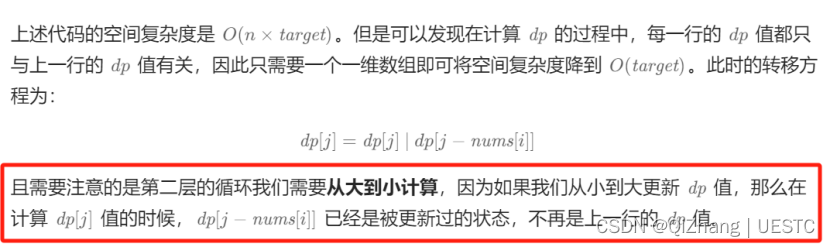

在浮点数乘法中,尾数部分可以像定点数一样相乘,而把指数部分析加。浮点数减法通常公更加复杂一些,这是因为首先要将尾数归一化,就是要将两个数都调整到较大的指数。然后再将两个尾数相加。对于加法和乘法混和运算来说,最终的归一化,就是将结果尾数再统一成小数1.m 形式的表达式,这是非常必要的。

微信公众号含更多FPGA相关源码: