1. 简介

VCS是编译型verilog仿真器,处理verilog的源码过程如下:

VCS先将verilog/systemverilog文件转化为C文件,在linux下编译链接生成可执行文件,在linux下运行simv即可得到仿真结果。

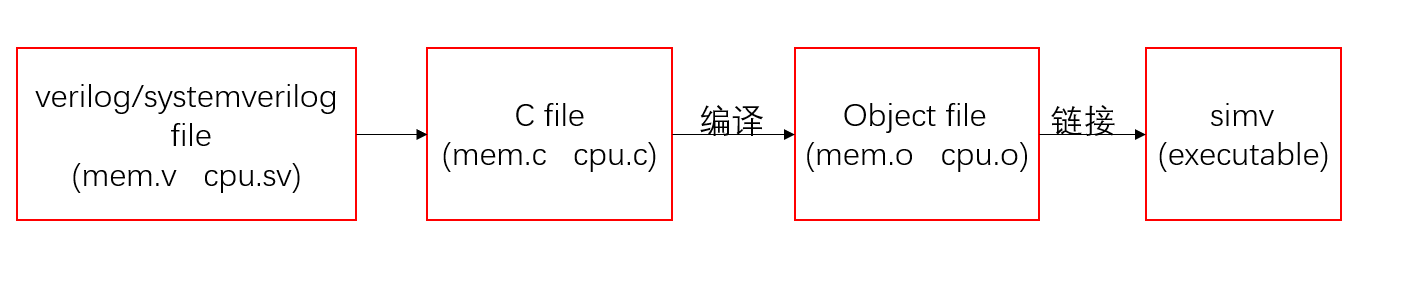

VCS使用步骤,先编译verilog源码,再运行可执行文件:

编译命令的格式:vcs sourcefile [compile_time_option] (编译选项用来控制编译过程)

执行仿真命令格式:./simv [run_time_option]

2. 示例

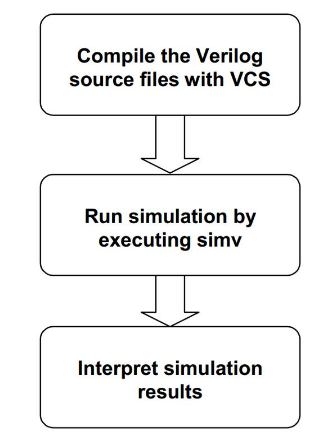

2.1. 电路结构图

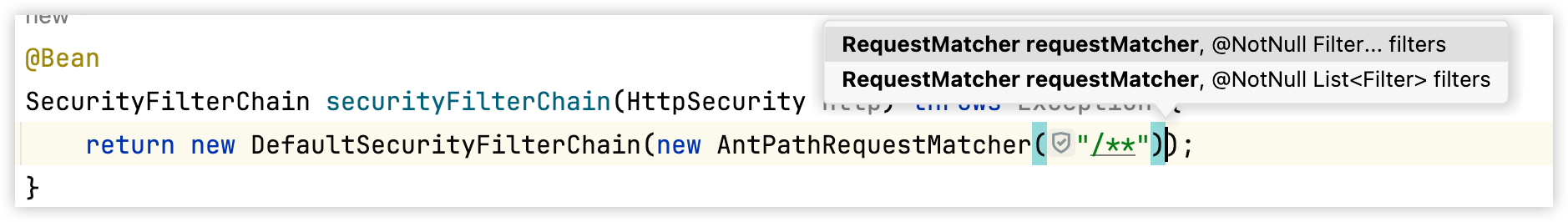

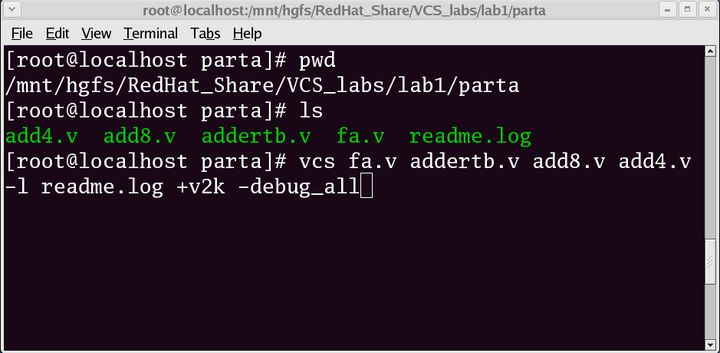

2.2. 编译

此电路为一位加法器 fa.v 组成4位加法器 add4.v,再组成一个8位加法器,使用资源换性能的思路,减小了行波进位加法器的进位延迟。顶层文件为add8.v,testbench为addertb.v。输入下图命令回车即可编译verilog文件,其中-l readme.log 用于将编译产生的信息放在log文件内,+v2k是使VCS兼容verilog 2001以前的标准。-debug_all用于产生debug所需的文件。

2.3. 仿真

./simv -l run.log 开始仿真,testbench里的$display打印仿真成功的信息,显示在终端上。使用-l run.log 记录终端上产生的信息。

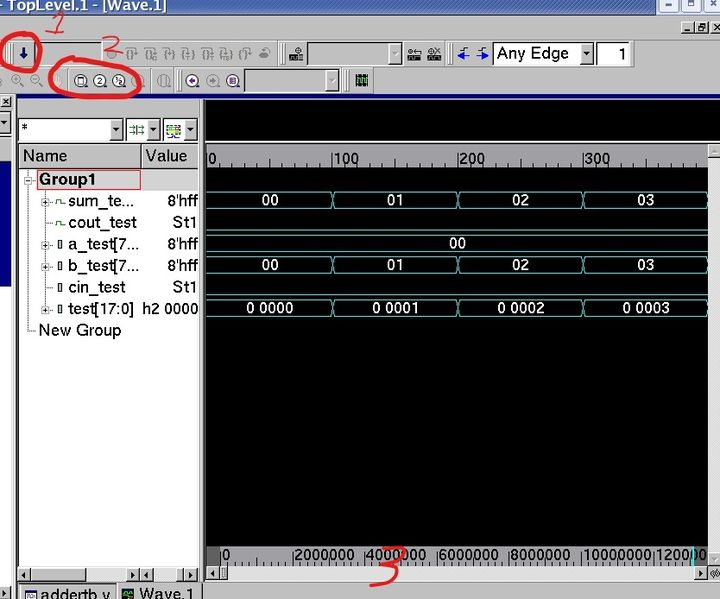

2.4. 添加波形信号

使用./simv -gui 命令打开图形化界面DVE,选中所有信号 --> 右键Add to Waves --> New Wave View

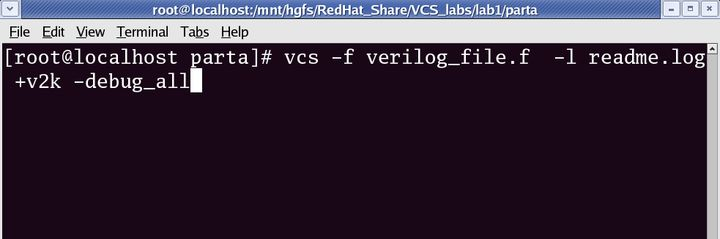

2.5. f文件

在工作目录下新建一个verilog_file.f文件,将所用到的verilog源码以及路径写入文件,并保存退出。使用-f verilog_file.f 选项,即可将.f文件里的源码全部编译。

2.6. 常用命令

以下有其他常用编译选项,注意各个编译选项的顺序,有时出错需要调整。

1) -R 编译后立即运行,即编译完成后立即执行 ./simv

2) -Mupdate 源文件有修改时,只要重新编译有改动的.v文件,节约编译时间。

3) -sverilog 打开对Systemverilog的支持,编译Systemverilog文件时使用。

4) -timescale=1ns/1ns 设置仿真精度

5) -o simv_file 编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。

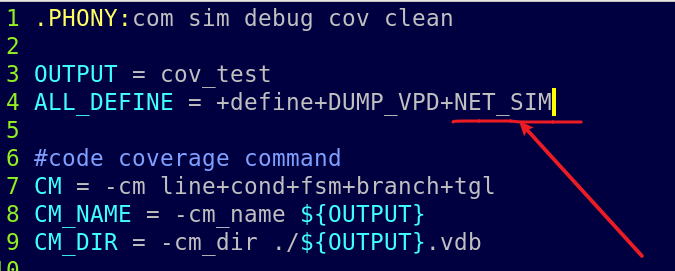

2.7. makefile

命令比较多时,常用makefile文件来描述。

.PHONY:com sim cleanOUTPUT = adder_topVCS = vcs -sverilog +v2k -timescale=1ns/1ns \-debug_all \-o ${OUTPUT} \-l compile.log \SIM = ./${OUTPUT} -l run.logcom:${VCS} -f verilog_file.fsim:${SIM}clean:rm -rf ./csrc *.daidir *.log simv* *.key终端上输入 make com 后回车,相当于在终端中输入以下内容后回车,进行编译。

终端上输入make sim后回车进行仿真。

3. 代码覆盖率

3.1. 概念

在进行功能验证时,给设计添加激励信号,查看仿真结果,需要考虑覆盖率的问题。覆盖率分为代码覆盖率(code coverage)和功能覆盖率(function coverage)。功能覆盖率就是检查设计的功能是否完善,需要考虑很多不同的情况,是使用System verilog的重点内容。代码覆盖率是检查代码是否存在冗余,检查所有的代码是否都已经执行,状态机所有的状态是否都有到达,检查 if else 和 case 条件语句的条件是否都有使用。防止一些不必要的代码浪费芯片面积,毕竟面积就意味着钱。我们这里只讨论代码覆盖率。

对于RTL代码,通常考虑以下覆盖率:

-

Line coverage :行覆盖率,检查语句是否被执行。

-

Toggle coverage:检查电路的每个节点是否都有 0 -> 1 和 1 -> 0 的跳变。这种检查通常会使仿真变慢很多。

-

conditional coverage:检查条件语句是否覆盖了所有的情况。 比如有时写了if 语句,没有写else语句。

-

FSM coverage: 状态机覆盖率,检查状态机所有的状态是否都到达过。

-

path coverage:在always语句块和initial语句块中,有时会使用 if ... else 和 case 语句,在电路结构上便会产生一系列的数据路径。检查这些路径的覆盖情况。

3.2. 生成覆盖率文件

VCS在统计代码覆盖率的过程中,我们通常在编译和仿真命令上添加对应的开关选项,生成一个 .vdb文件记录覆盖率的情况。再使用dve打开该文件查看。下面介绍一些选项。

-cm <coveragetype> :打开对应类型的覆盖率,例如 -cm cond+tgl+lin+fsm+path为统计上述所有覆盖率。可根据需要增减。

-cm_name:设置记录有覆盖率信息文件的名字。

-cm_dir:指定生成文件的目录。

以上三个选项编译仿真过程都要加上。下面的选项在编译过程加上。

-cm_log + filename.log:.log文件记录仿真过程中统计覆盖率的信息。用的比较少。

-cm_nocasedef: 在统计case语句的条件覆盖率时,不考虑default条件未达到的情况。

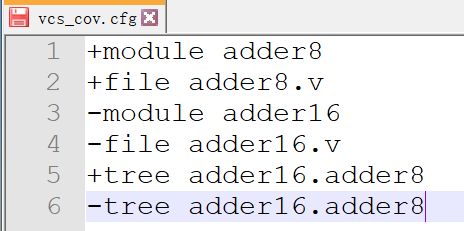

-cm_hier vcs_cov.cfg:通过.cfg文件(名字随便取)选择要查看覆盖率的模块/文件。

“+”代表查看,“-”代表不查看。tree代表查看某个模块调用的子模块。

在文件内部,可以使用特殊注释来打开和关闭代码覆盖率的统计:

//VCS coverage on 统计代码覆盖率

.......

//VCS coverage off 不统计代码覆盖率

在上述注释之间的内容,统计覆盖率。其余地方不统计。

3.3. 查看覆盖

-

统计覆盖率命令并启动UI

dve -covdir *.vdb &-

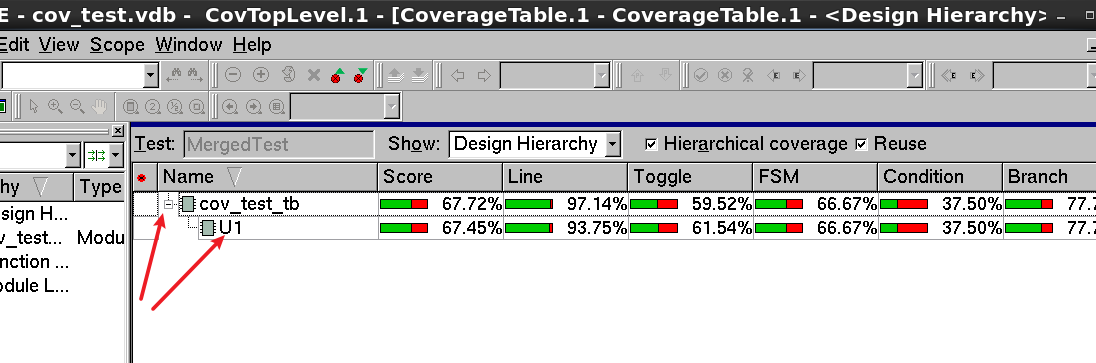

单击箭头1处加号,再双击箭头2处的U1,查看设计的代码覆盖率。

-

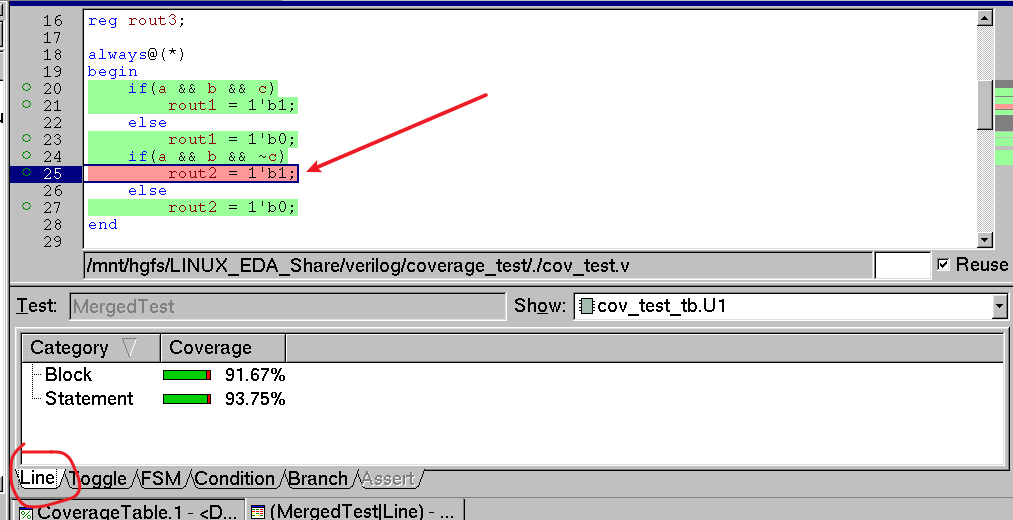

行覆盖率,第25行未执行过。

-

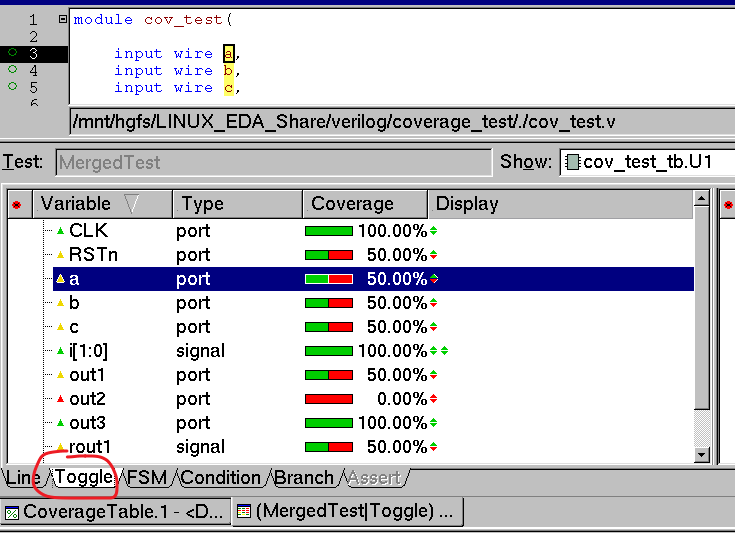

Toggle coverage:大量节点都没有 0 -> 1 和 1 -> 0 两种跳变

-

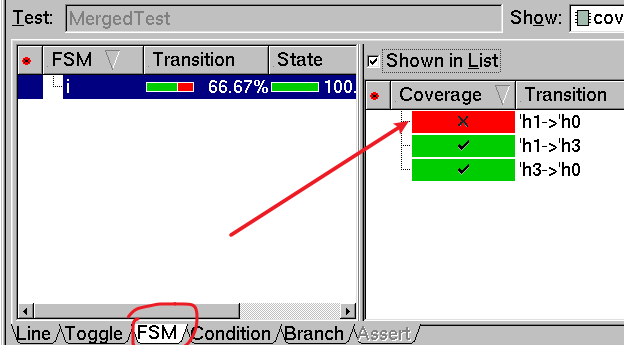

FSM coverage : 2'd1 -> 2'd0 的转换没有发生过。

-

condition 覆盖率

-

Branch(Path) 的覆盖率

4. 逻辑综合

当我们把所写的RTL进行的功能仿真通过之后,便输入到 Design Compiler工具中进行逻辑综合,逻辑综合的结果便是RTL代码转化为由与、或、非等门电路和触发器组成的电路,称为门级网表(netlist)。门级网表中便包含了电路的实际信息,例如逻辑门单元的扇入扇出系数,延迟等等。因此在逻辑综合完成之后,需要对网表再进行仿真验证,防止出现意想不到的错误。

对于实际电路,时钟信号并不是理想的“陡直”,门电路也存在延迟,这些电路的实际信息需要在逻辑综合的时候考虑到。RTL代码转换为门级电路,我们需要对电路施加一些约束。例如时序电路的工作频率,电路中组合逻辑块的延迟等等。综合工具会根据我们施加的约束做时序上的优化,从工艺库中挑选合适的单元,在面积,时序和功耗三个方面进行折中。当然满足时序的要求是首要的,面积和功耗要越小越好。

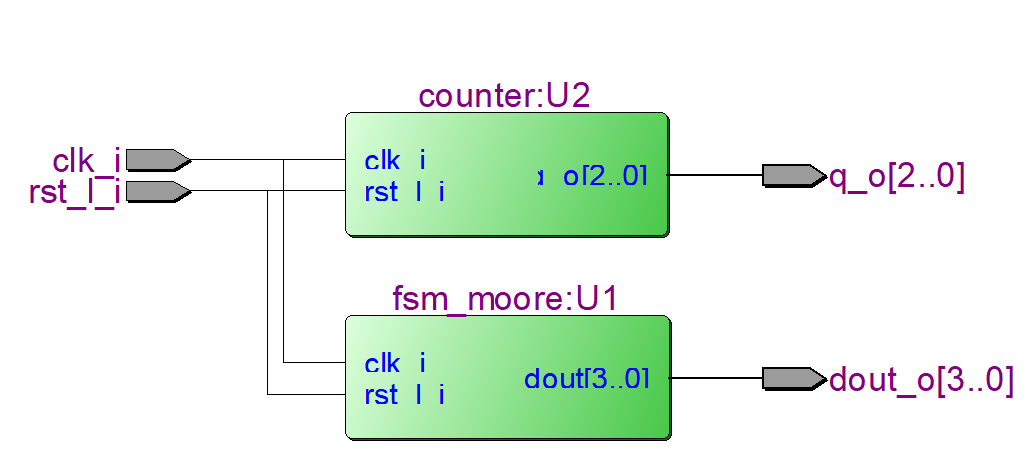

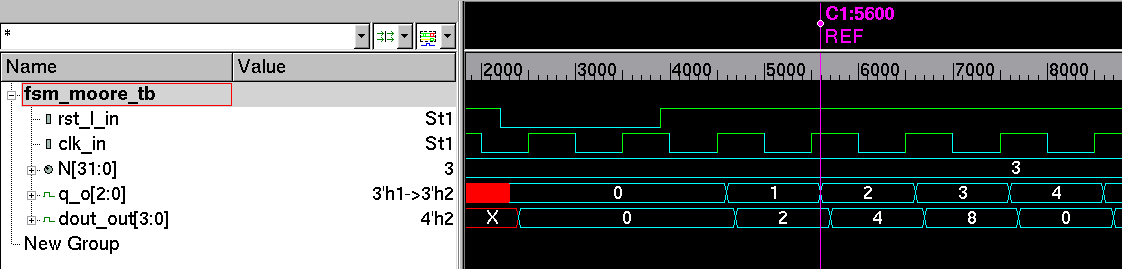

为简单起见,以一个Moore状态机为实例,做最基本的不添加约束的逻辑综合,用以生成门级仿真所需要的文件。设计电路框图如下:

由一个计数器和moore状态机组成。

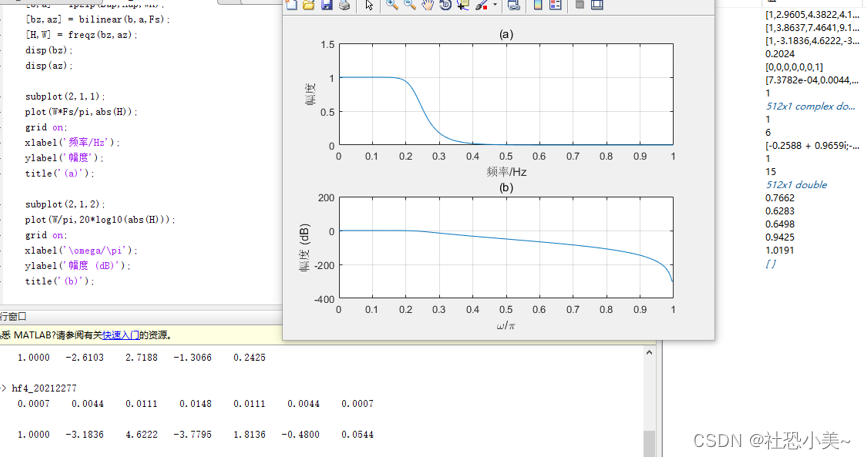

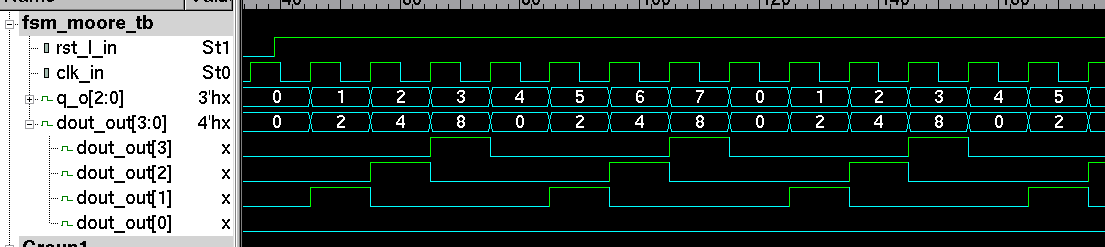

RTL仿真图如下

q_o 为三位计数器的输出,dout_out为状态机的输出,按 0000 0010 0100 1000 的顺序循环。

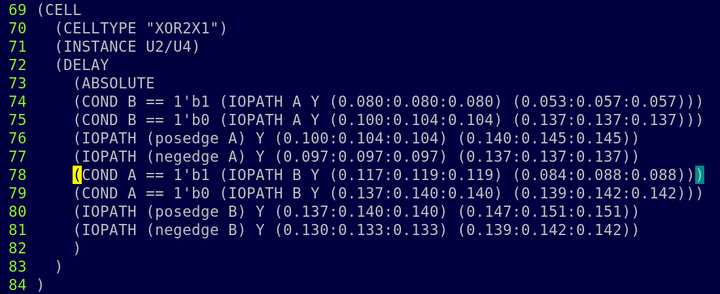

之后便在Design Compiler中进行综合生成后端和门级仿真的文件,我们在此关心VCS门级仿真所需要的文件。SDF文件包括设计中的时序信息,.v文件是以工艺库单元例化形成的verilog文件。

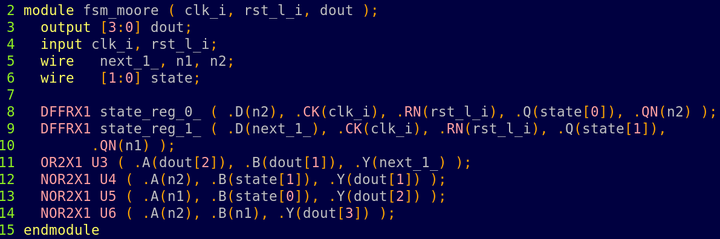

我们可以看到网表形式的verilog文件,由门电路和触发器例化组成。

4. 网表仿真

-

makefile模板添加了一个开关选项,由于网表.v文件是由工艺库单元例化的,工艺库中给出了一个verilog文件,包含各个单元。

-

定义NET_SIM这个宏。用于testbench中代码块的打开和关闭。

-

在Testbench中添加添加下面的代码块,使用sdf_annotate()系统函数将sdf文件“反标”到设计中,第一个参数指定sdf文件,第二个参数指定反标到哪一层的module上,这里我们选择顶层文件。其他参数保持默认即可

initial begin

`ifdef NET_SIM$sdf_annotate("/mnt/hgfs/LINUX_EDA_Share/DC_Projects/netlist_simulation/Top.sdf",Top,,,"TYPICAL","1:1:1","FROM_MTM");

`endif

end-

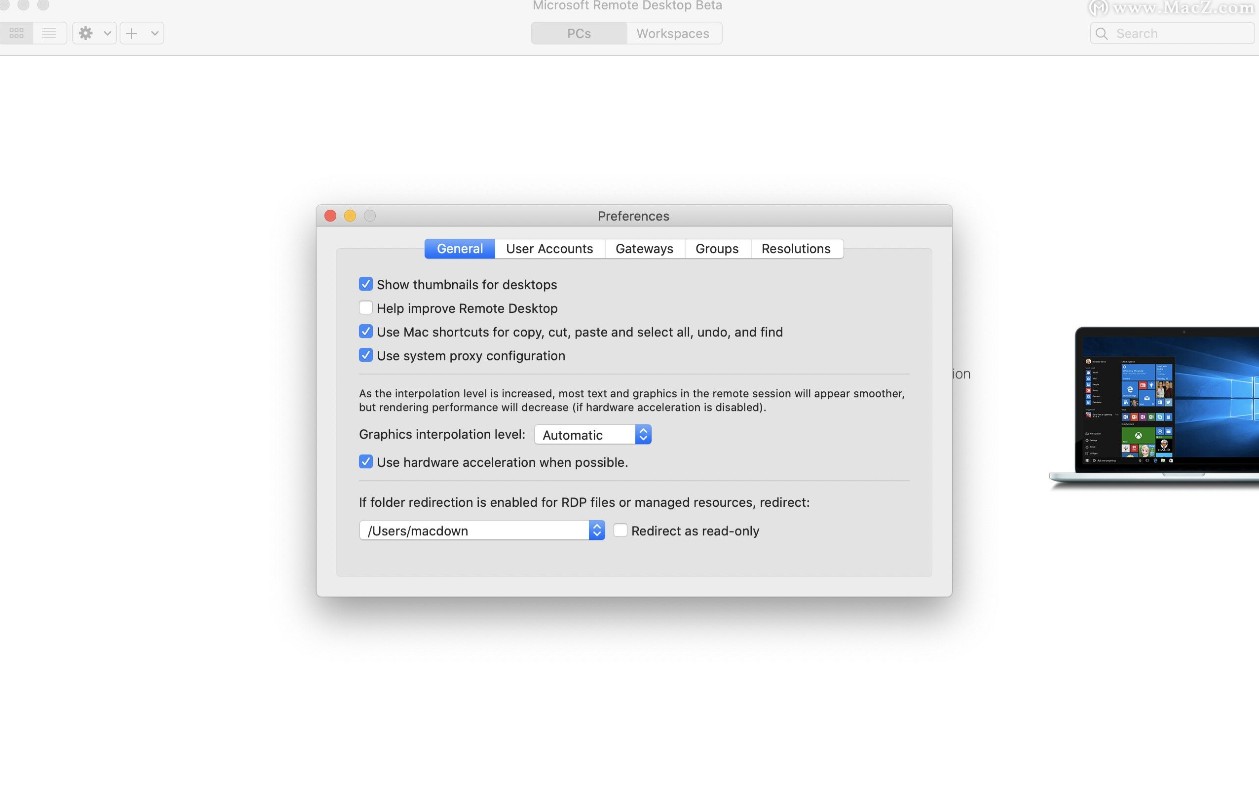

设置完毕后使用 make com sim debug 命令查看门级仿真波形,可以看到输出信号的跳变与时钟上升沿已有一段延迟,这与RTL仿真是不同的。

![Fastjson 反序列化漏洞[1.2.24-rce]](https://img-blog.csdnimg.cn/direct/16fd4bba409c400e82294be5e07e692a.png)