目录

- 会议议程

- 前言

- 开源处理器芯片的机遇与挑战,孙凝晖,中国工程院院士

- RISC-V原生基础软件栈,武延军,中国科学院软件研究所

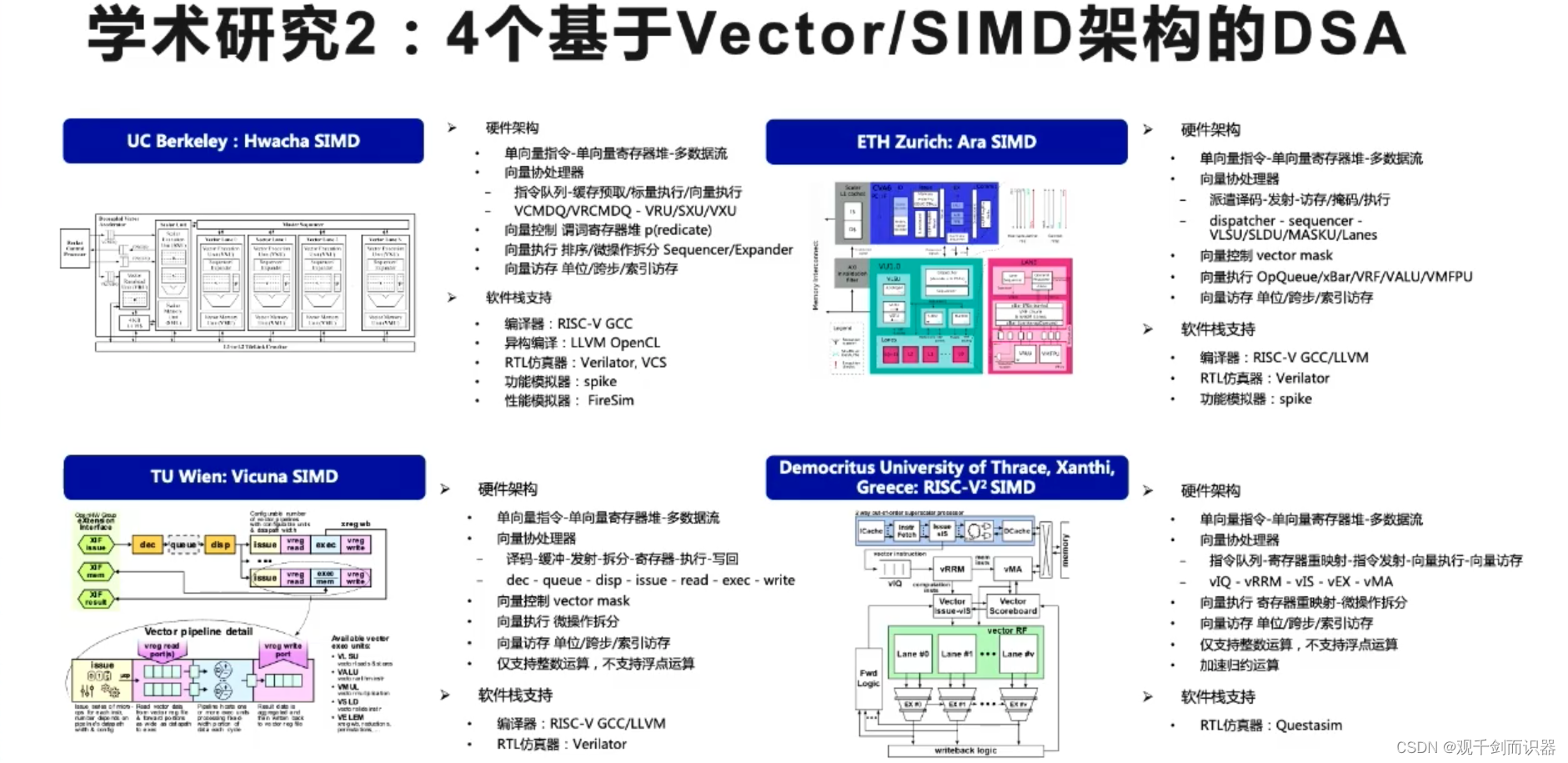

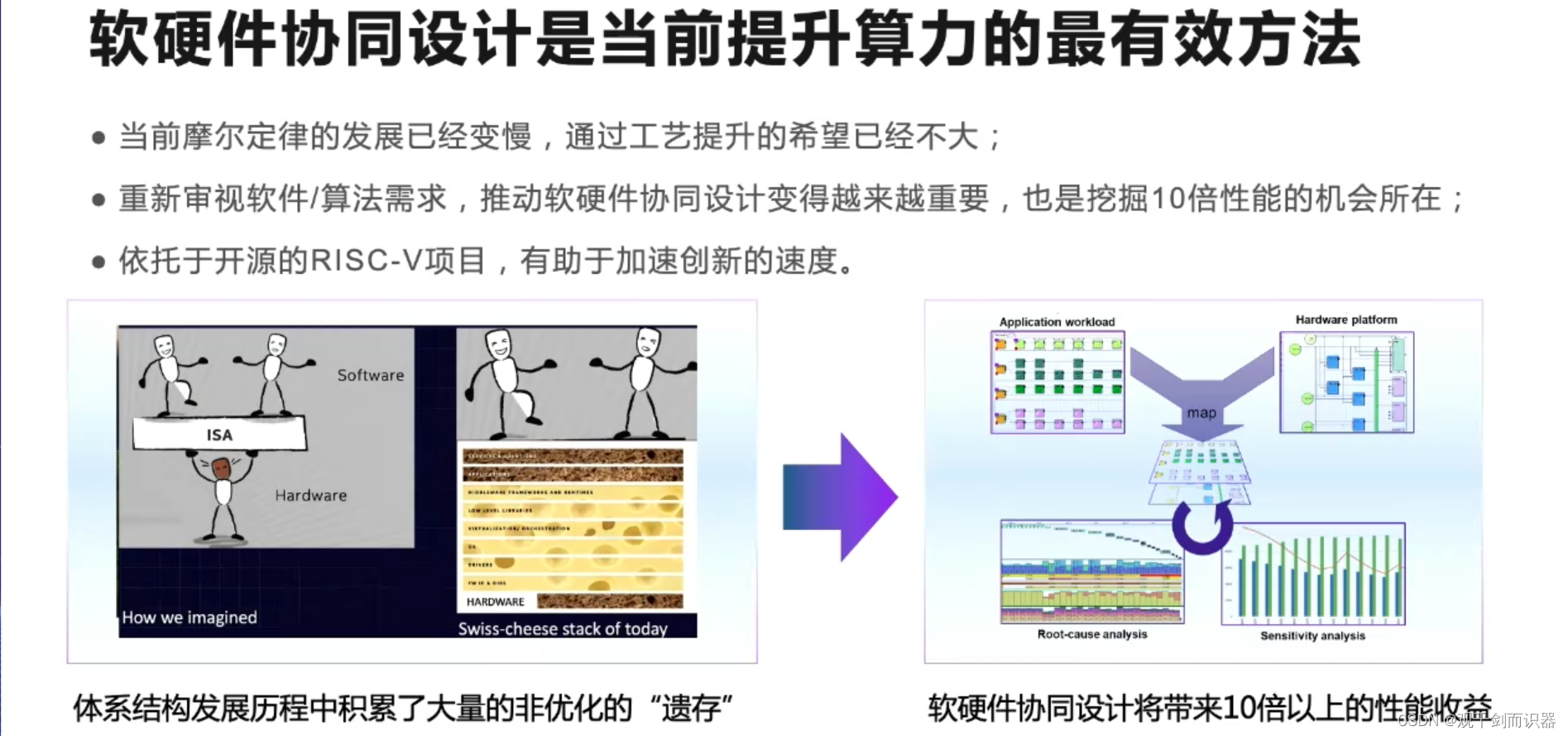

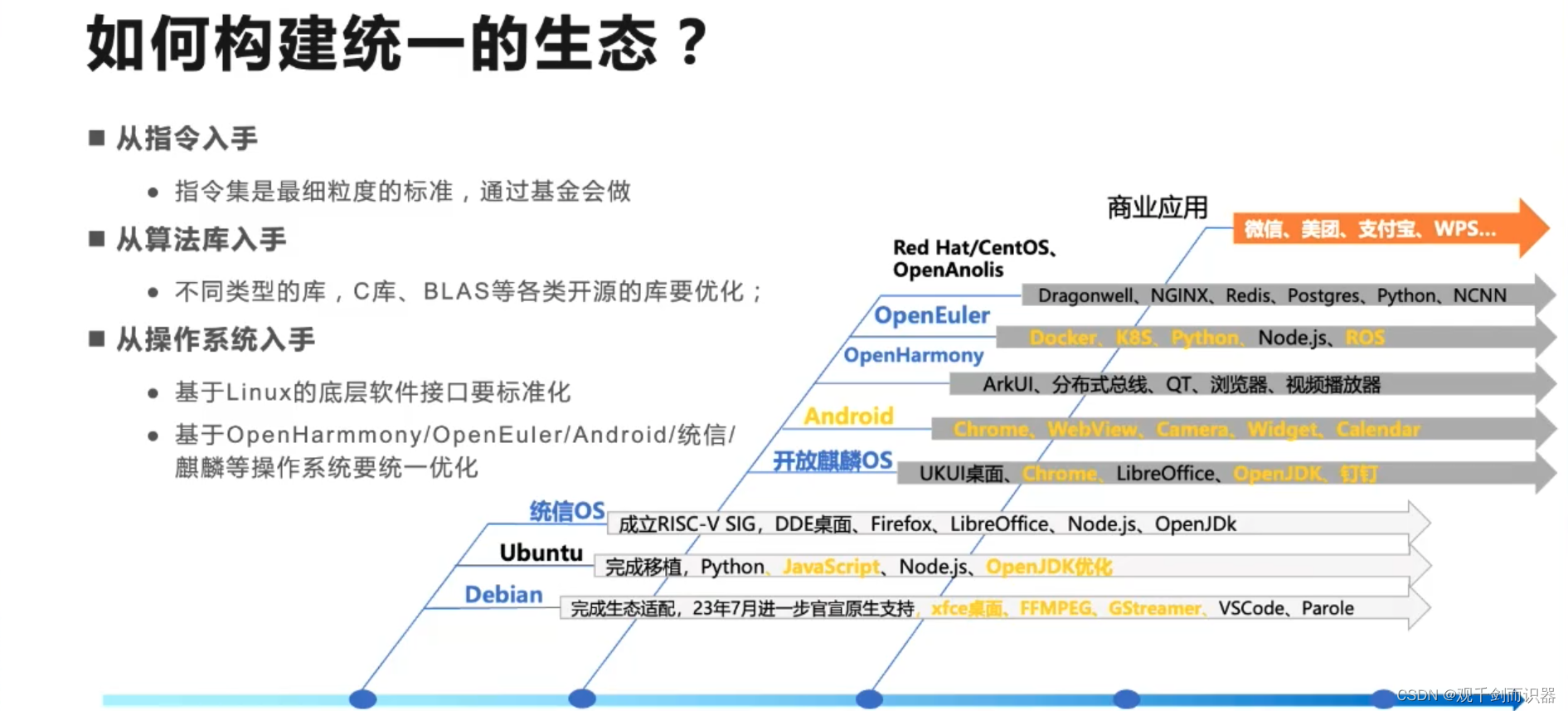

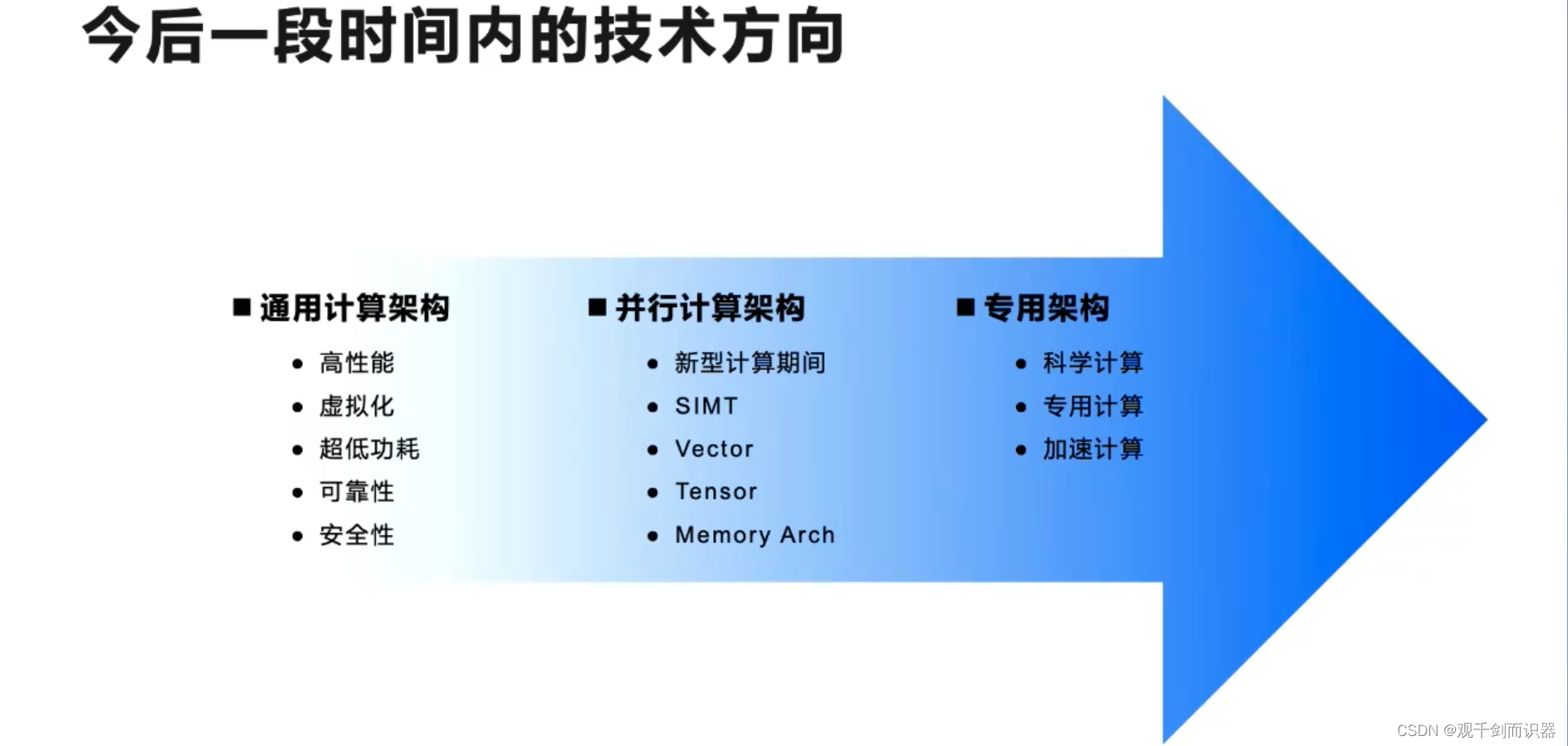

- RISC-V推动新型架构创新,孟建熠,浙江大学

- 专题一:开源芯片

- 开源高性能 RISC-V 处理器核香山开发实践,包云岗,香山团队

- RISC-V敏捷设计与验证,张旭,英特尔中国研究院

- 专题二:RISC-V软件生态

- 编译在新型应用发展下的潜力,崔慧敏,中国科学院计算技术研究所

- 专题三:RISC-V与先进计算

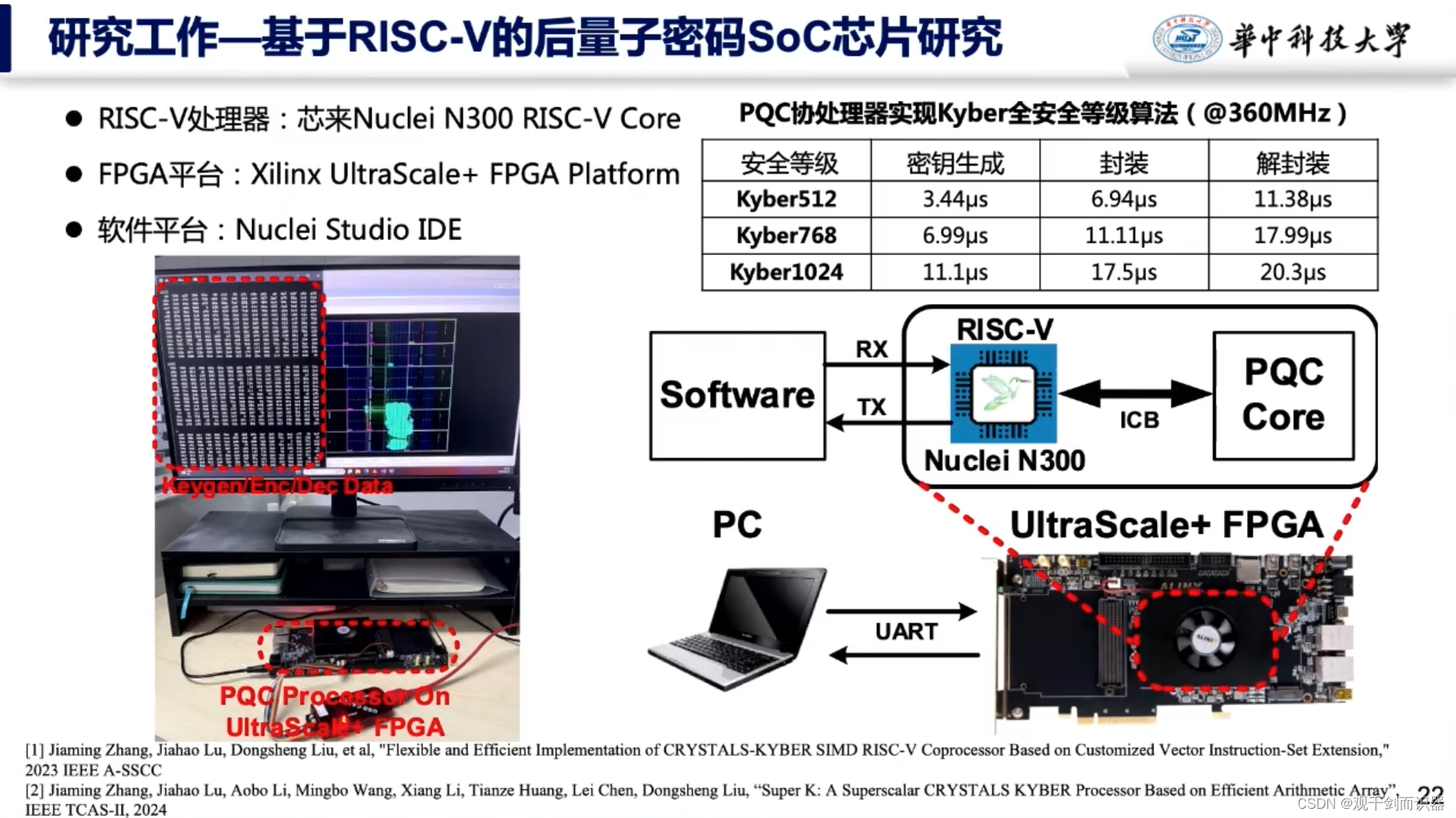

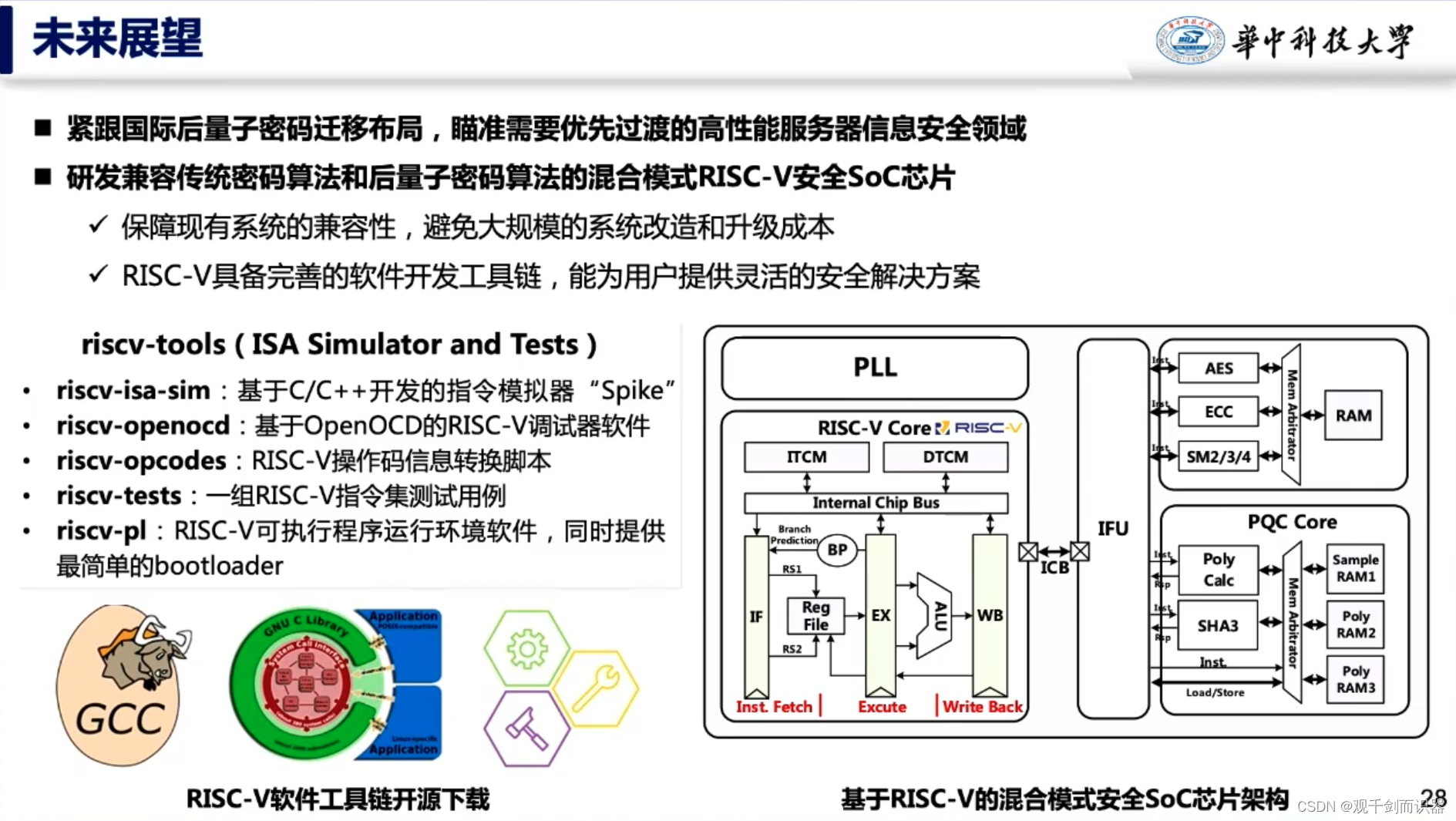

- 基于RISC-V的后量子密码芯片设计,刘冬生,华中科技大学

- 存算一体集成芯片,刘琦,复旦大学

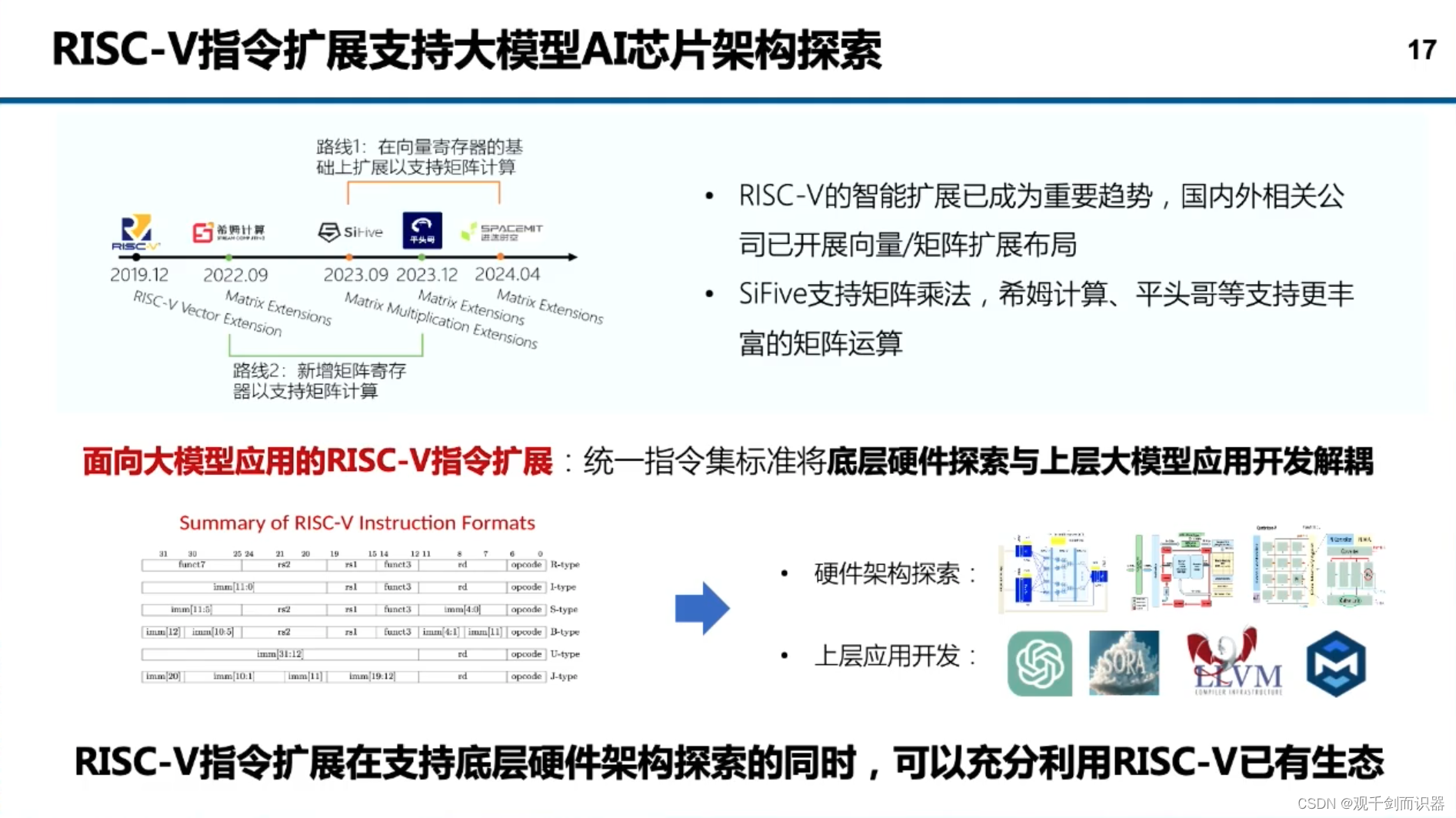

- 面向端侧大模型计算的RISC-V矩阵扩展架构,韩军,复旦大学

- 基于RISC-V的神经网络加速运算算法及处理器结构优化,叶涛,南方科技大学

- 专题四:RISC-V与人工智能

- RISC-V+AI算力系统软件栈建设,谢涛,北京大学

- 大模型AI芯片架构探索,郭崎,中国科学院计算技术研究所

- 专题五:RISC-V与安全

- 处理器侧信道攻击 吕勇强 清华大学

- 可信执行环境及关键技术研究,张锋巍,南方科技大学

- 处理器微处理架构安全,邓舒文,清华大学电子工程系

2024年5月19日,雁栖青年论坛 RISC-V生态专题论坛。

站得高,才能看得远,学习前沿知识,用于今后职业发展的方向指导。

会议议程

前言

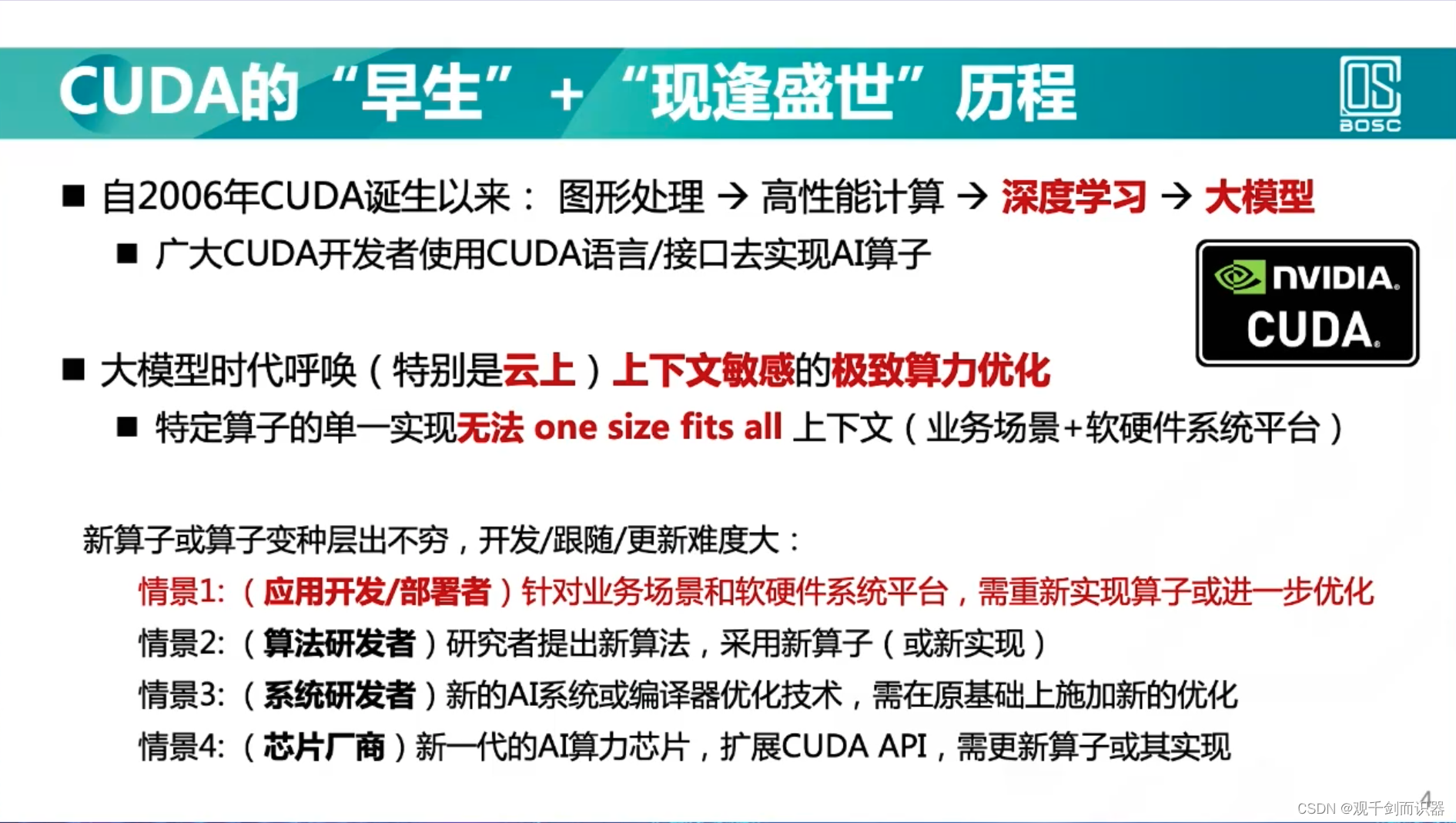

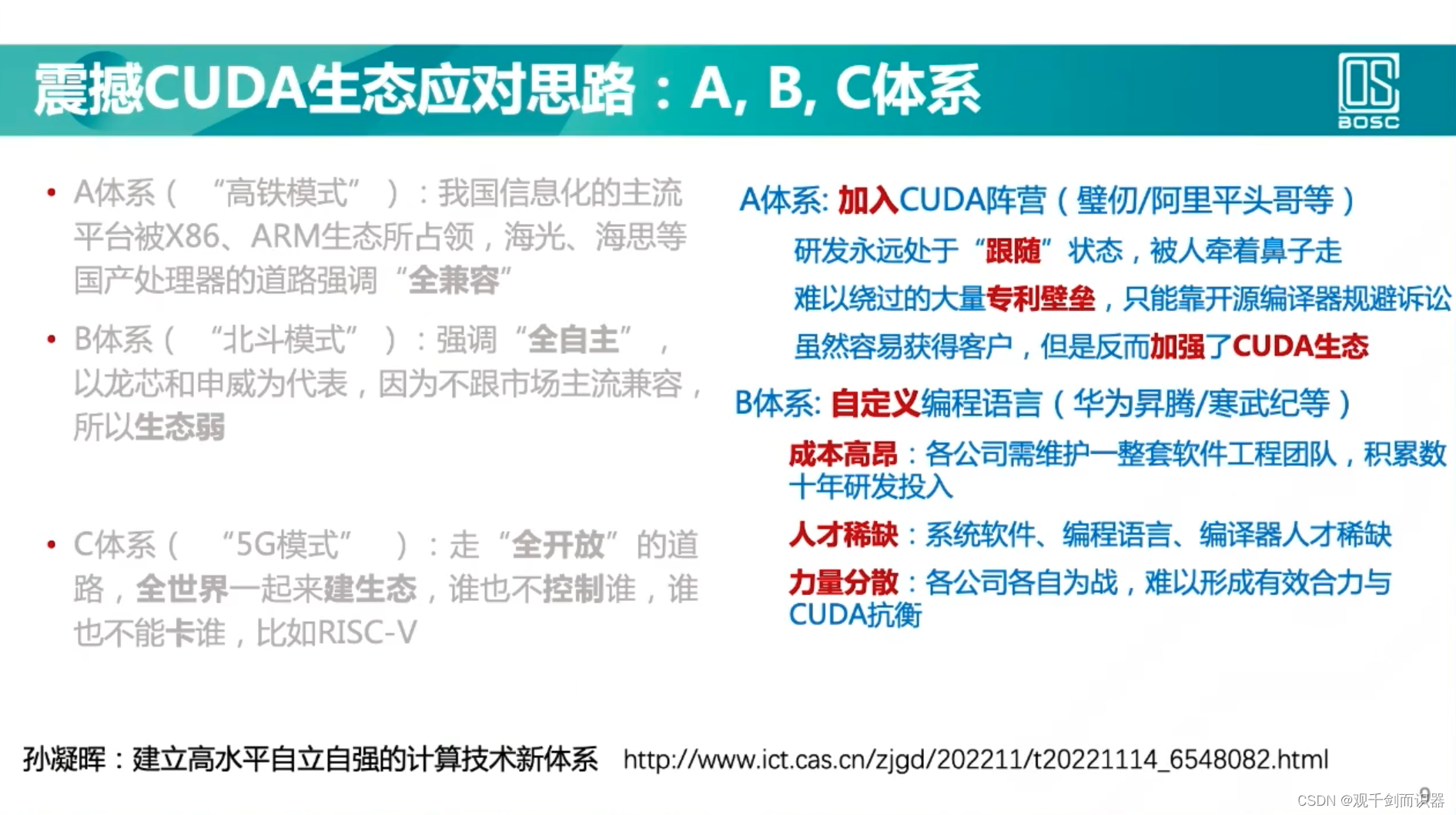

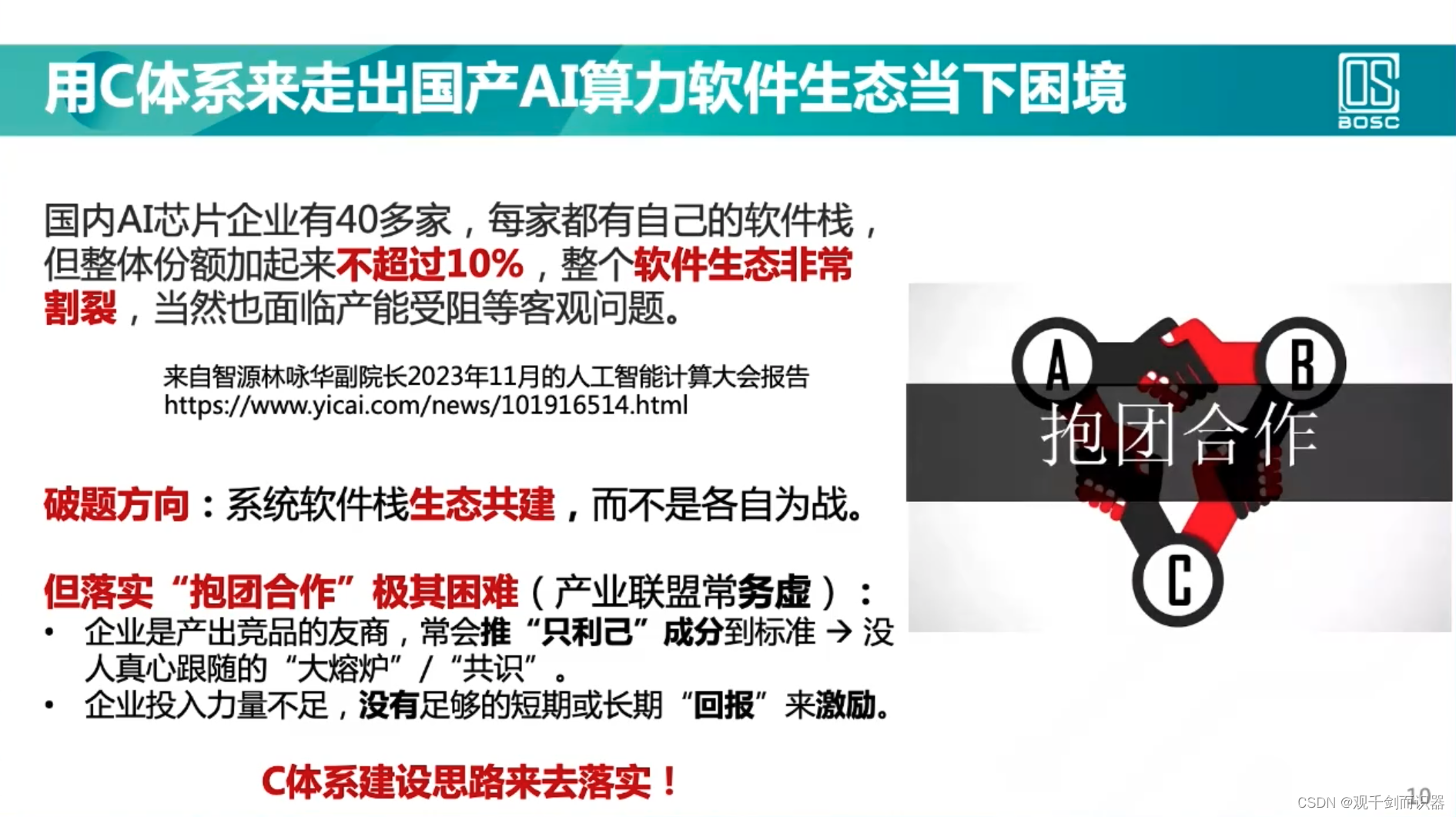

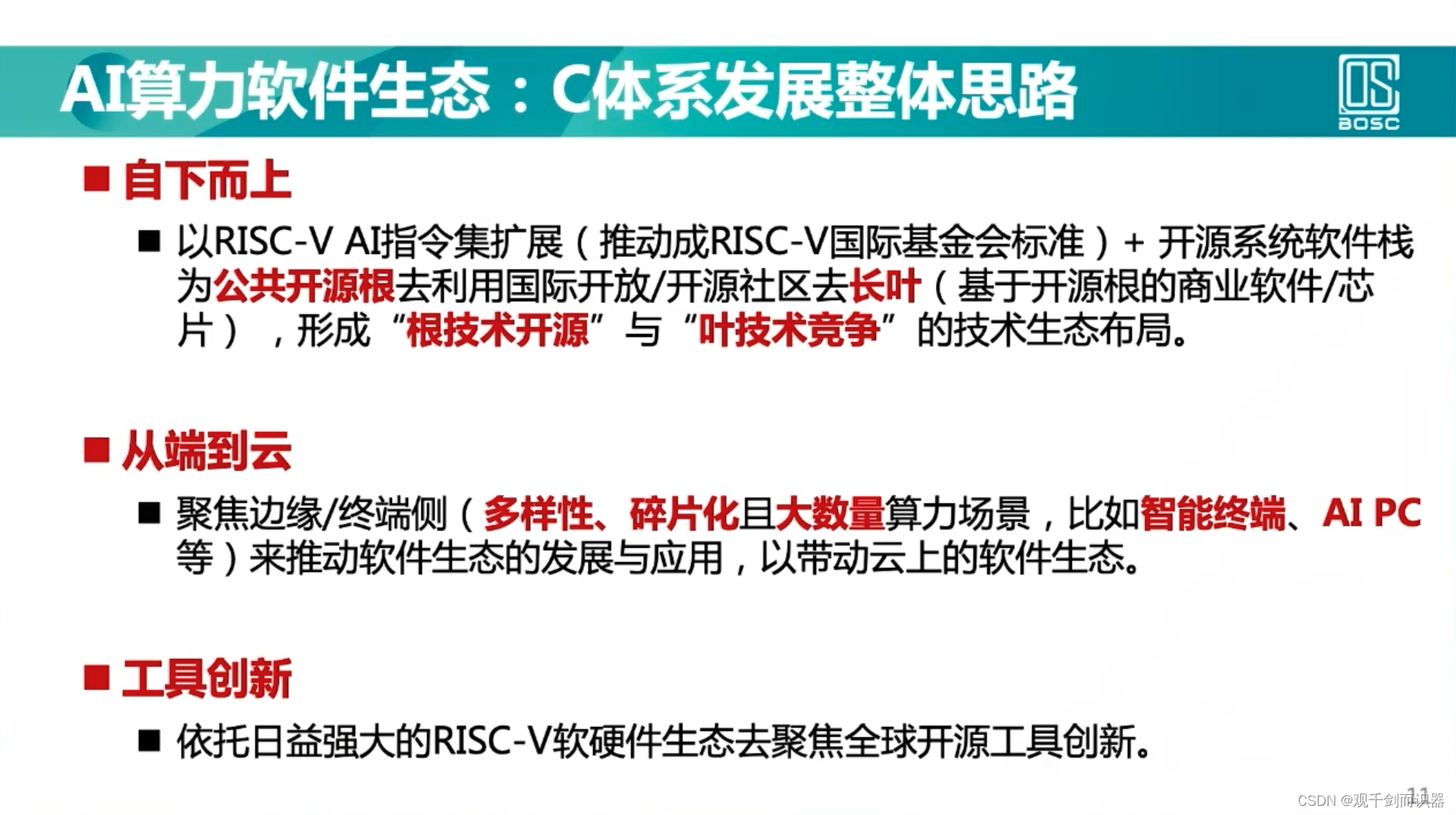

开源处理器芯片的机遇与挑战,孙凝晖,中国工程院院士

b站视频传送门:开源处理器芯片的机遇与挑战,孙凝晖,中国工程院院士

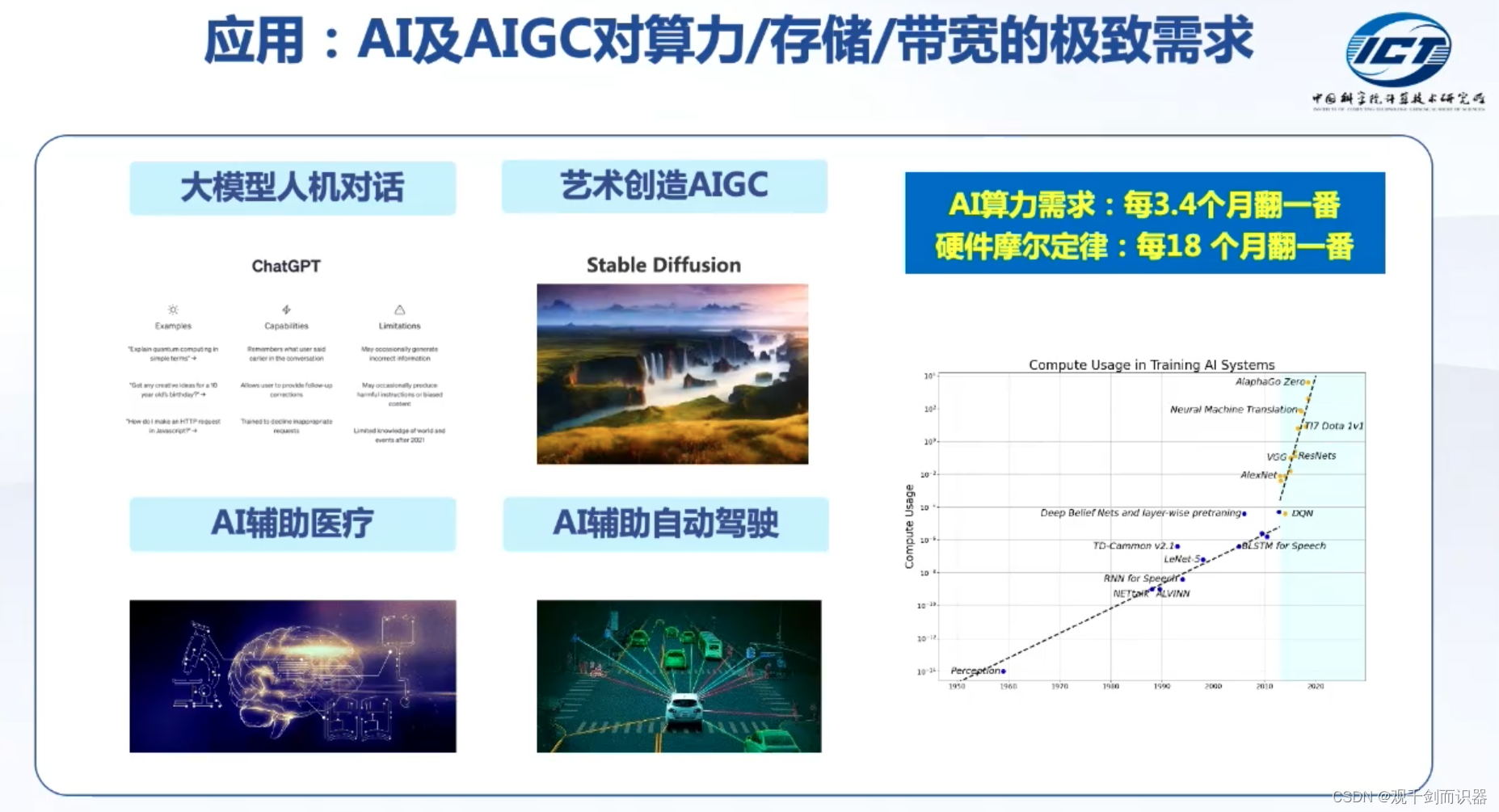

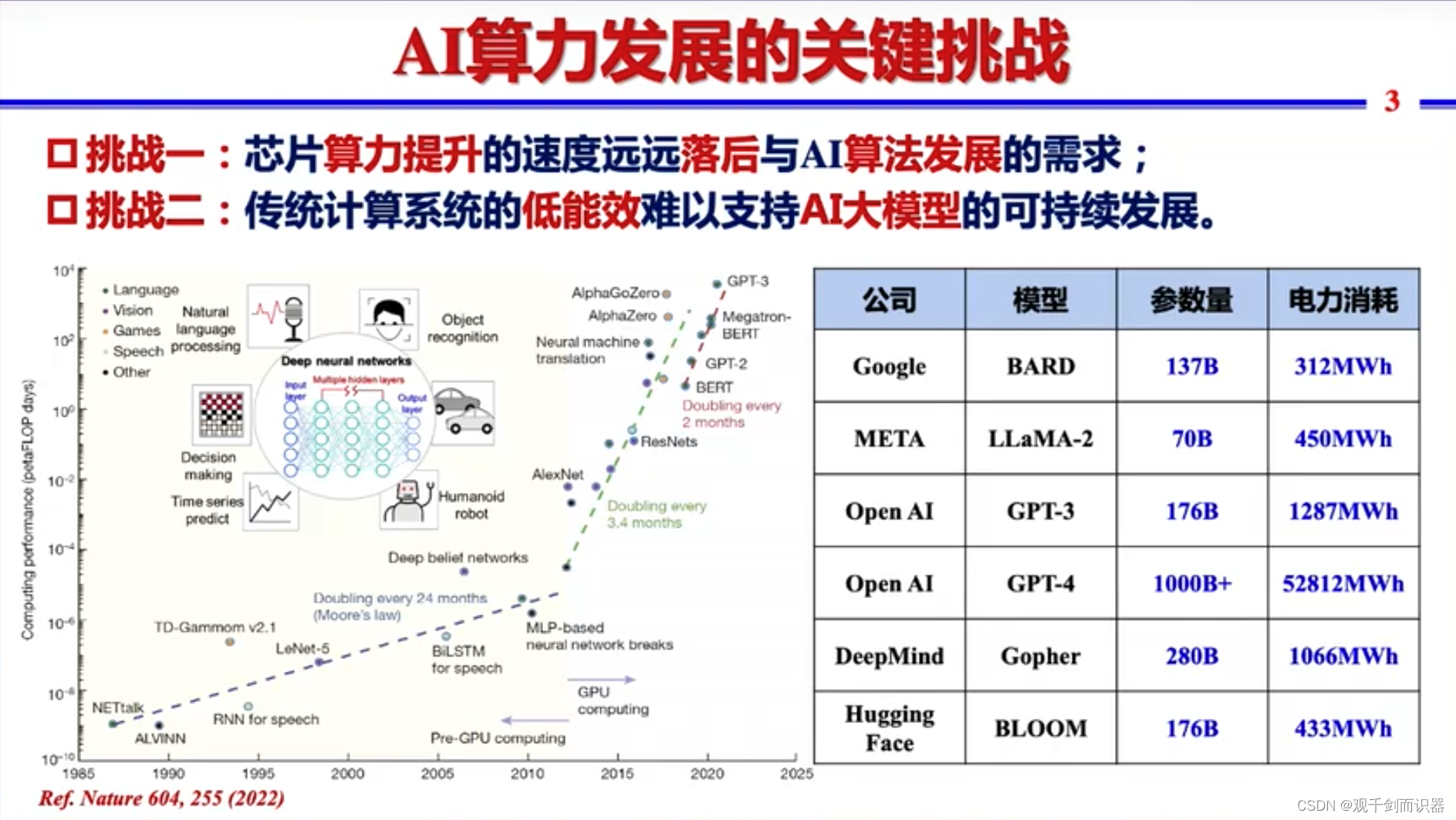

- 大模型训练、数据中心(万亿参数)

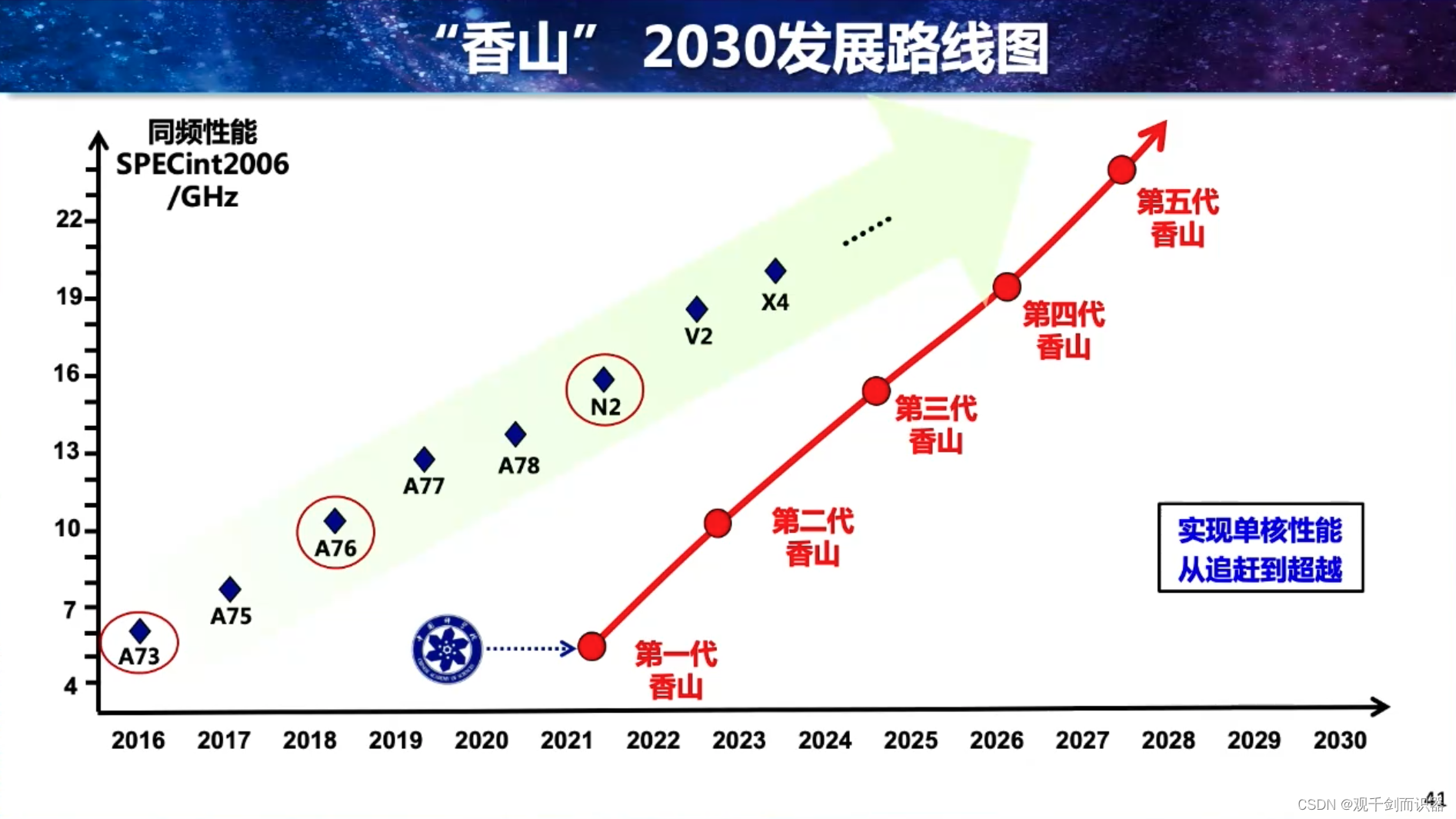

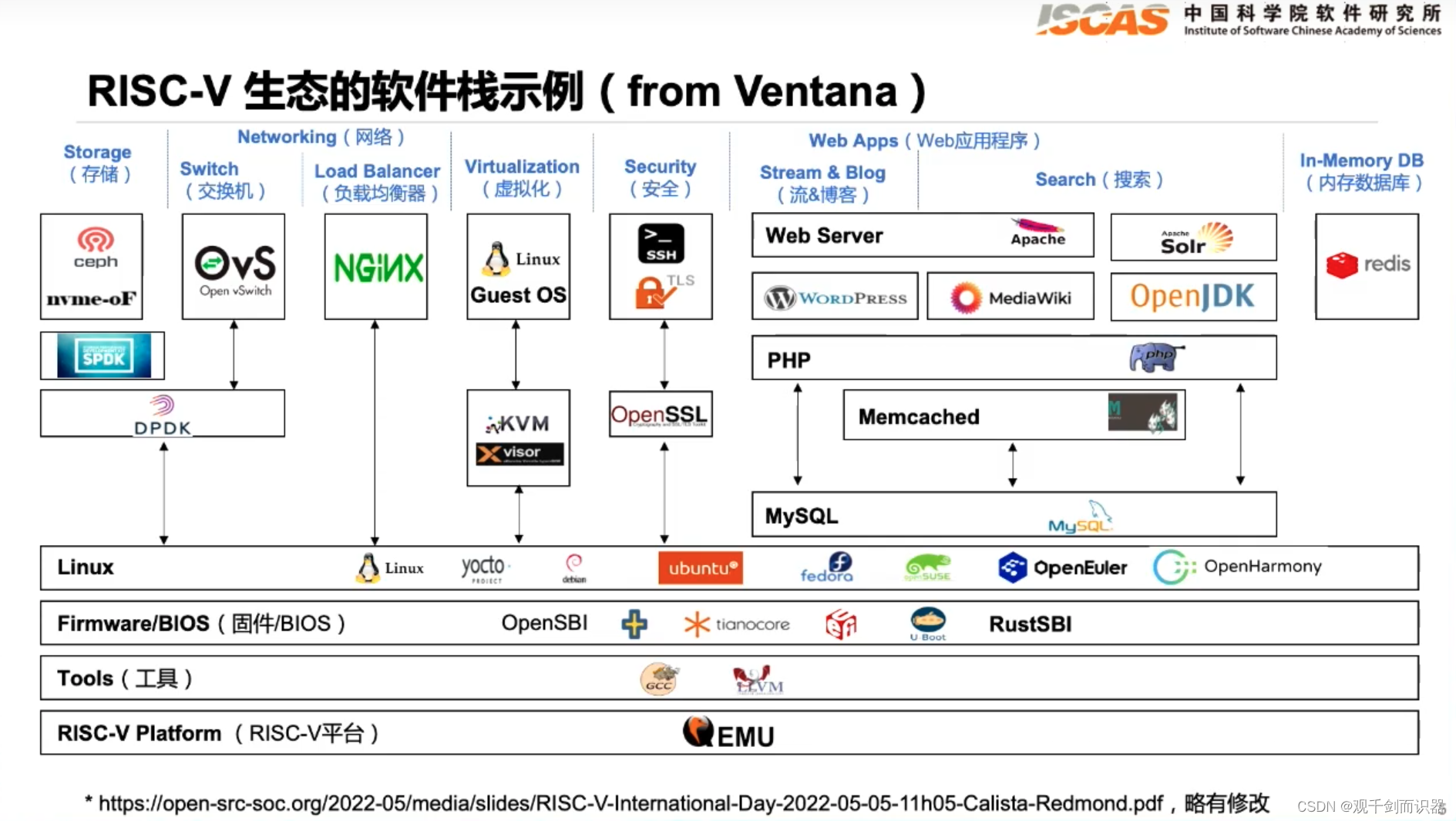

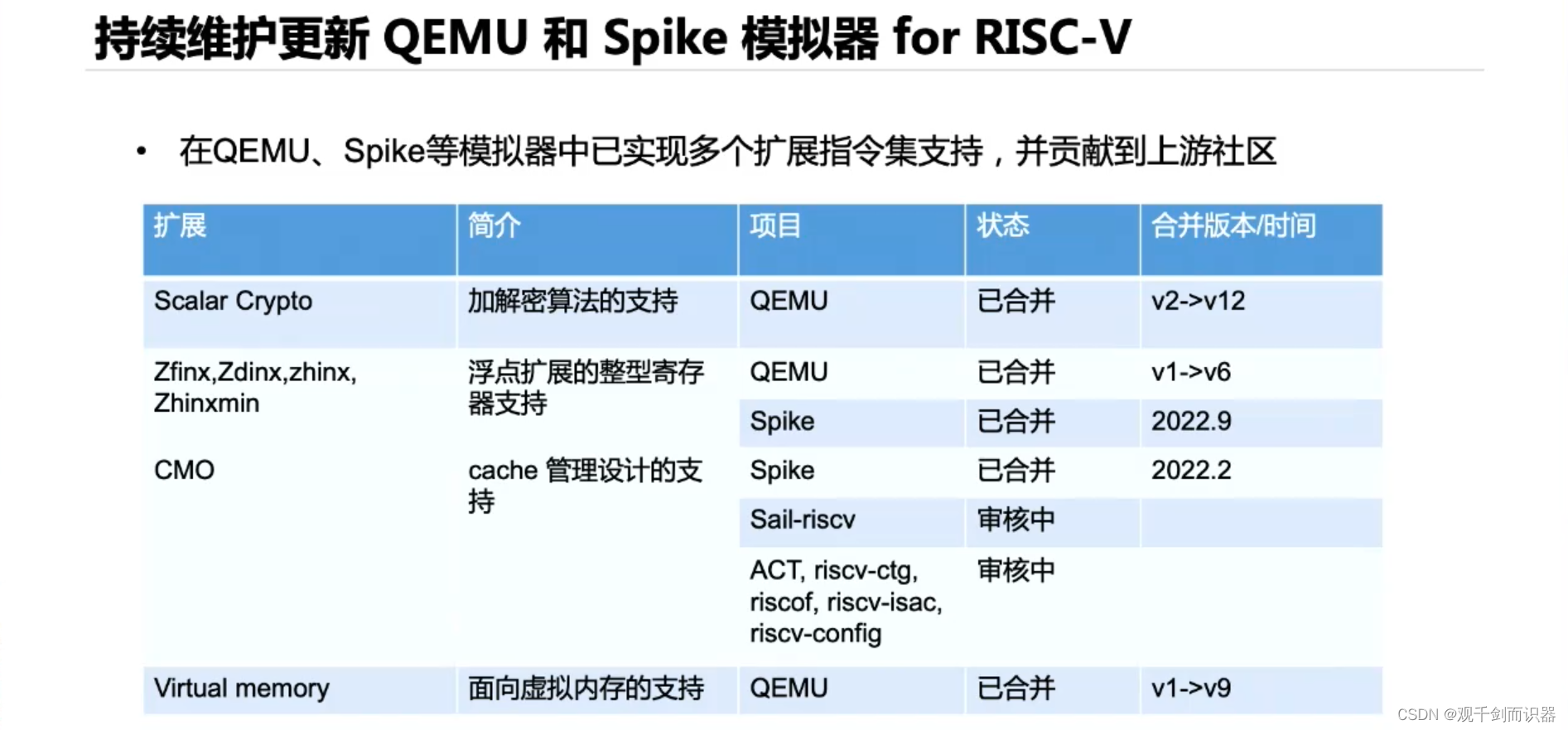

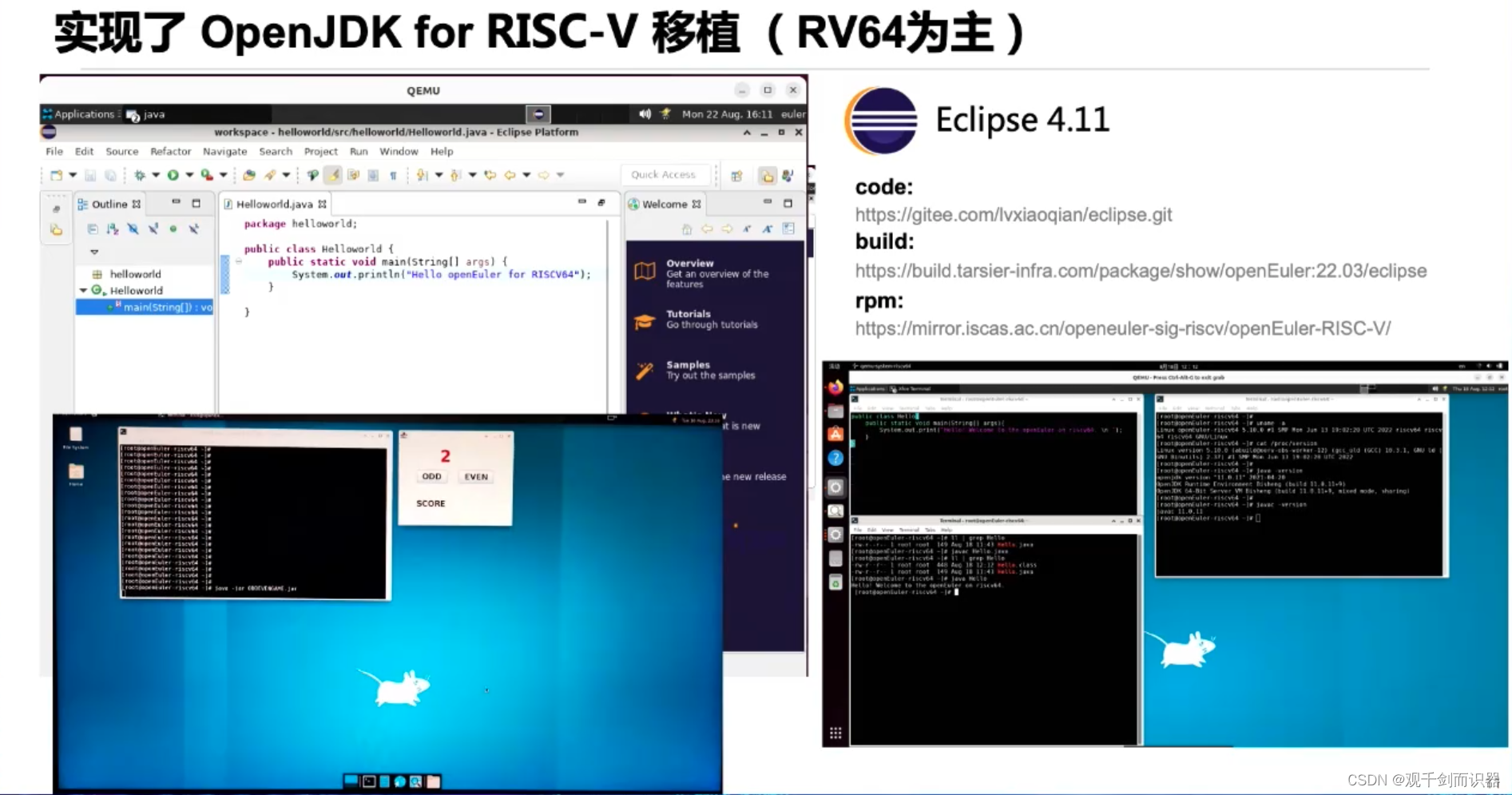

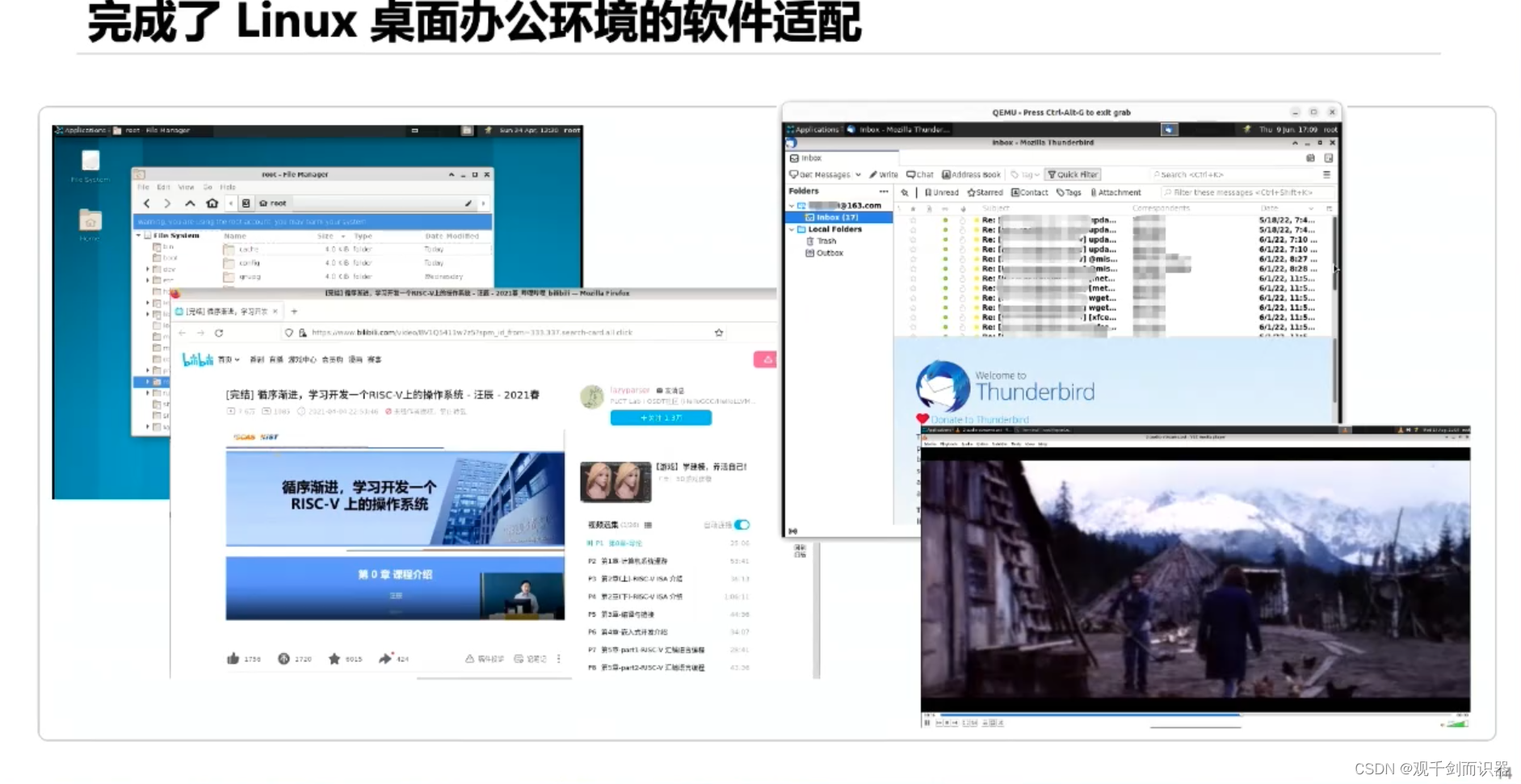

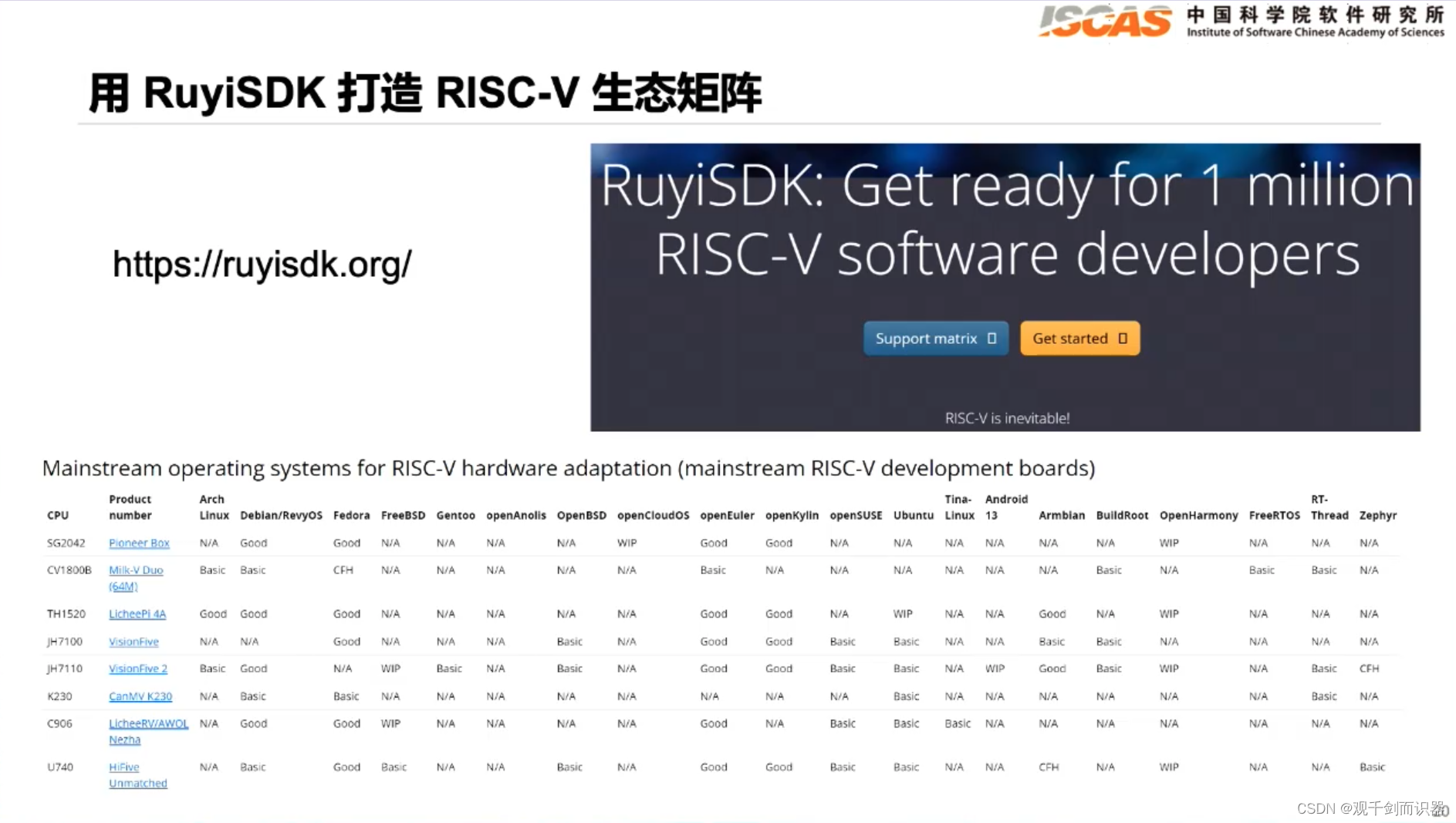

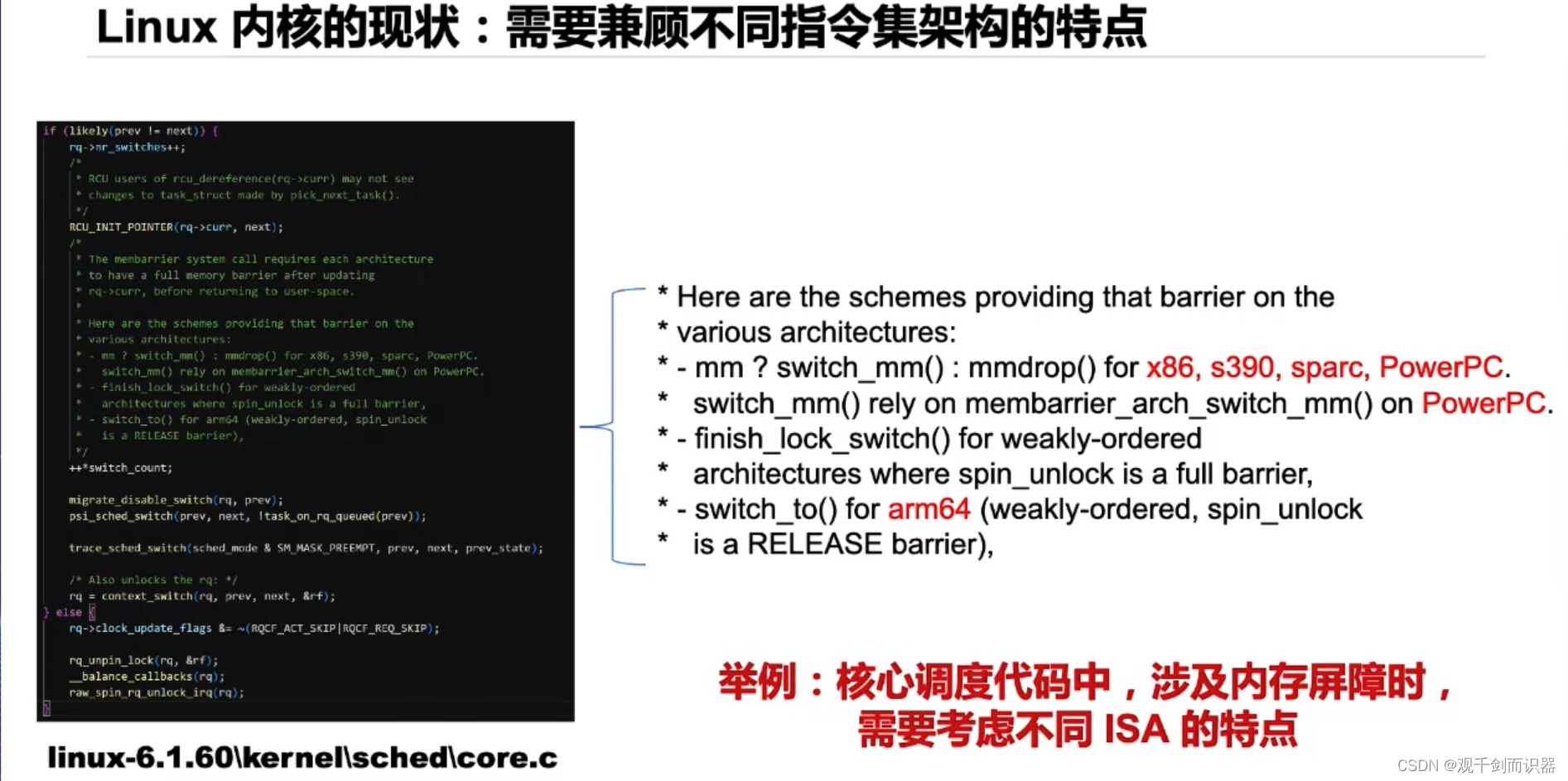

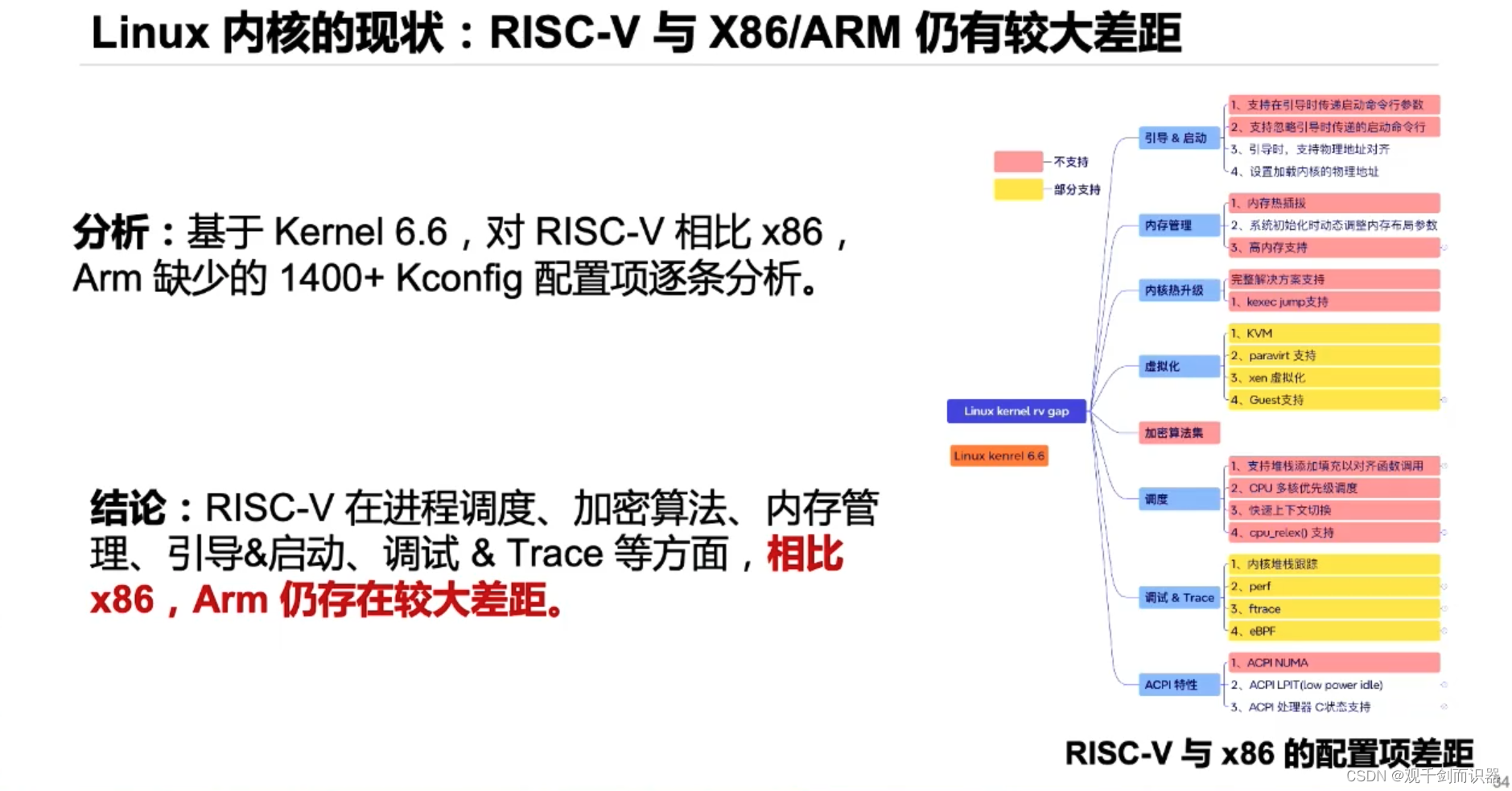

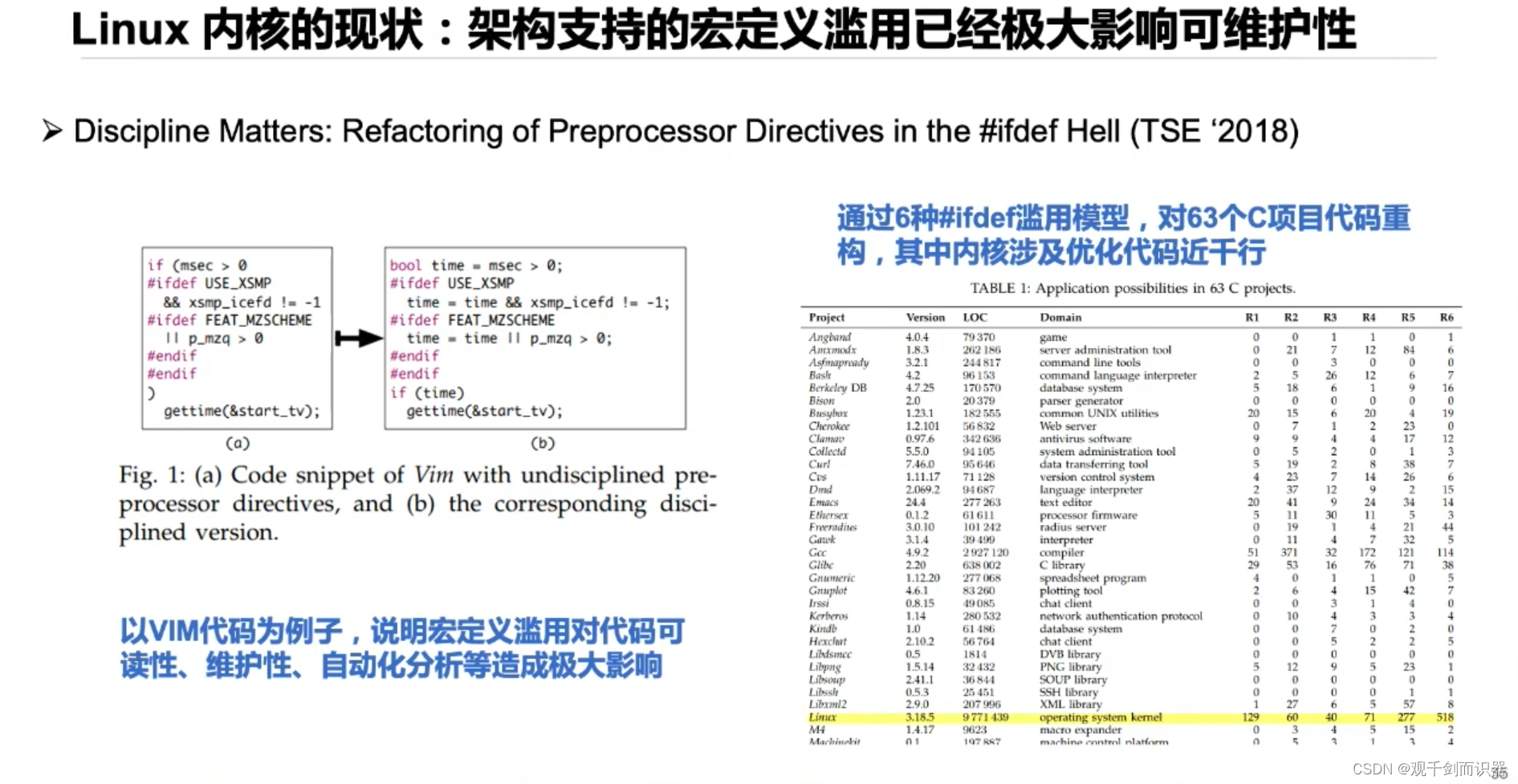

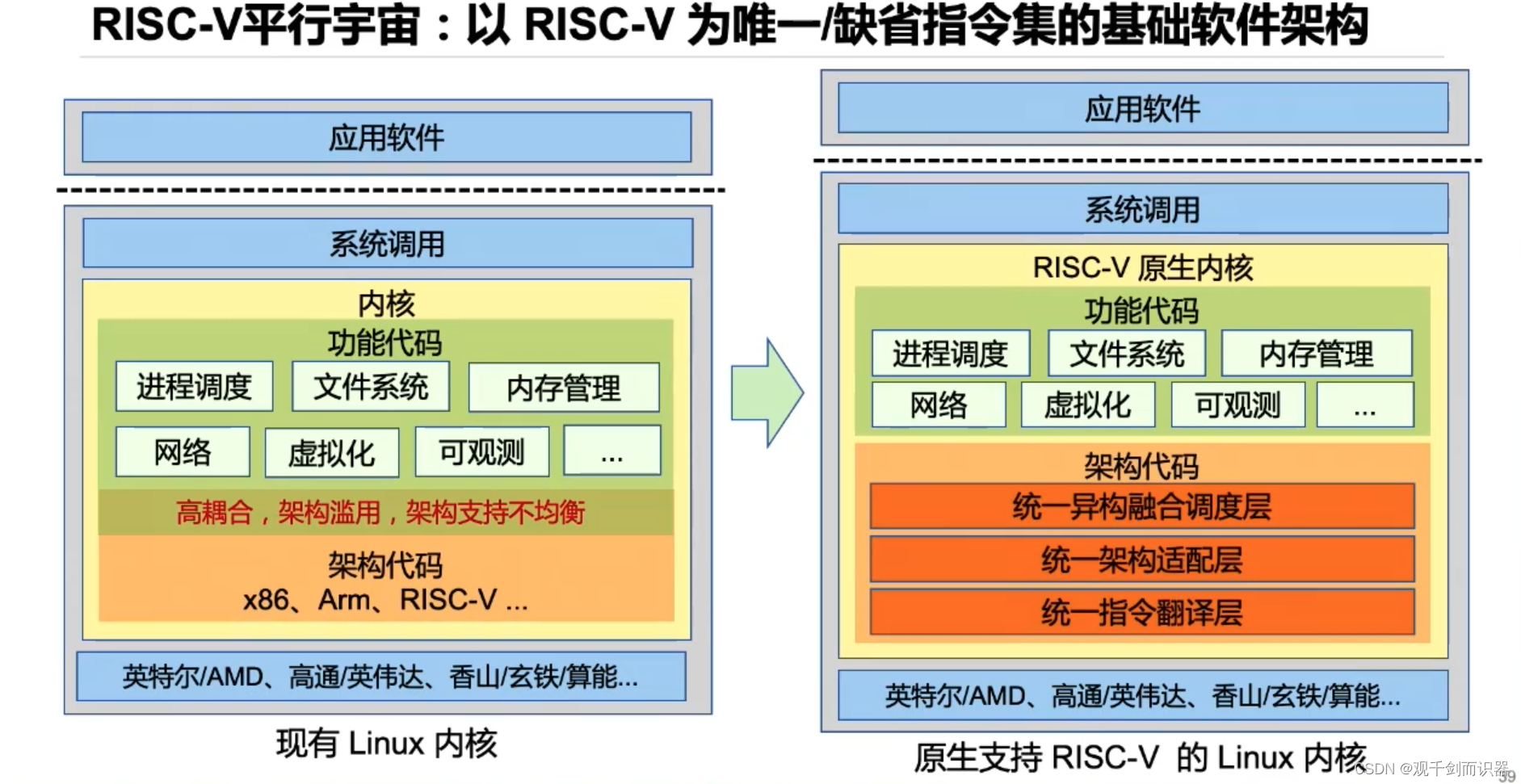

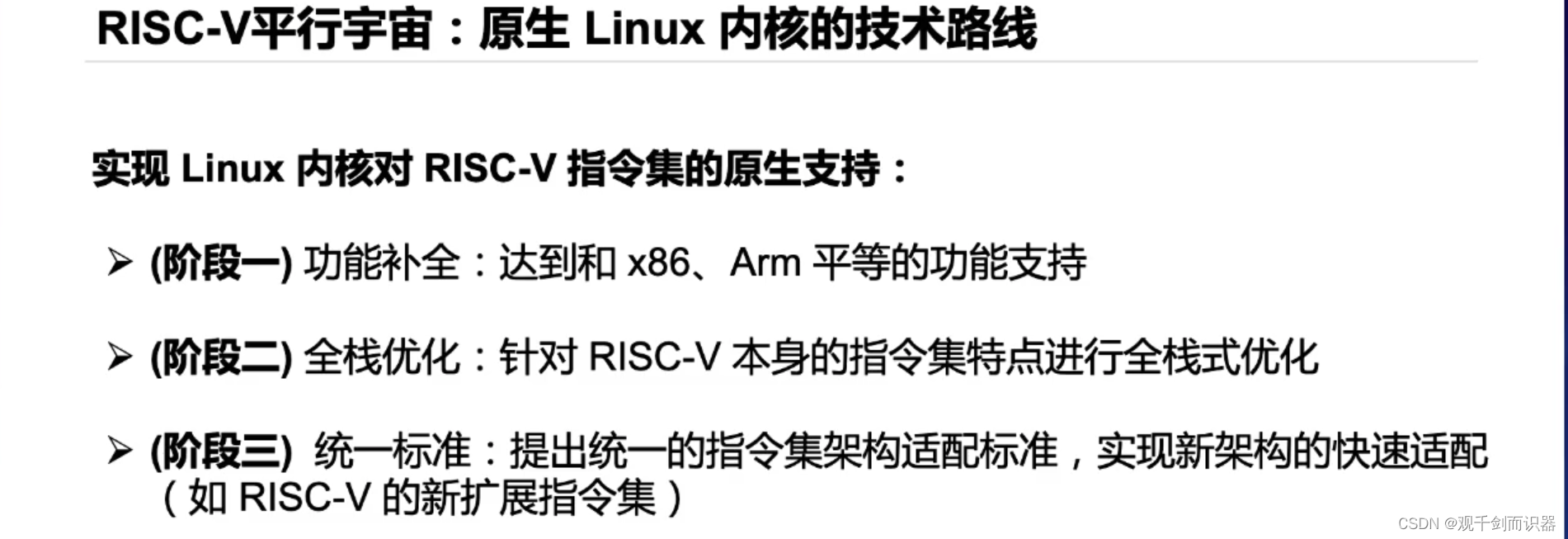

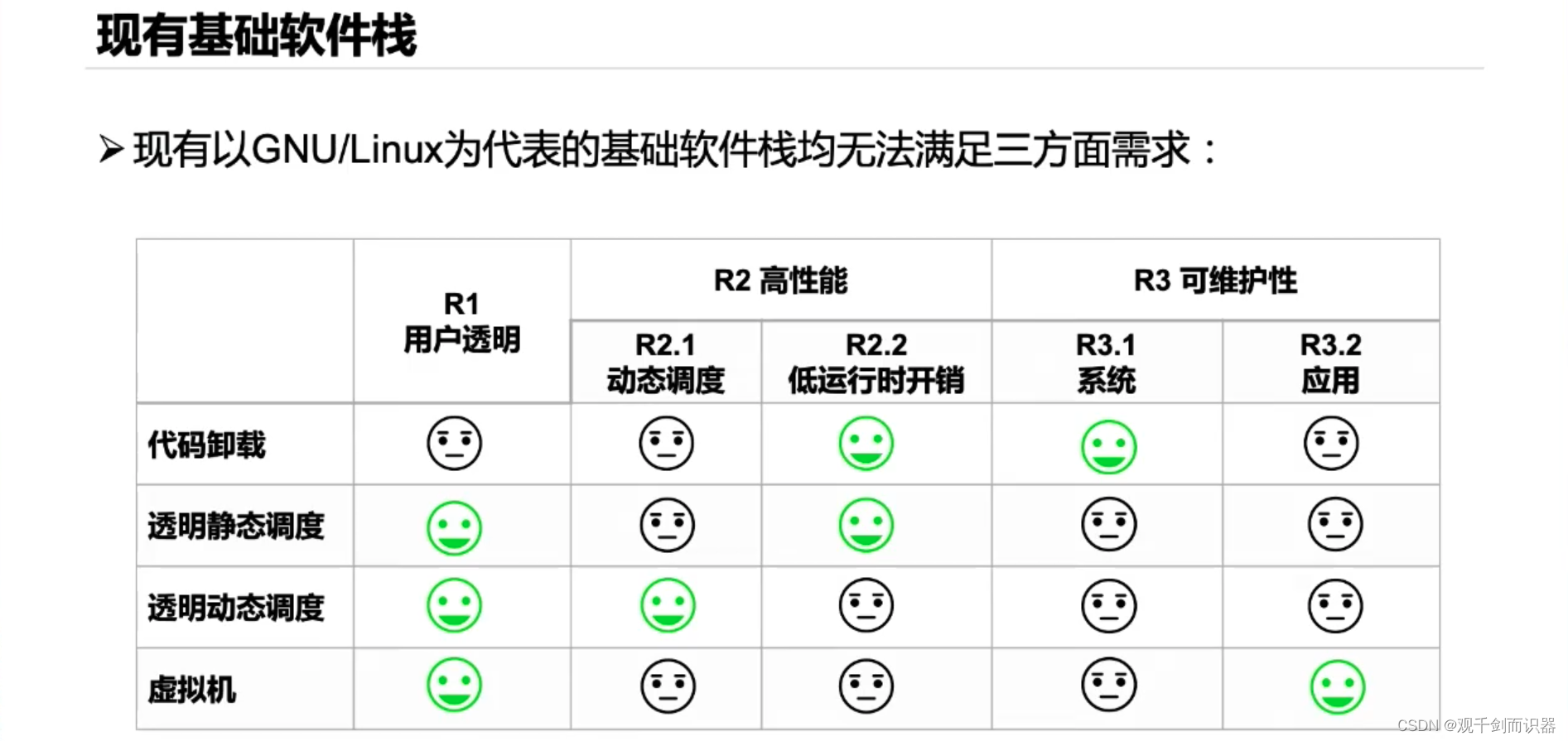

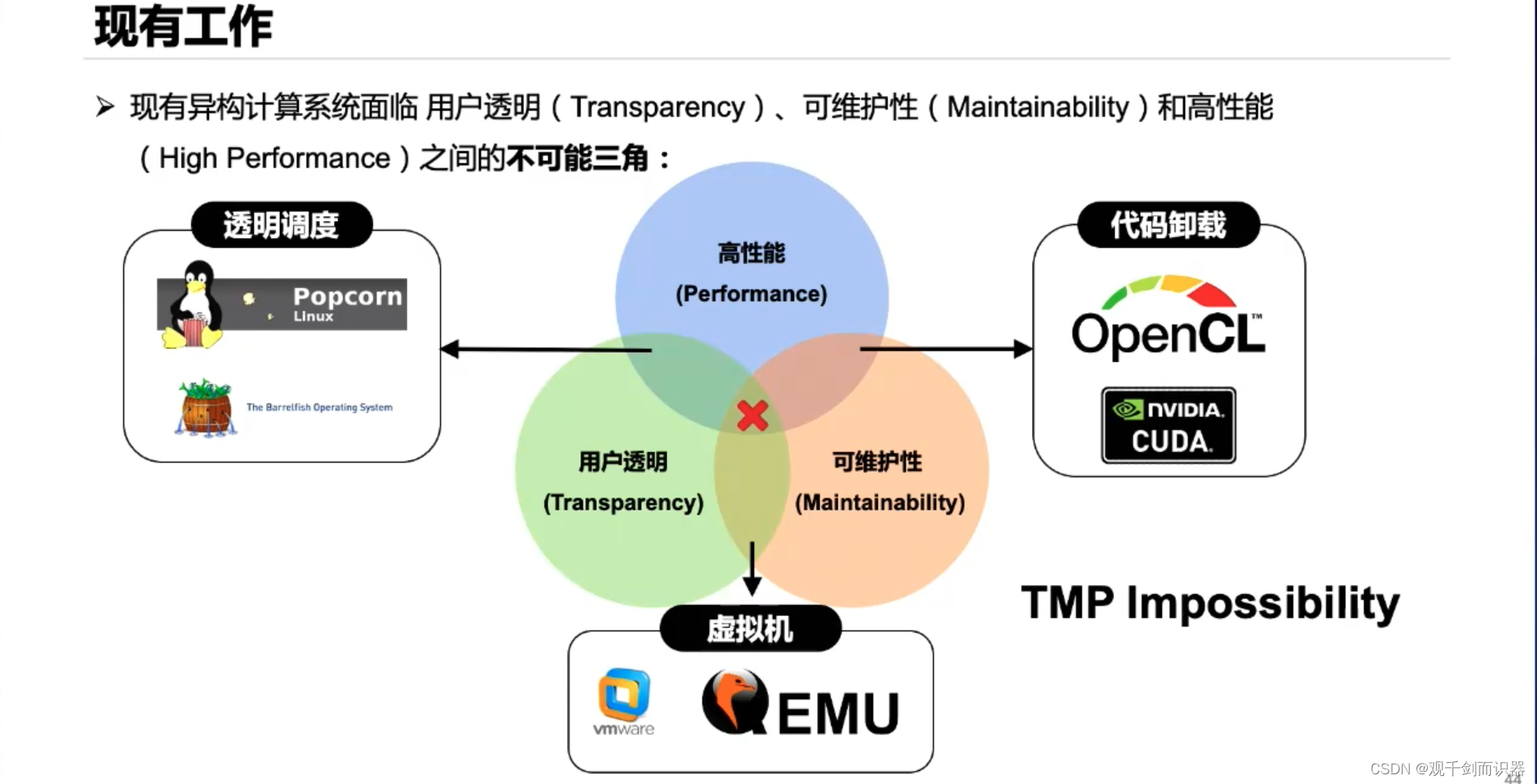

RISC-V原生基础软件栈,武延军,中国科学院软件研究所

b站视频传送门:RISC-V原生基础软件栈,武延军,中国科学院软件研究所

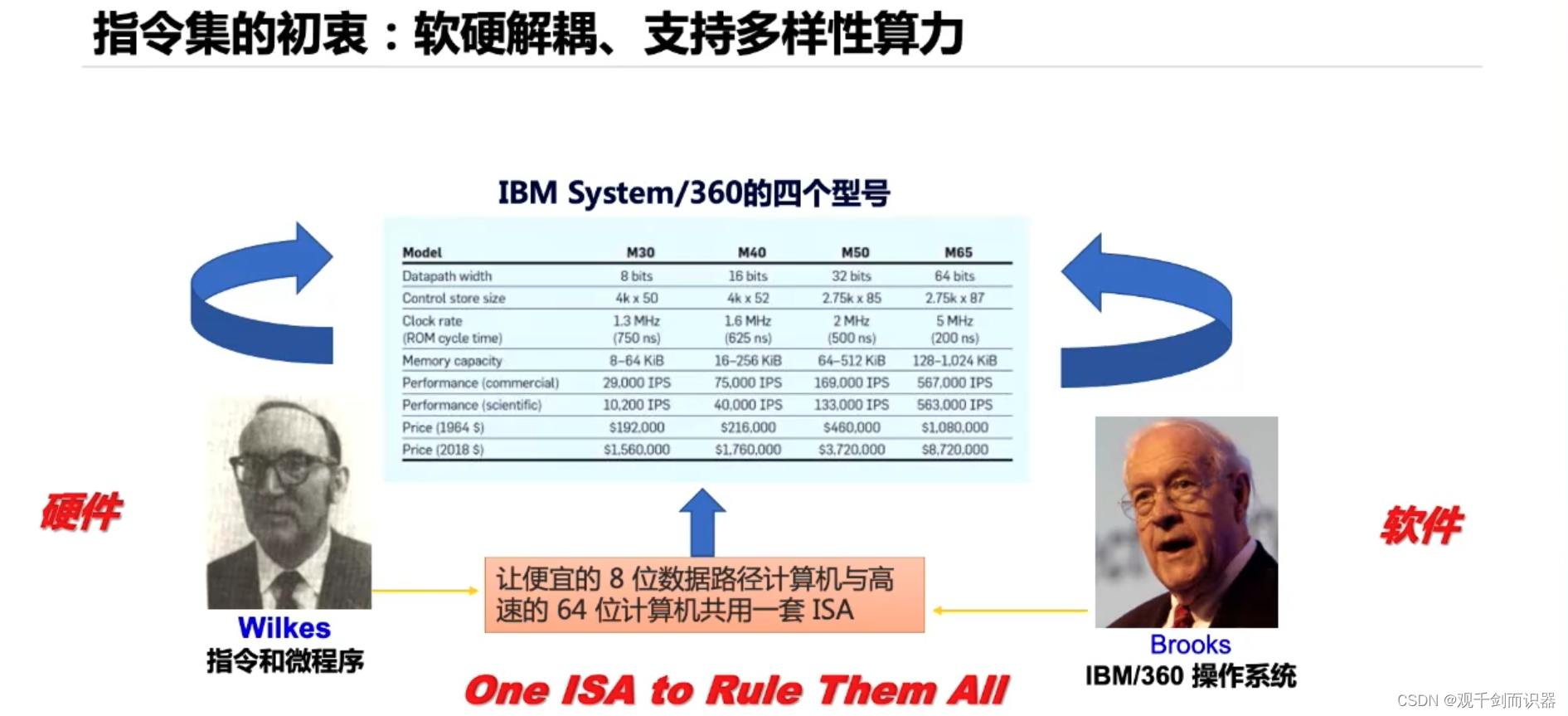

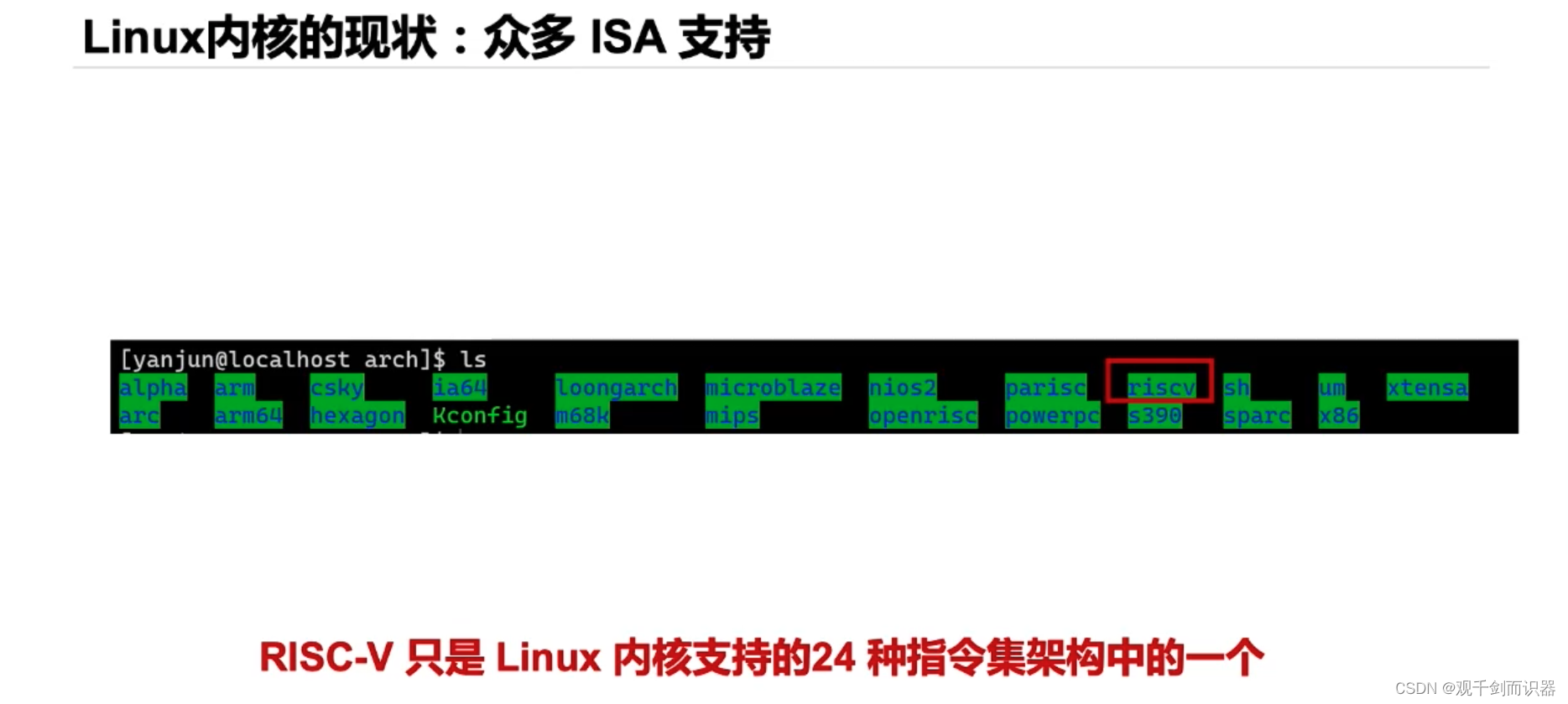

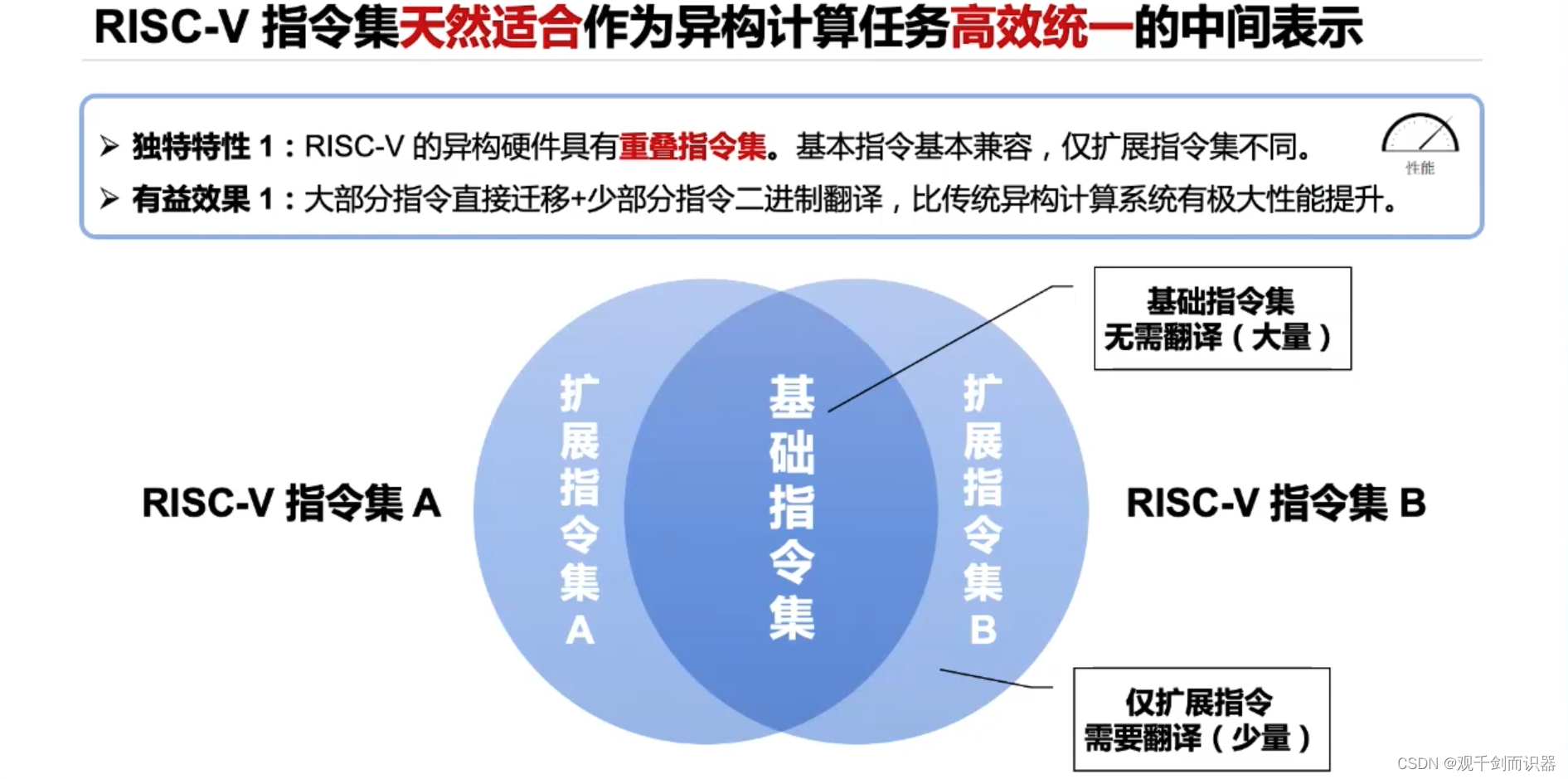

RISC-V推动新型架构创新,孟建熠,浙江大学

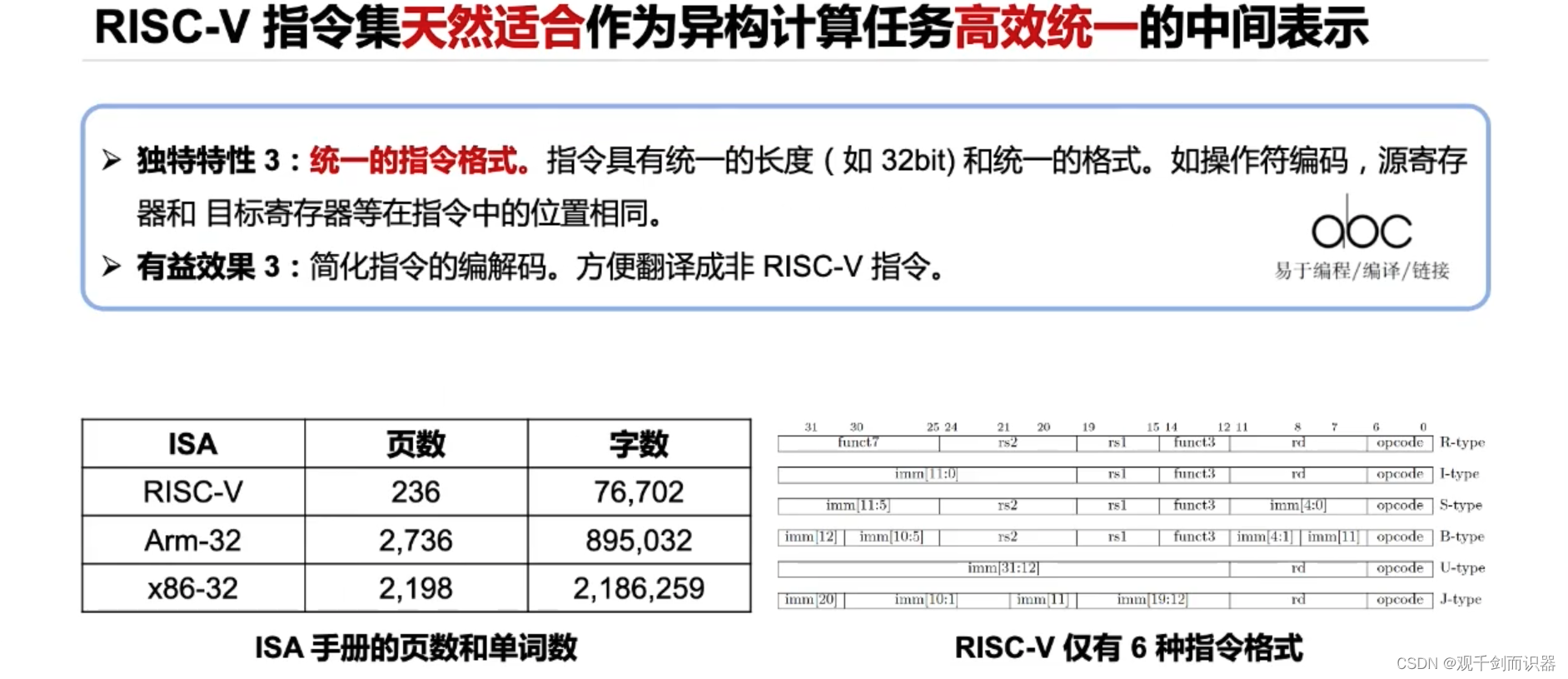

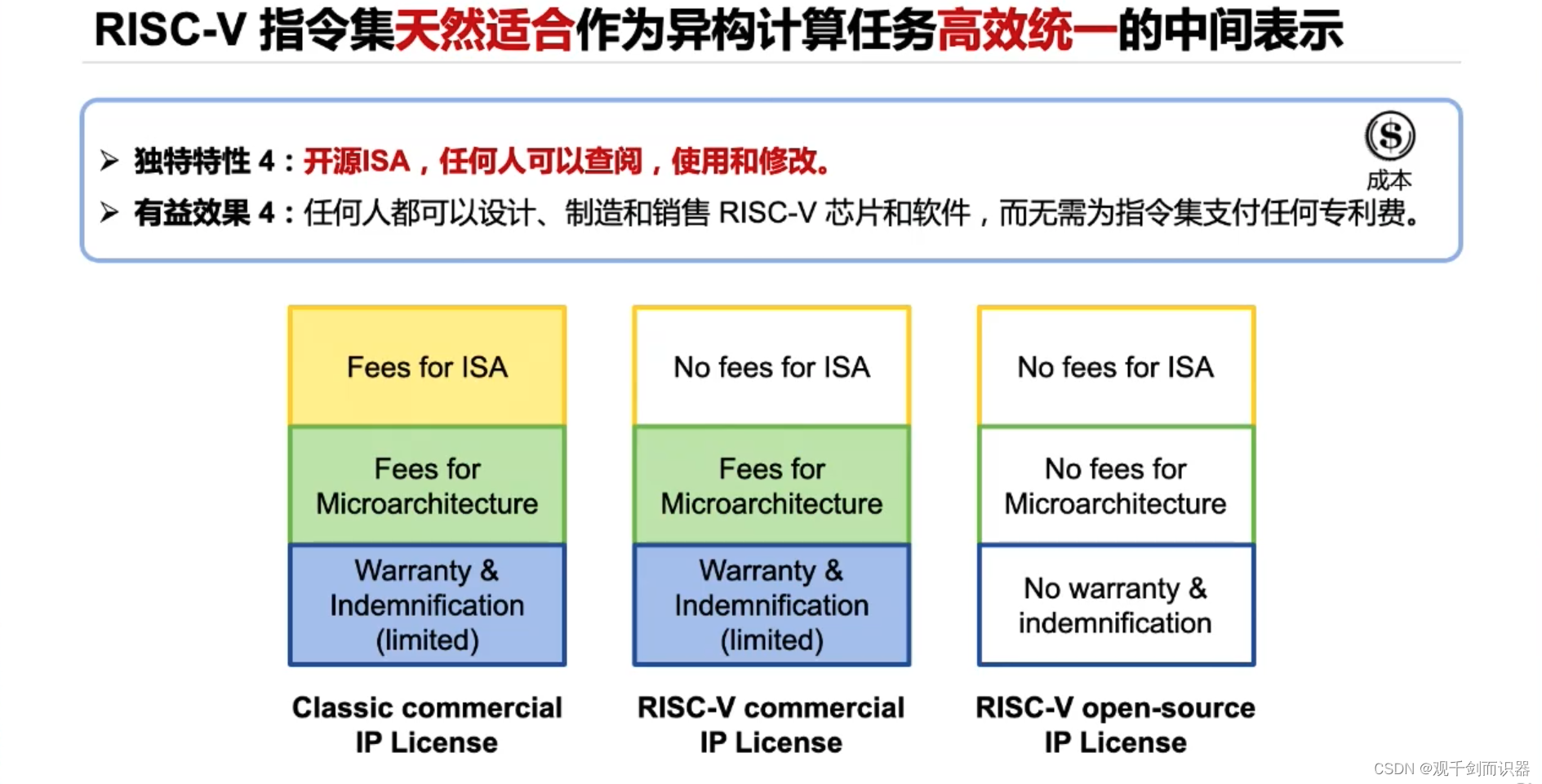

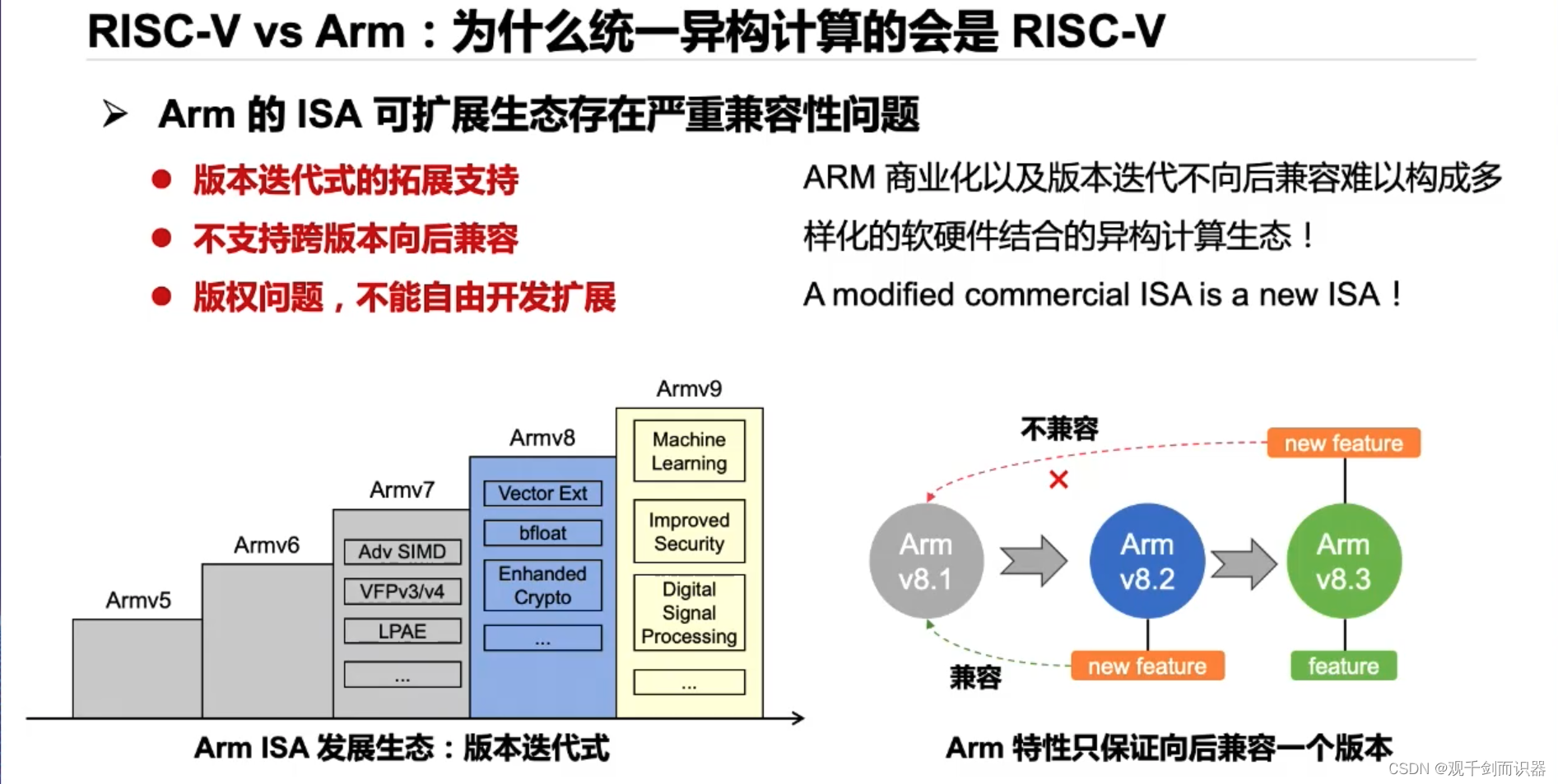

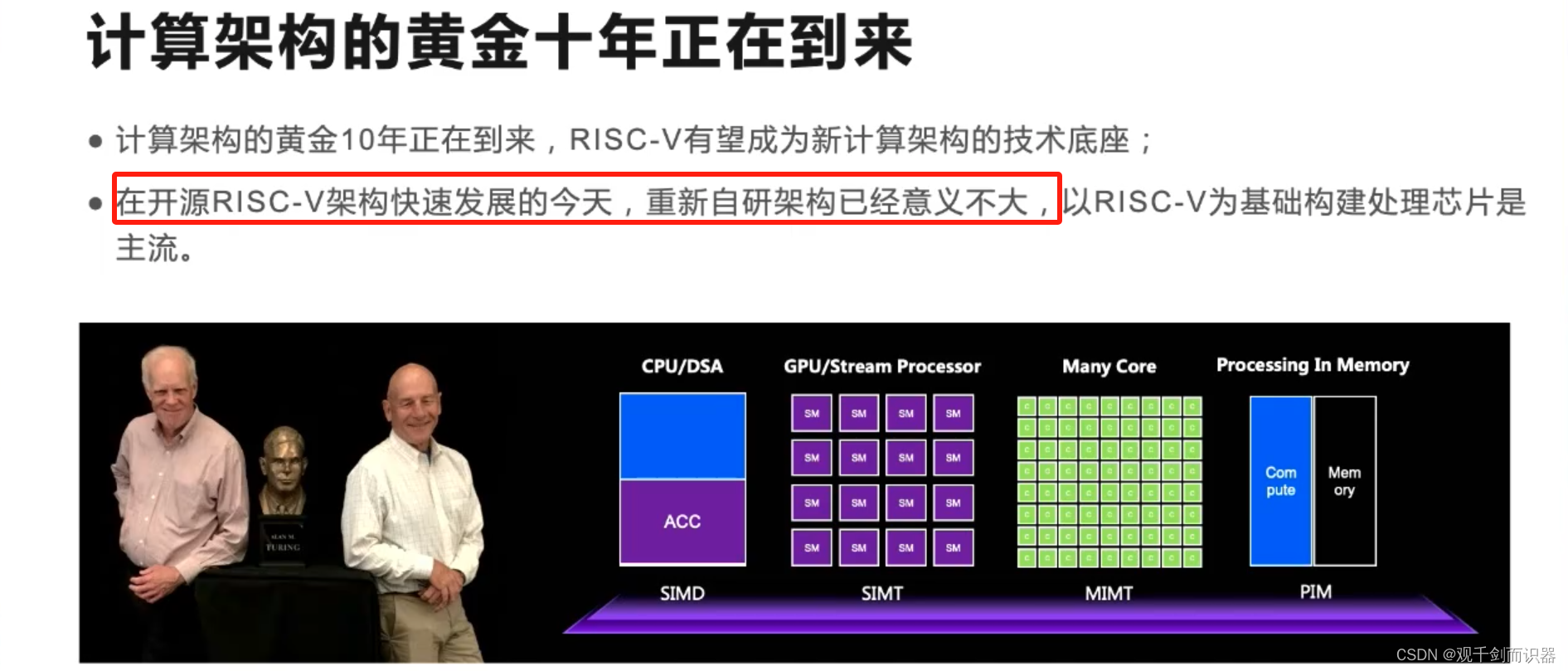

RISC-V推动新型架构创新,孟建熠,浙江大学

专题一:开源芯片

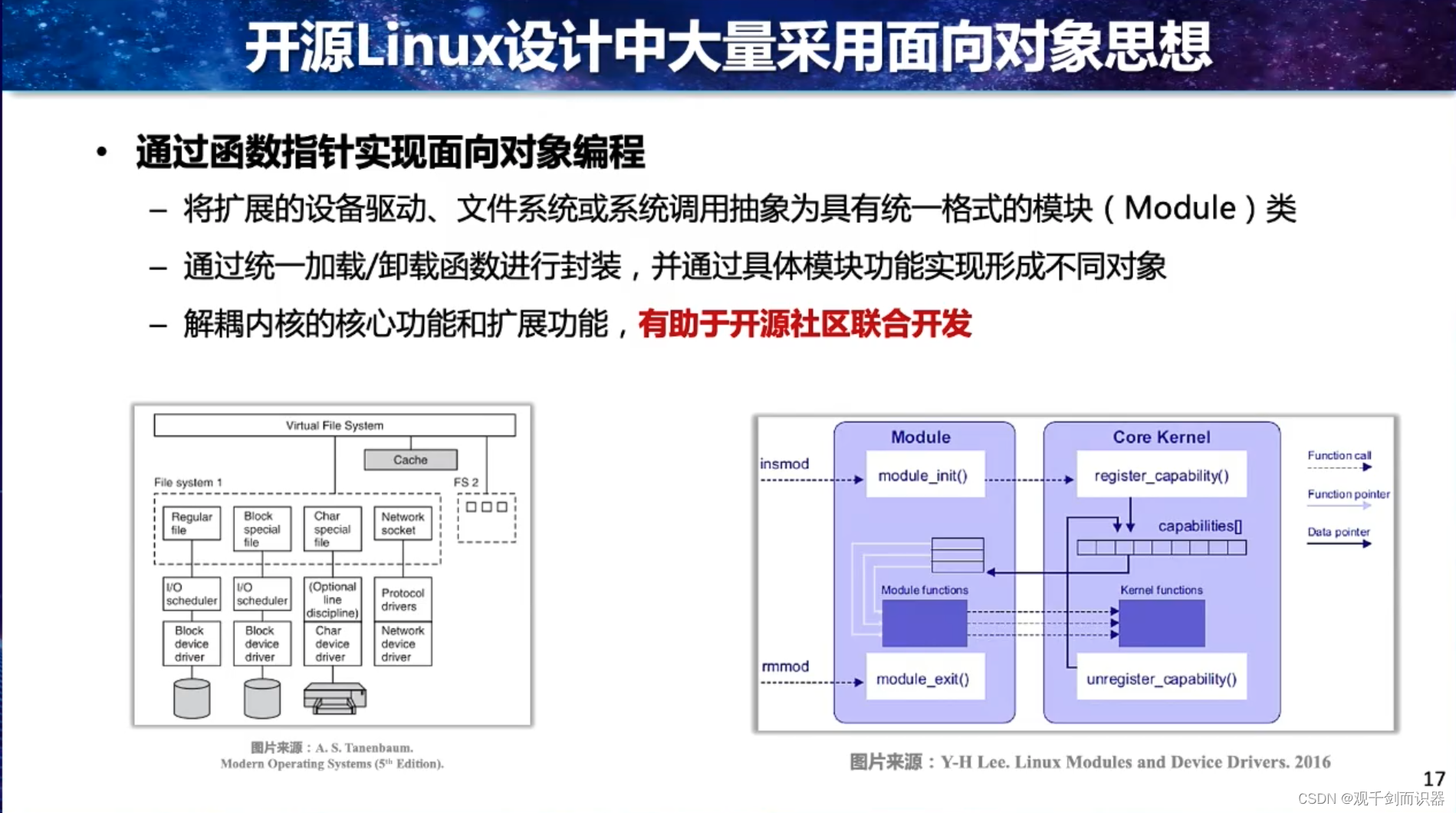

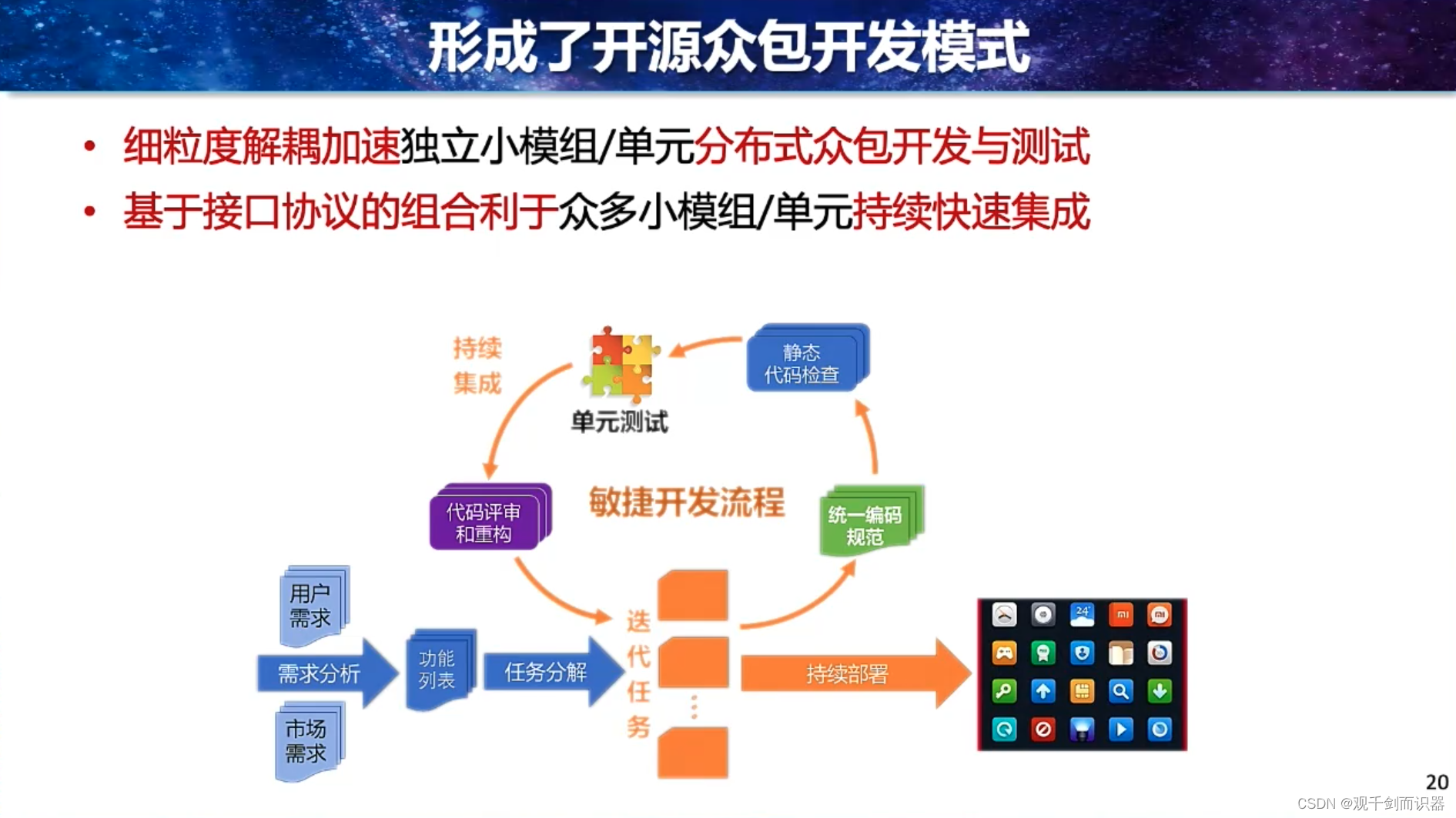

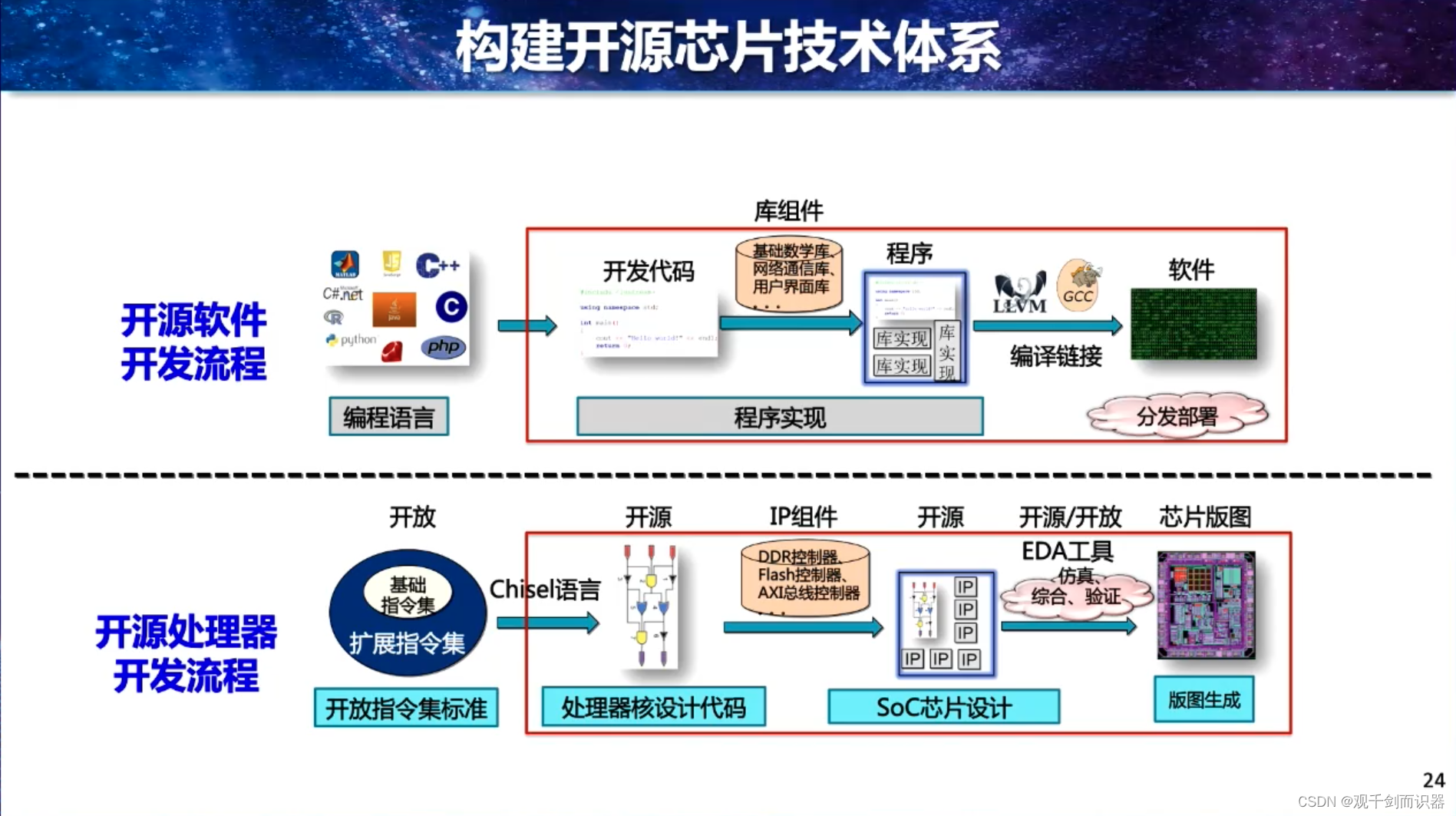

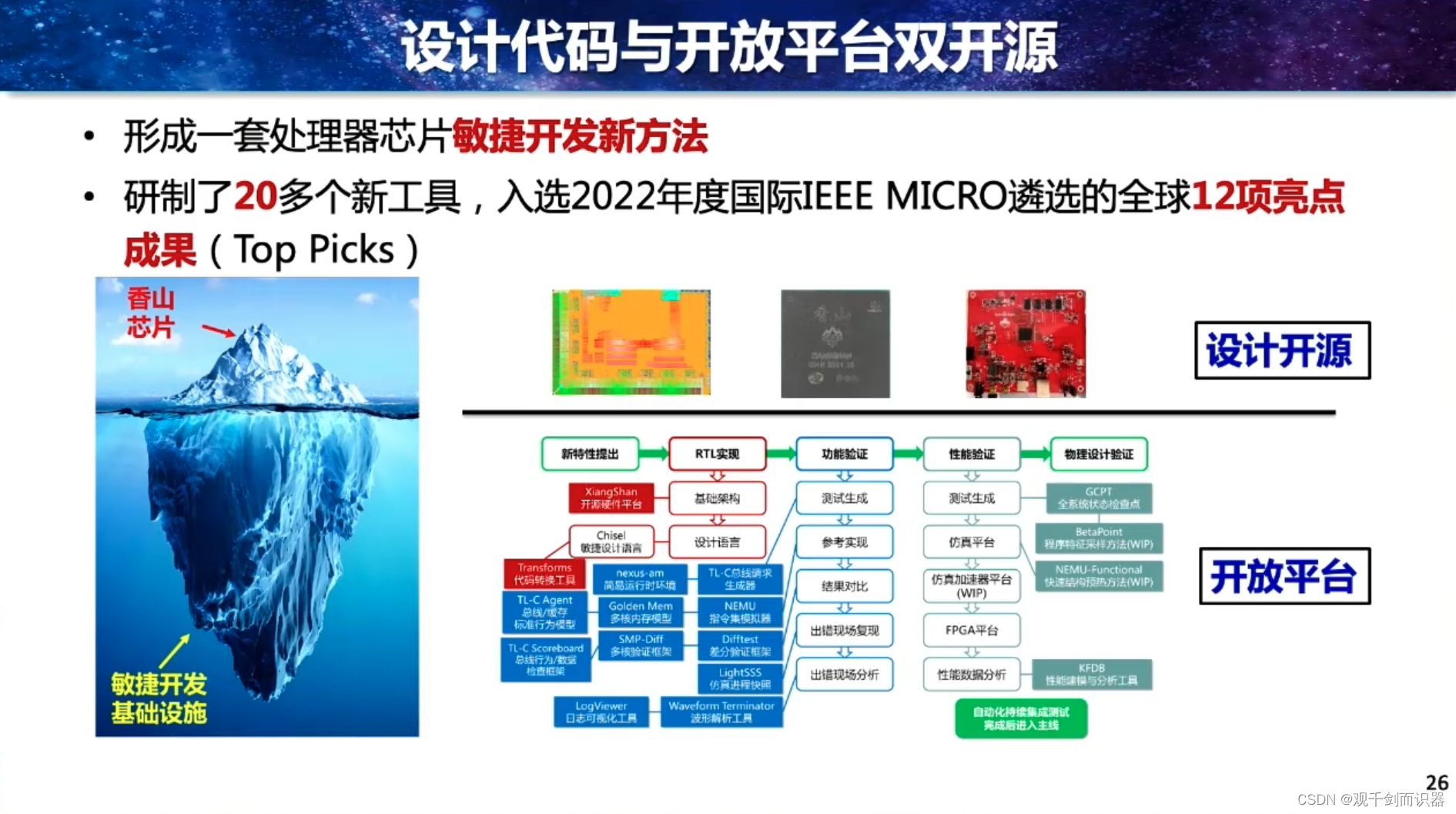

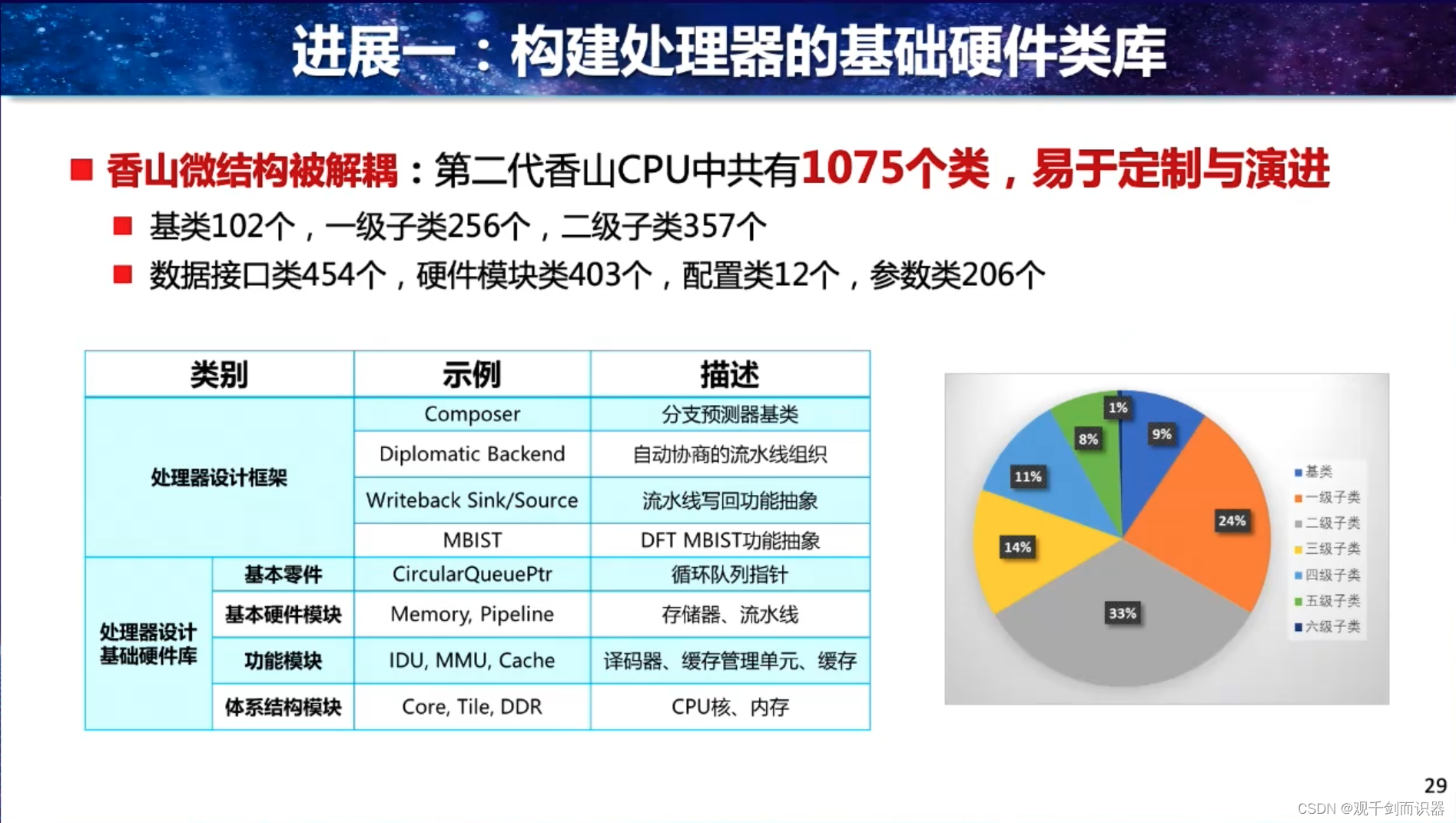

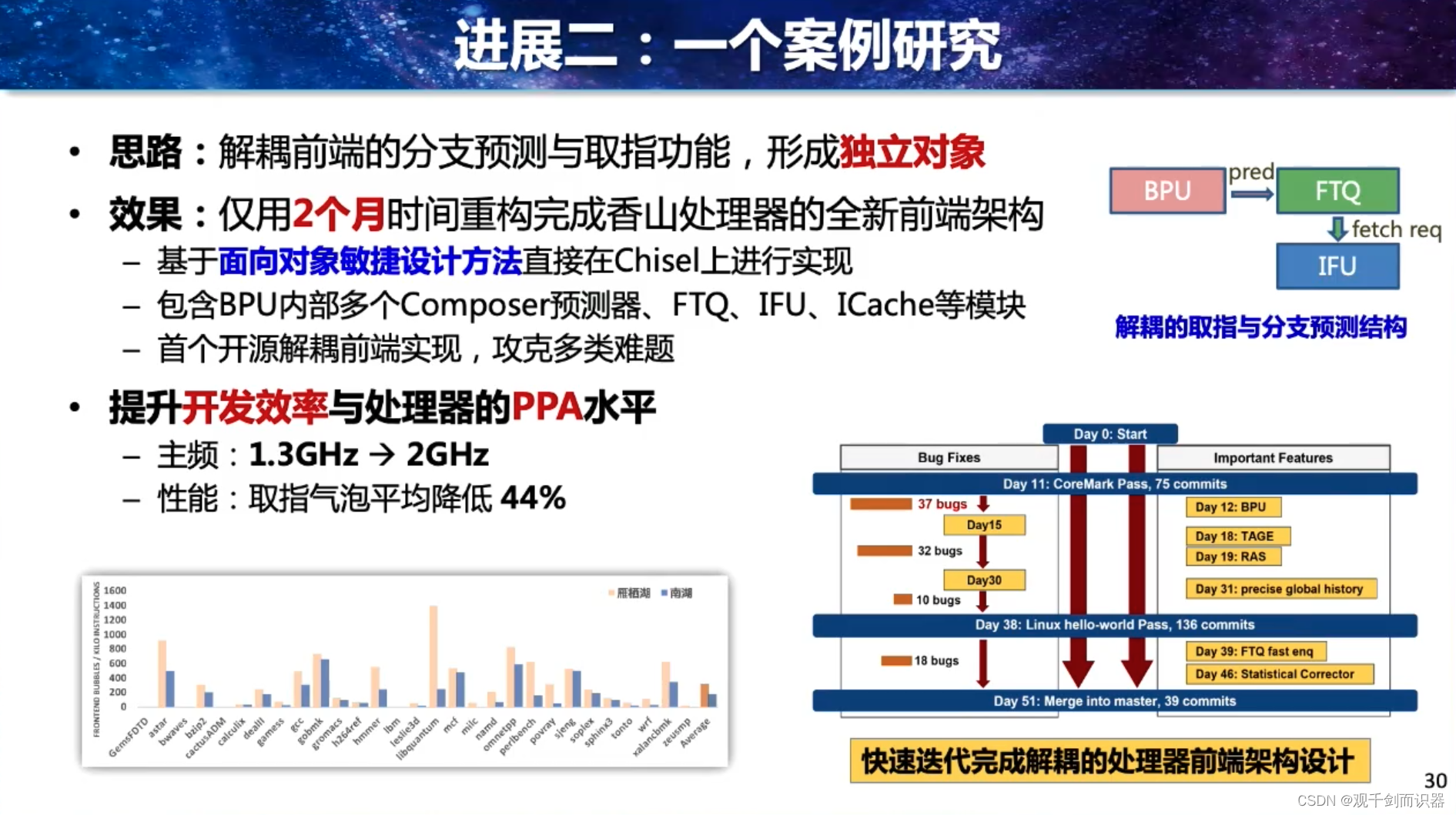

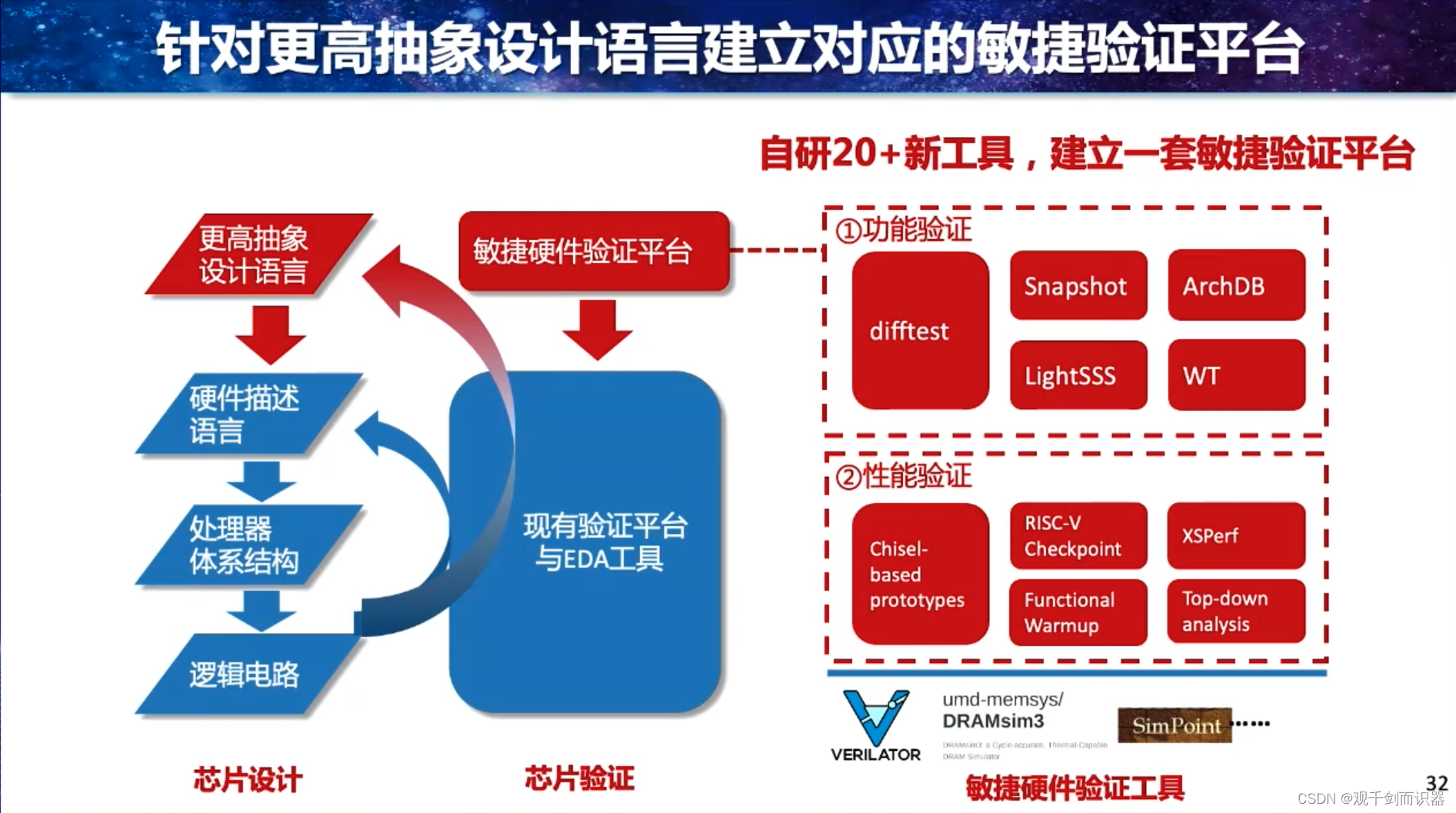

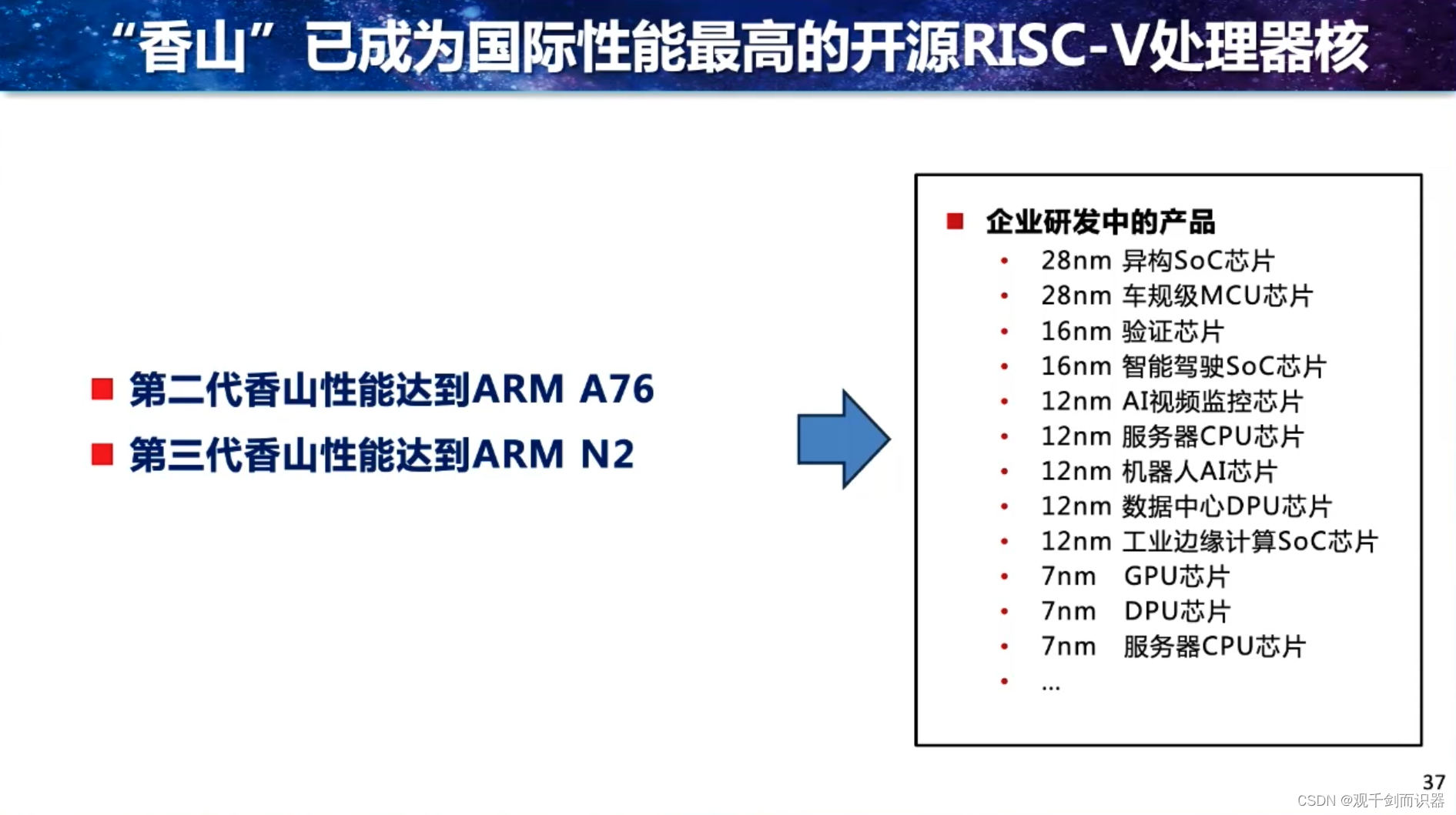

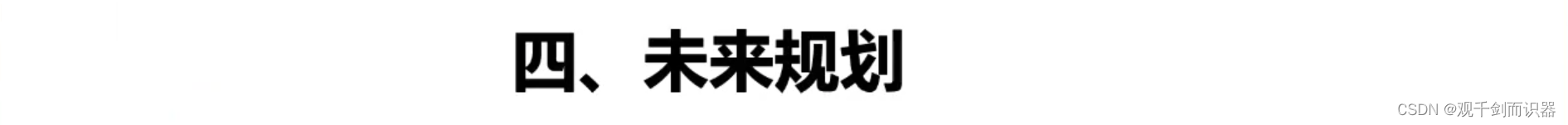

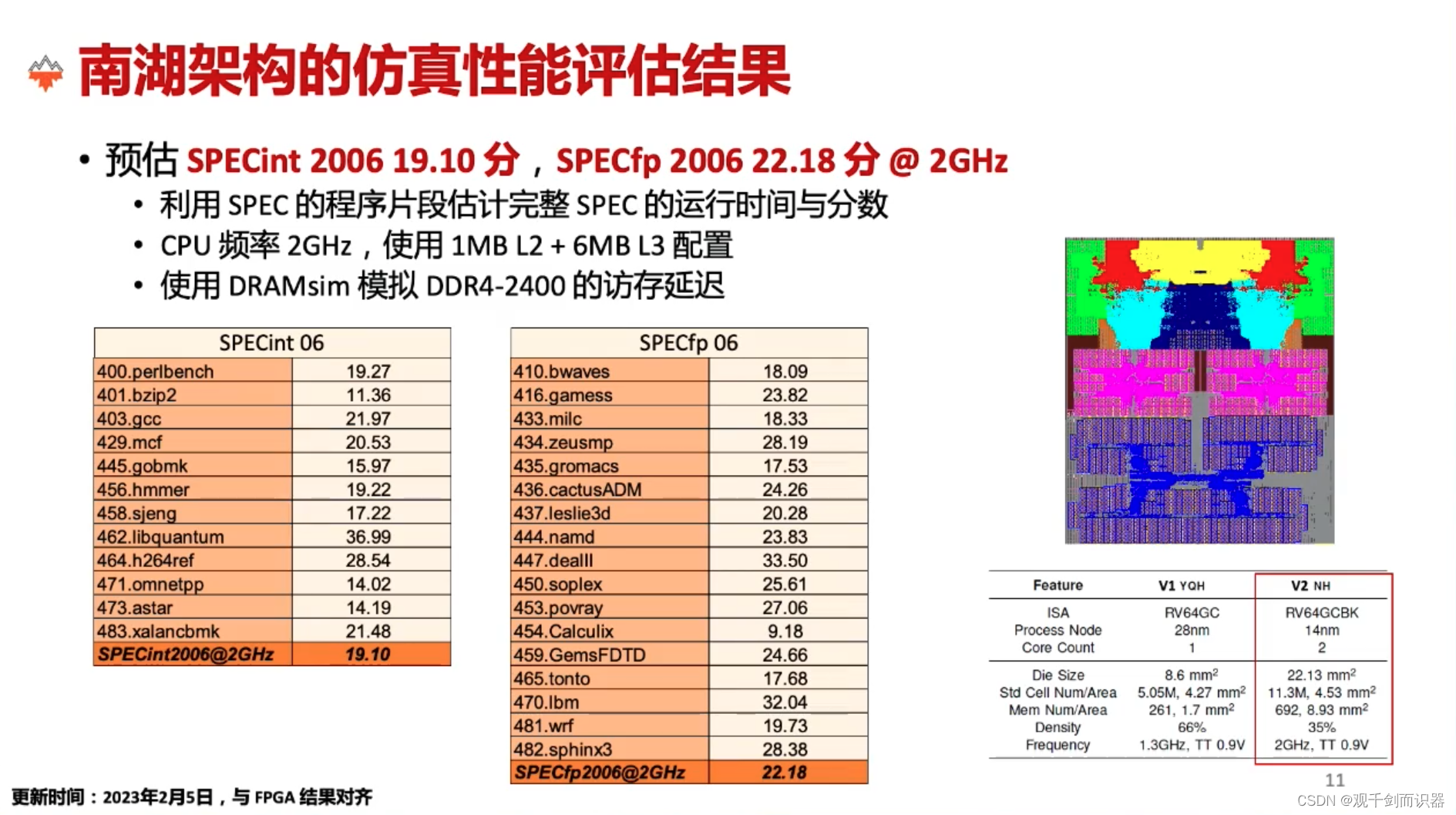

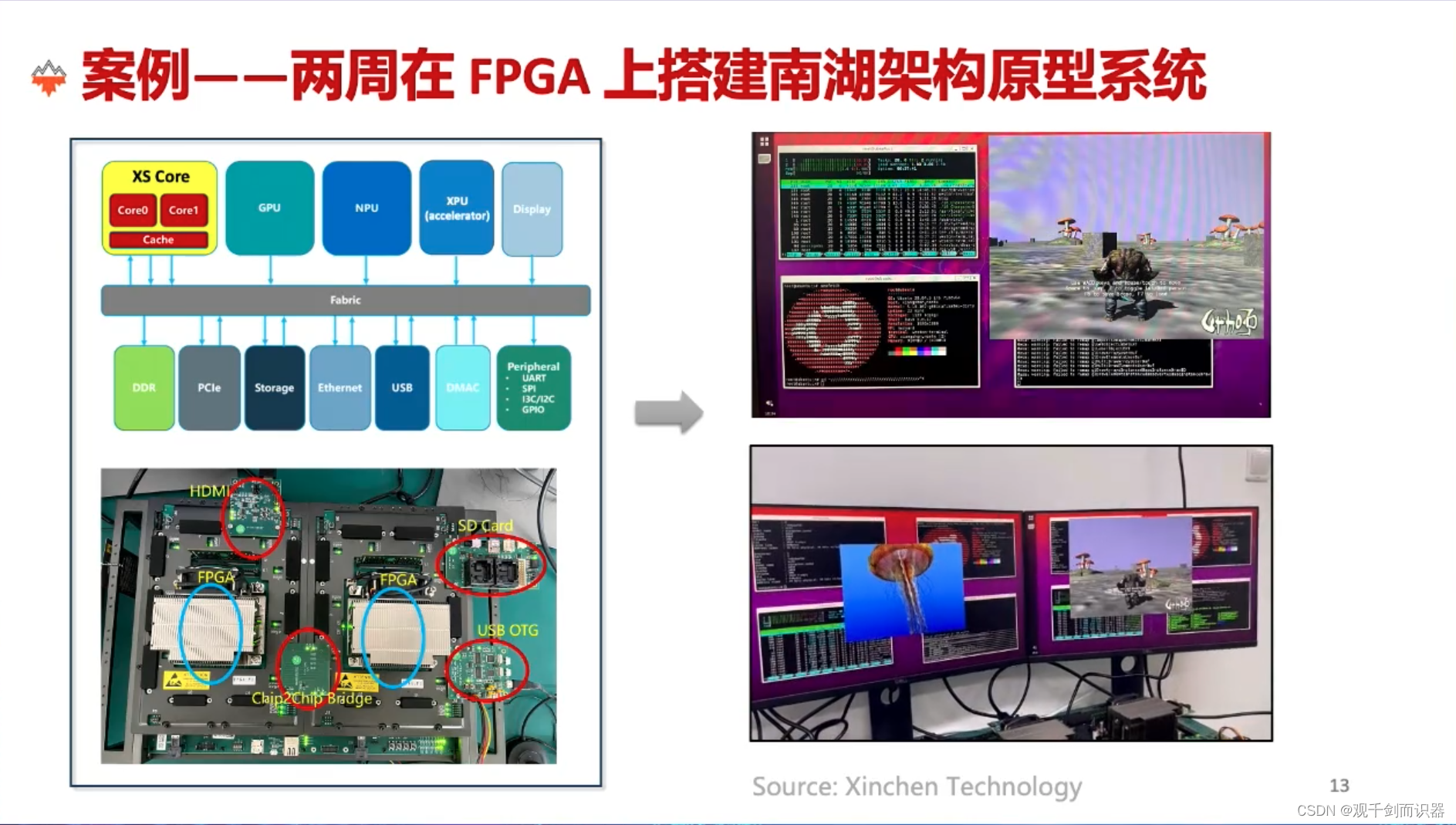

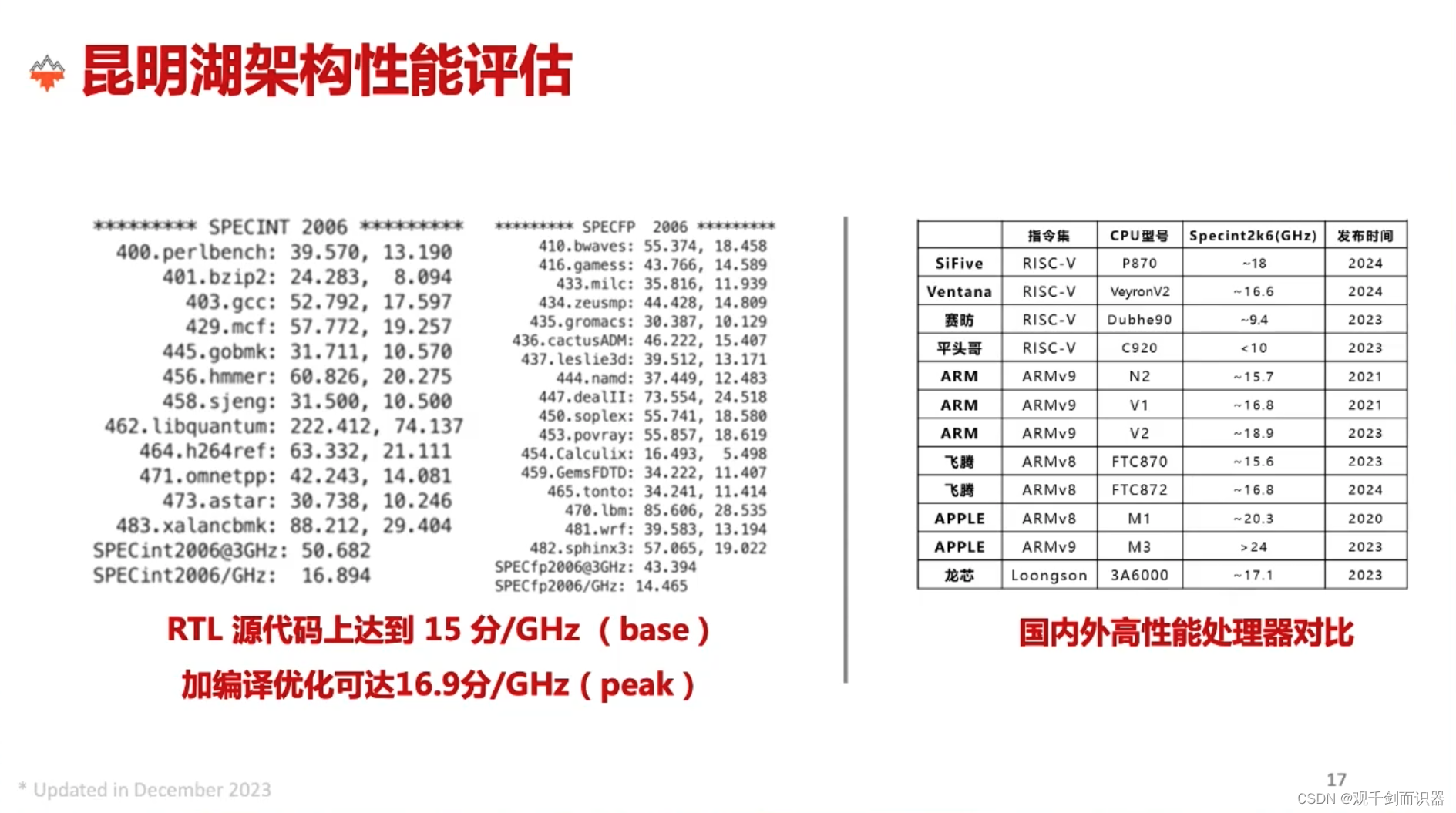

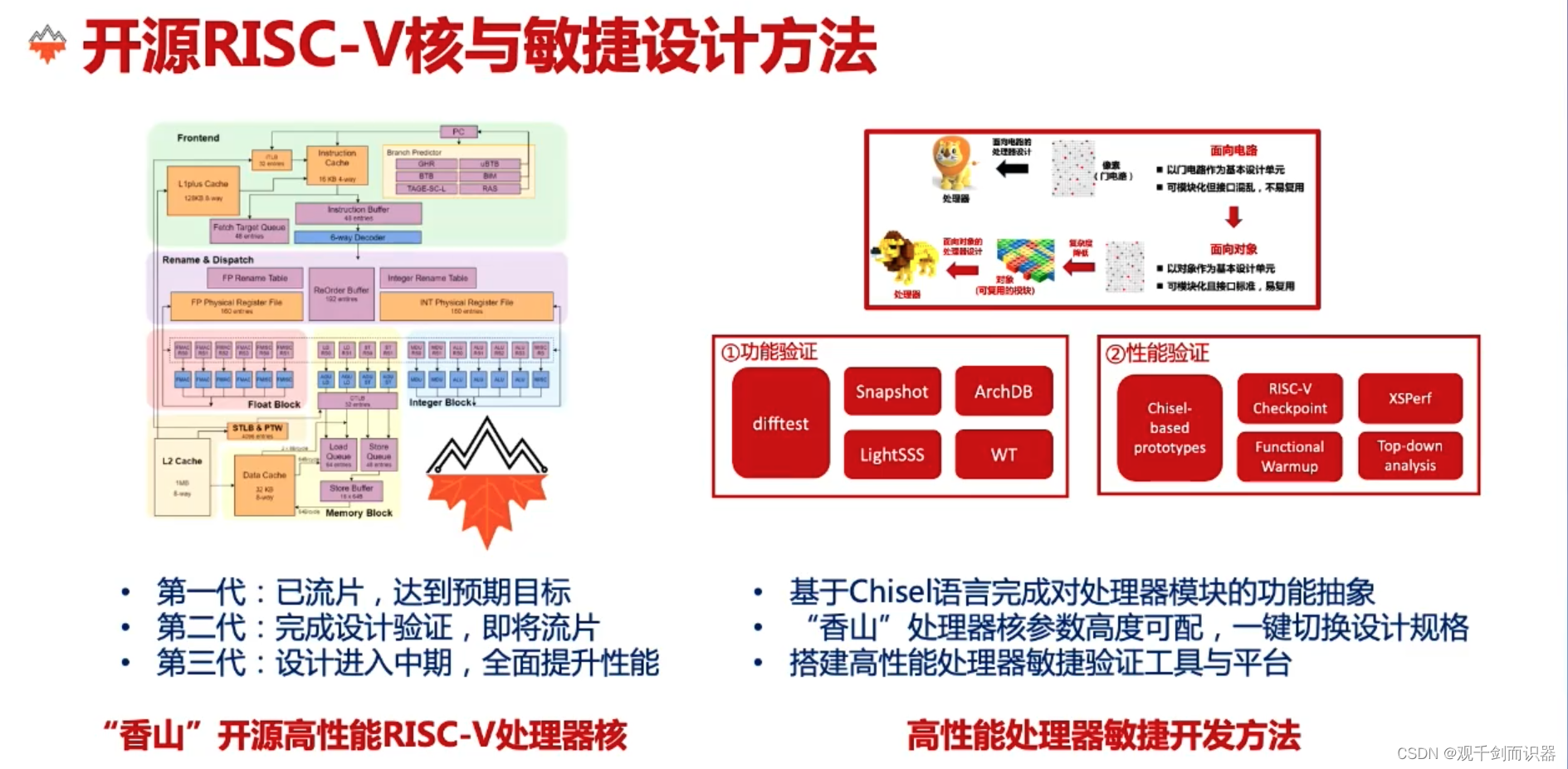

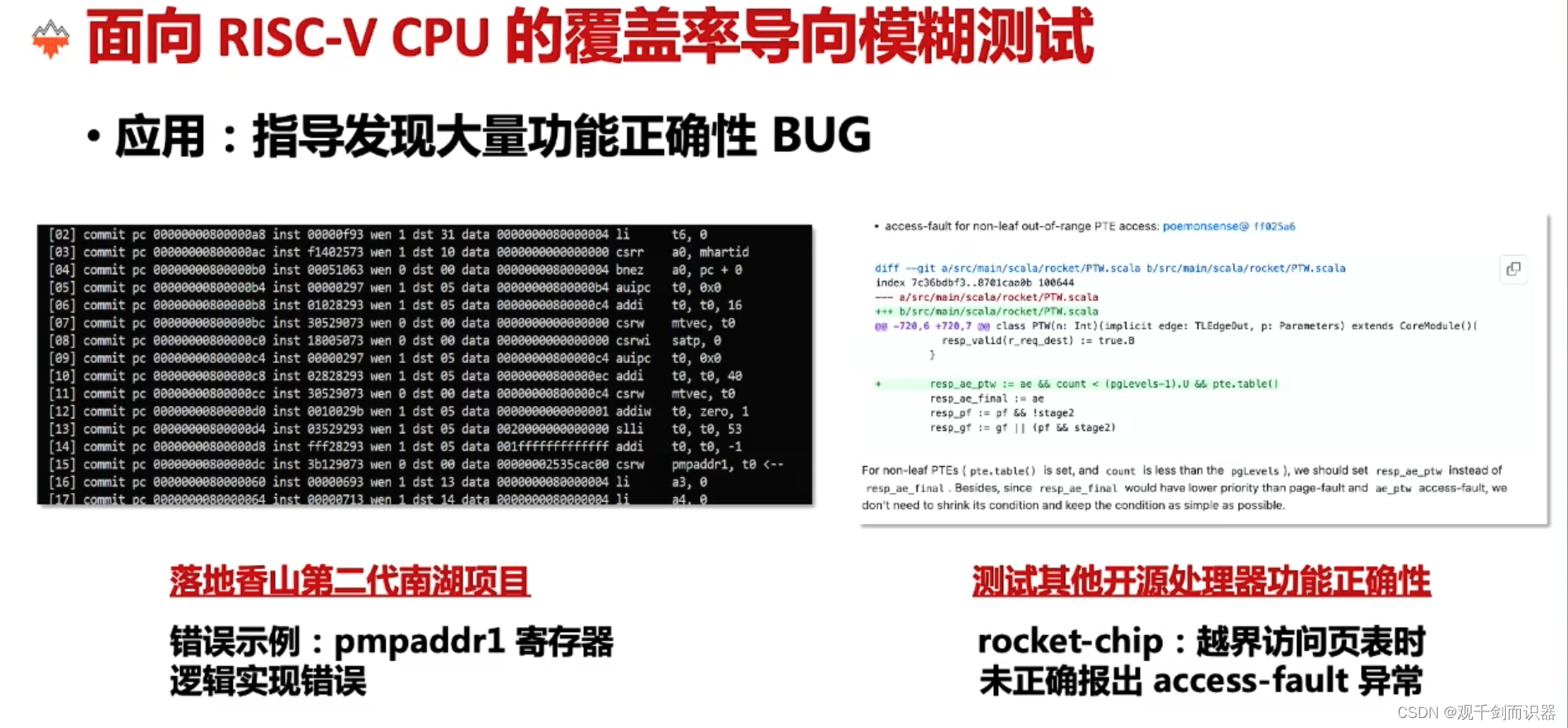

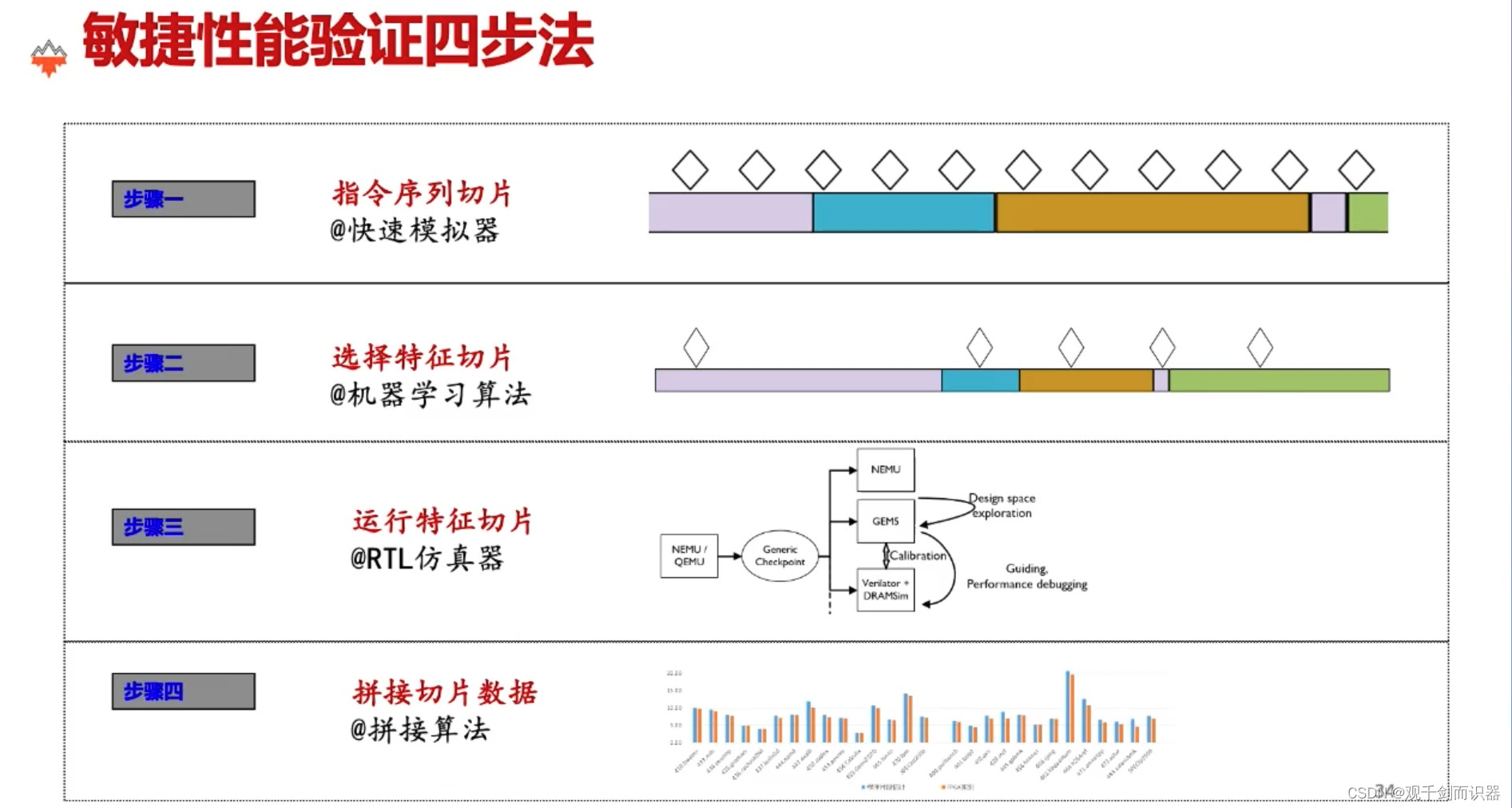

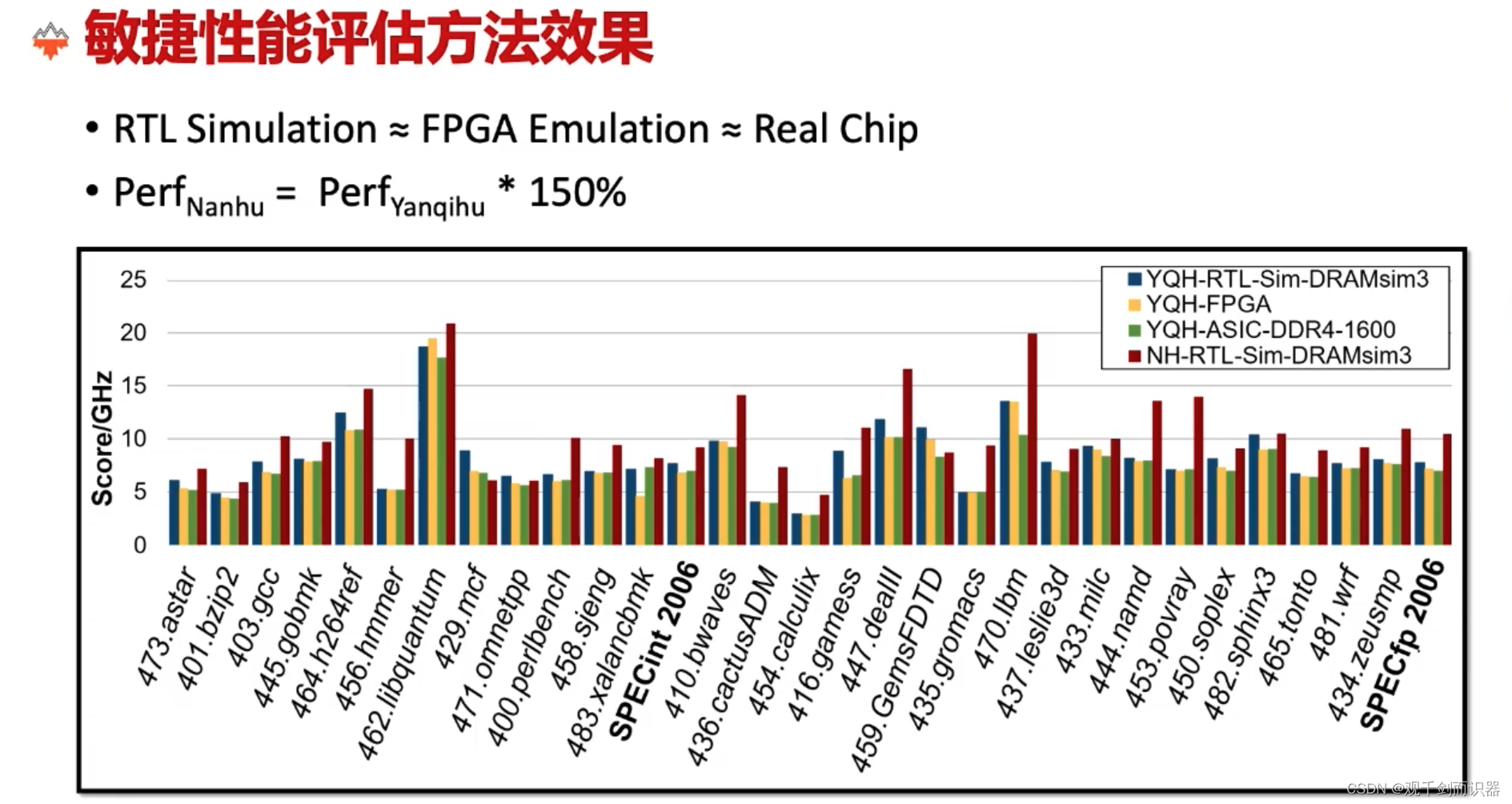

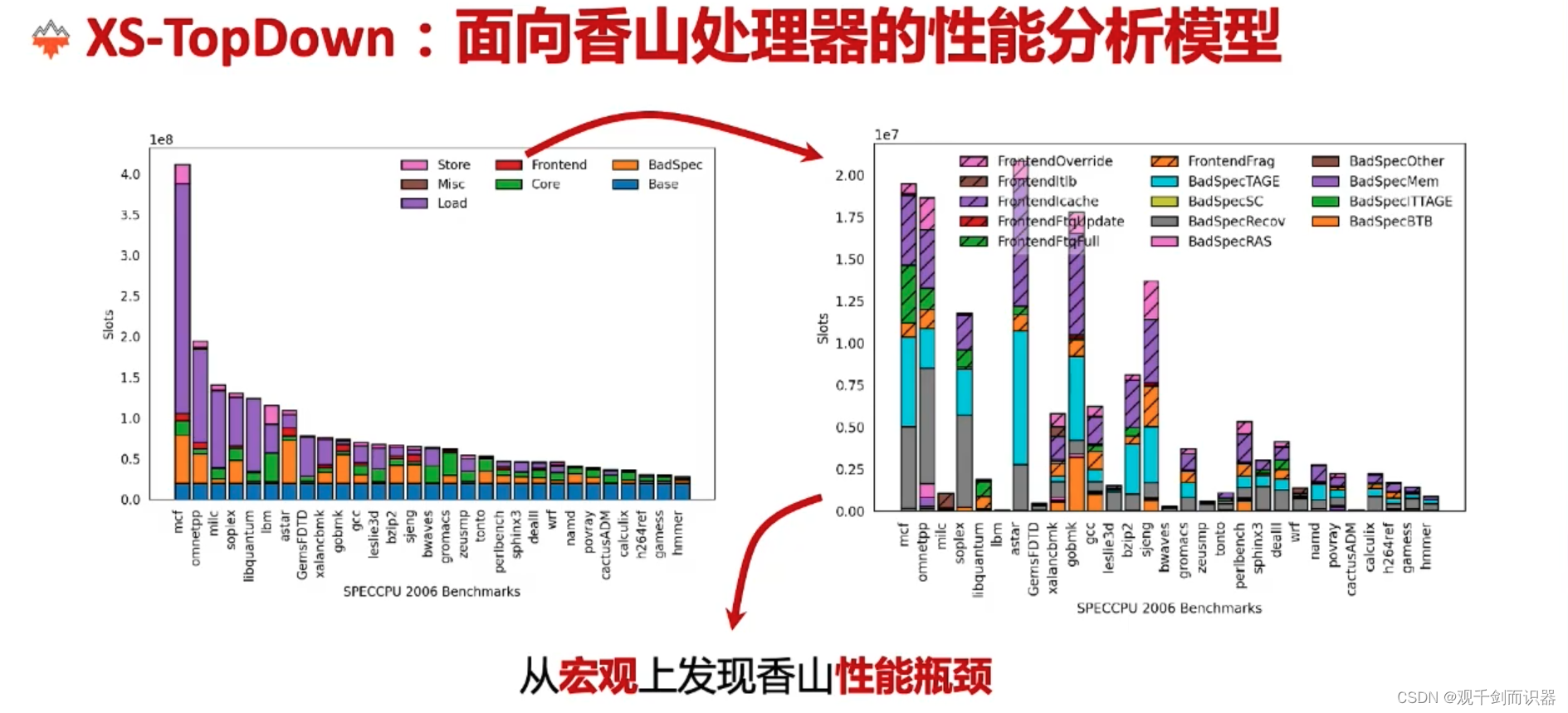

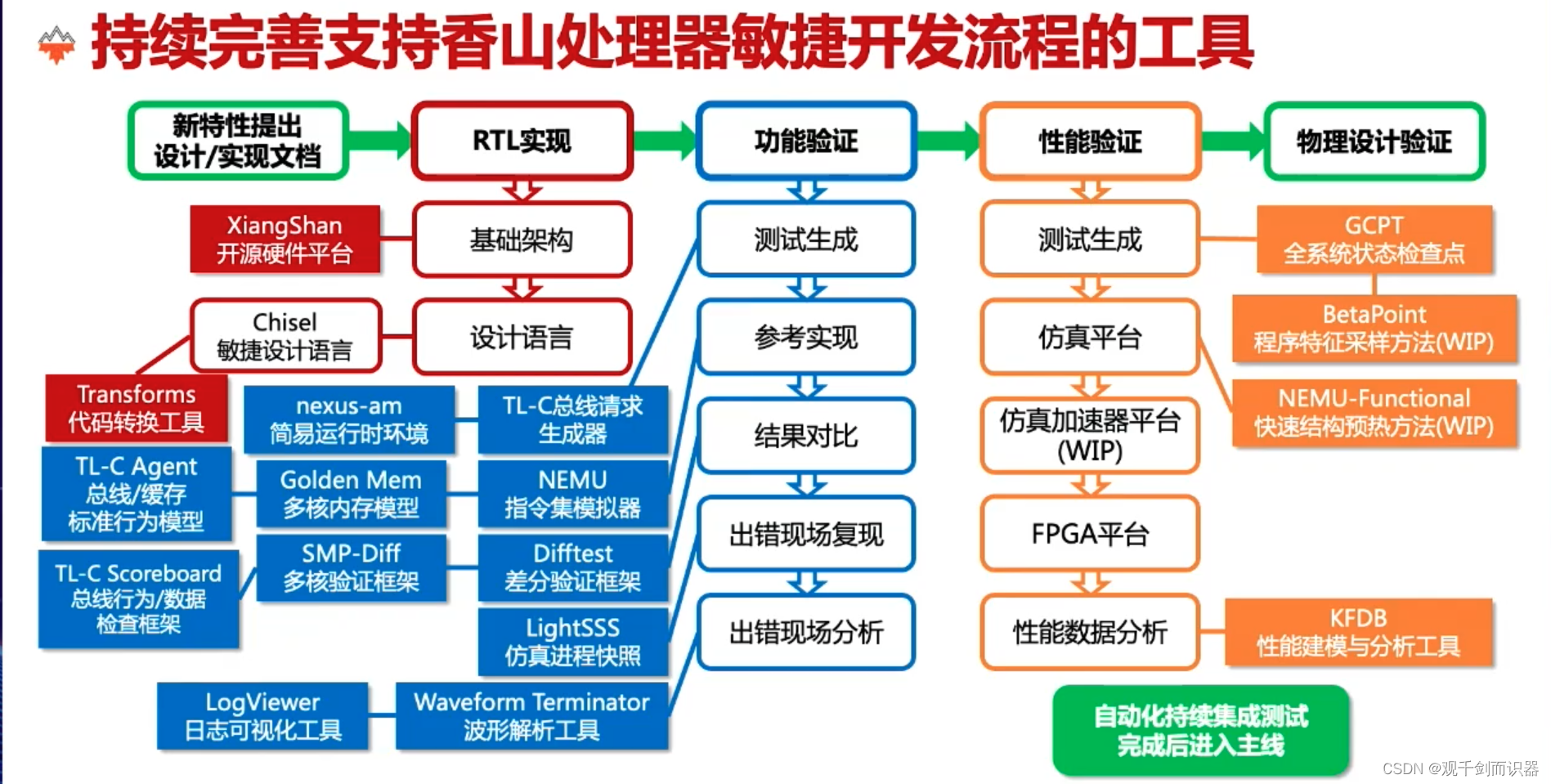

开源高性能 RISC-V 处理器核香山开发实践,包云岗,香山团队

开源高性能 RISC-V 处理器核香山开发实践,包云岗,香山团队

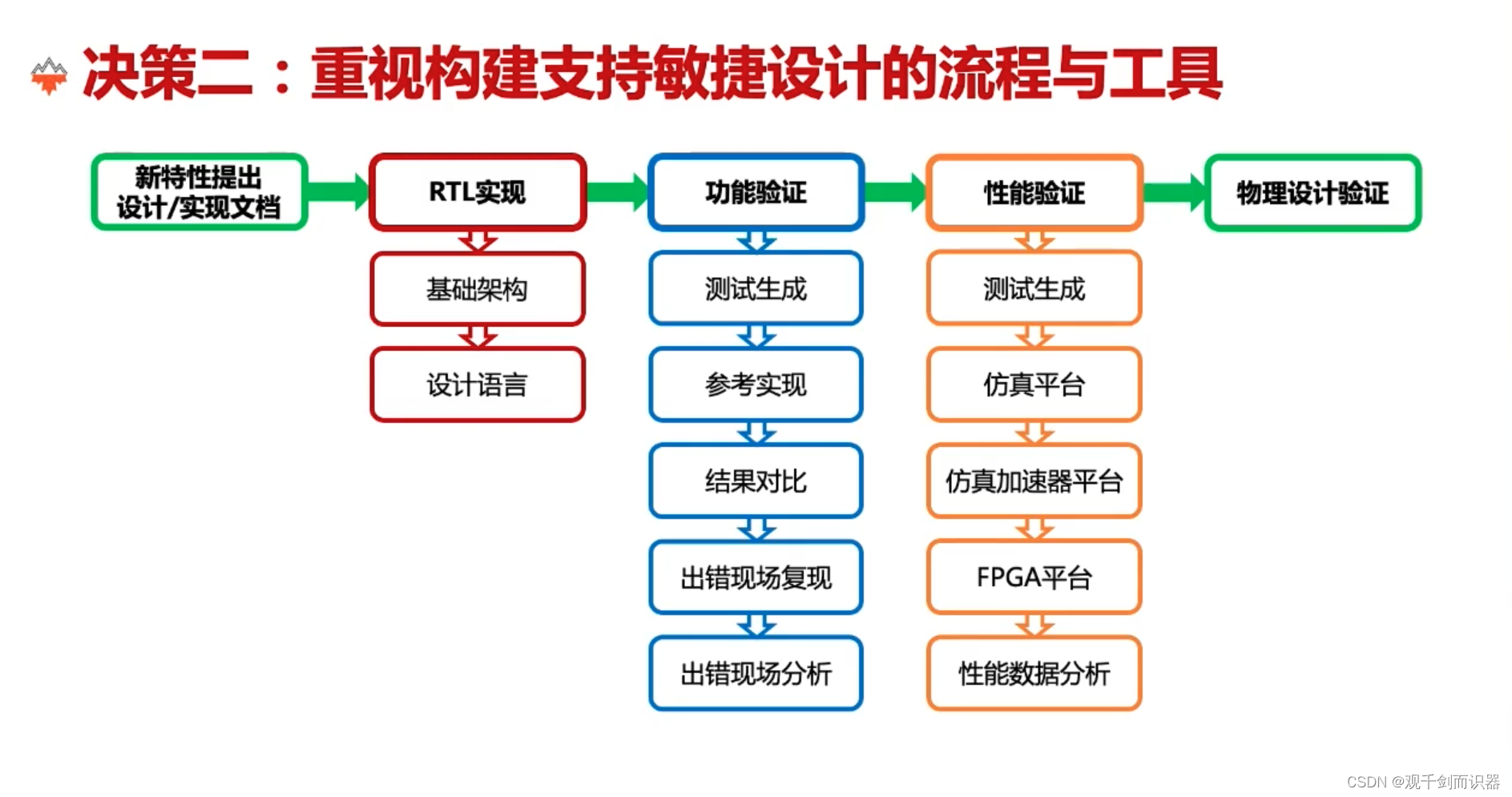

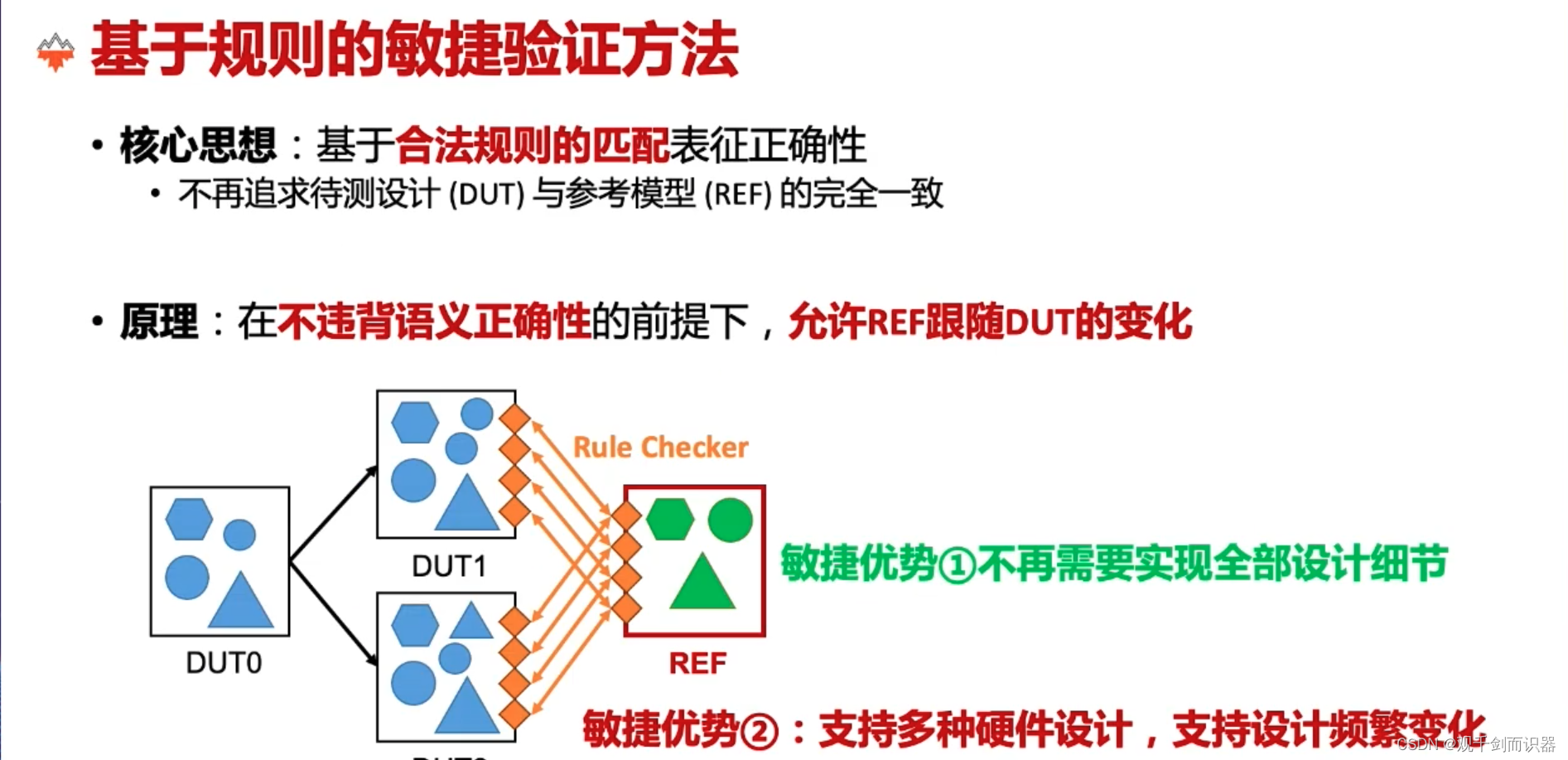

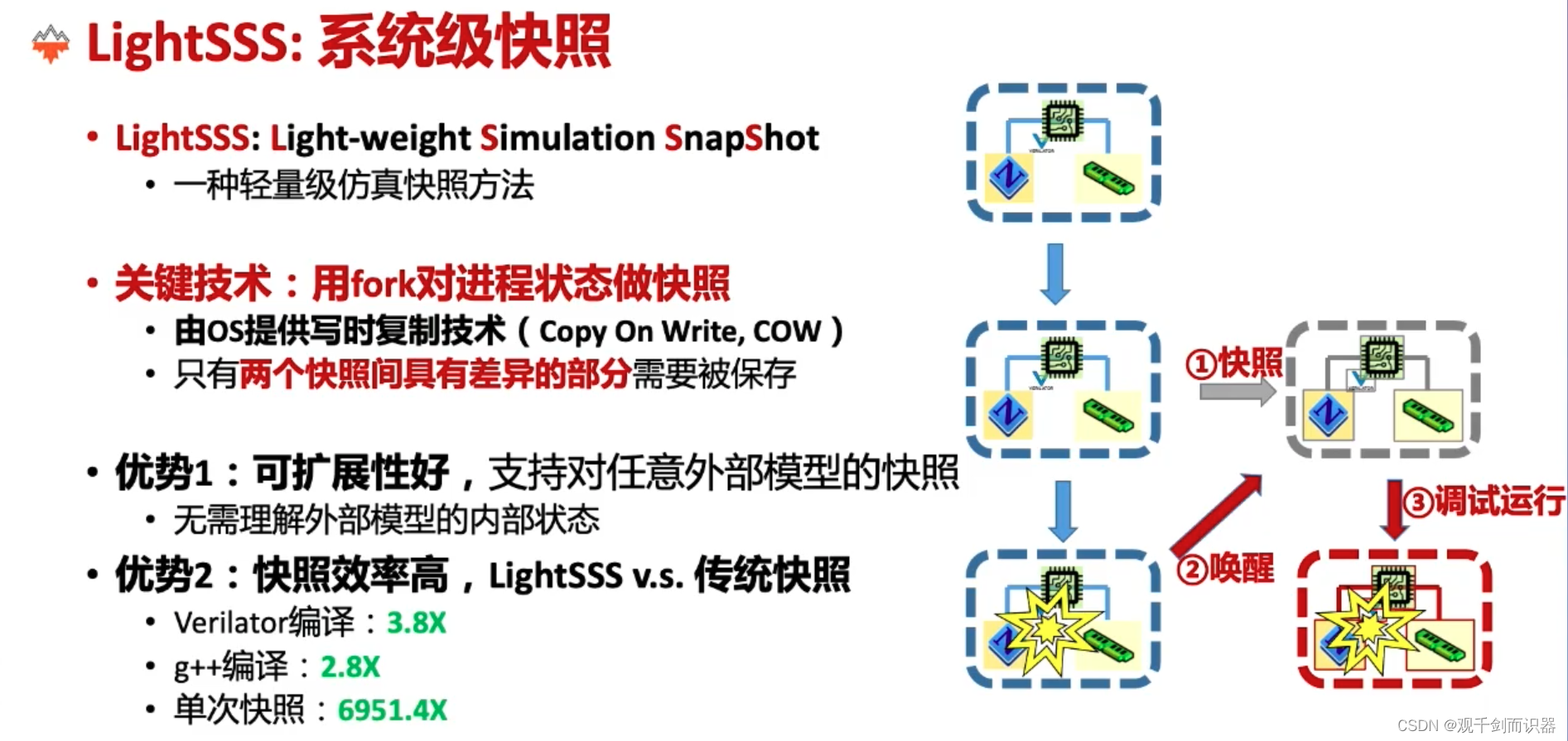

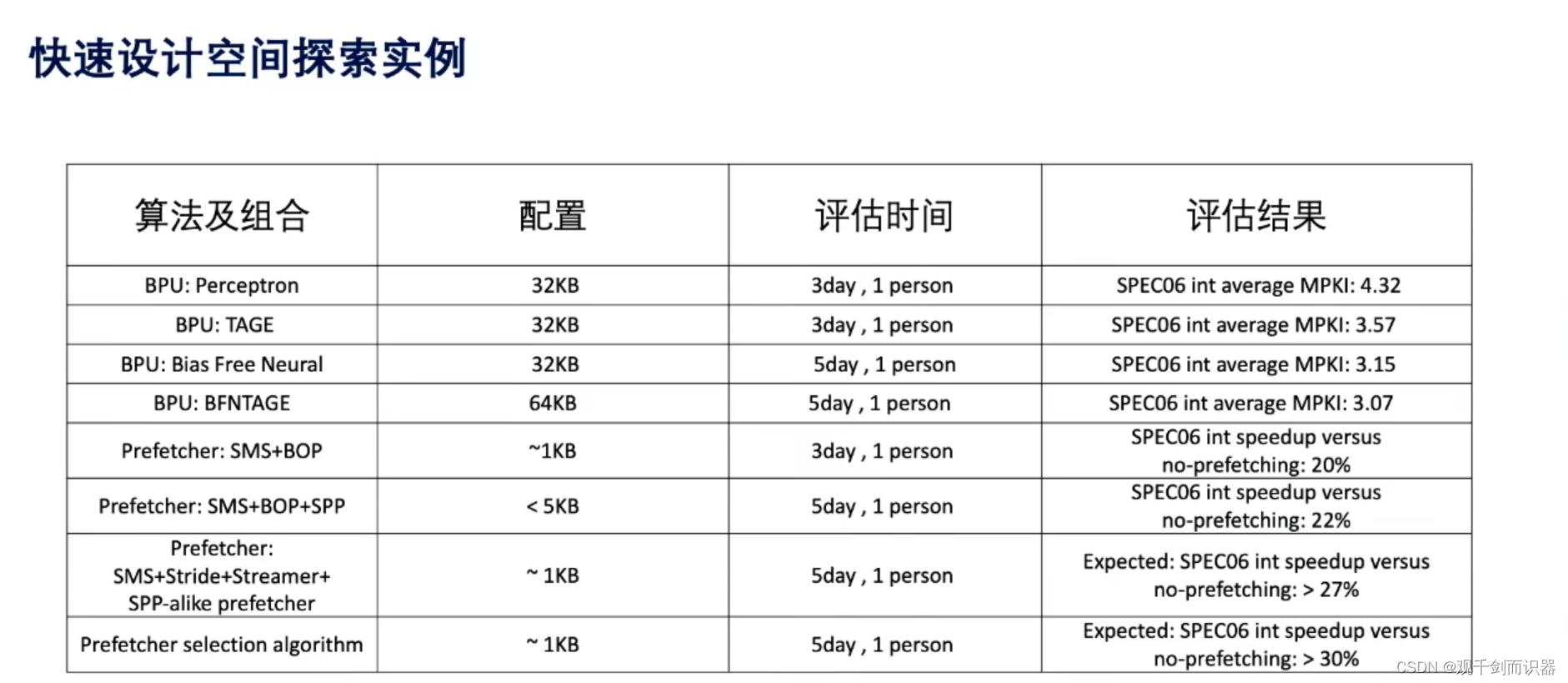

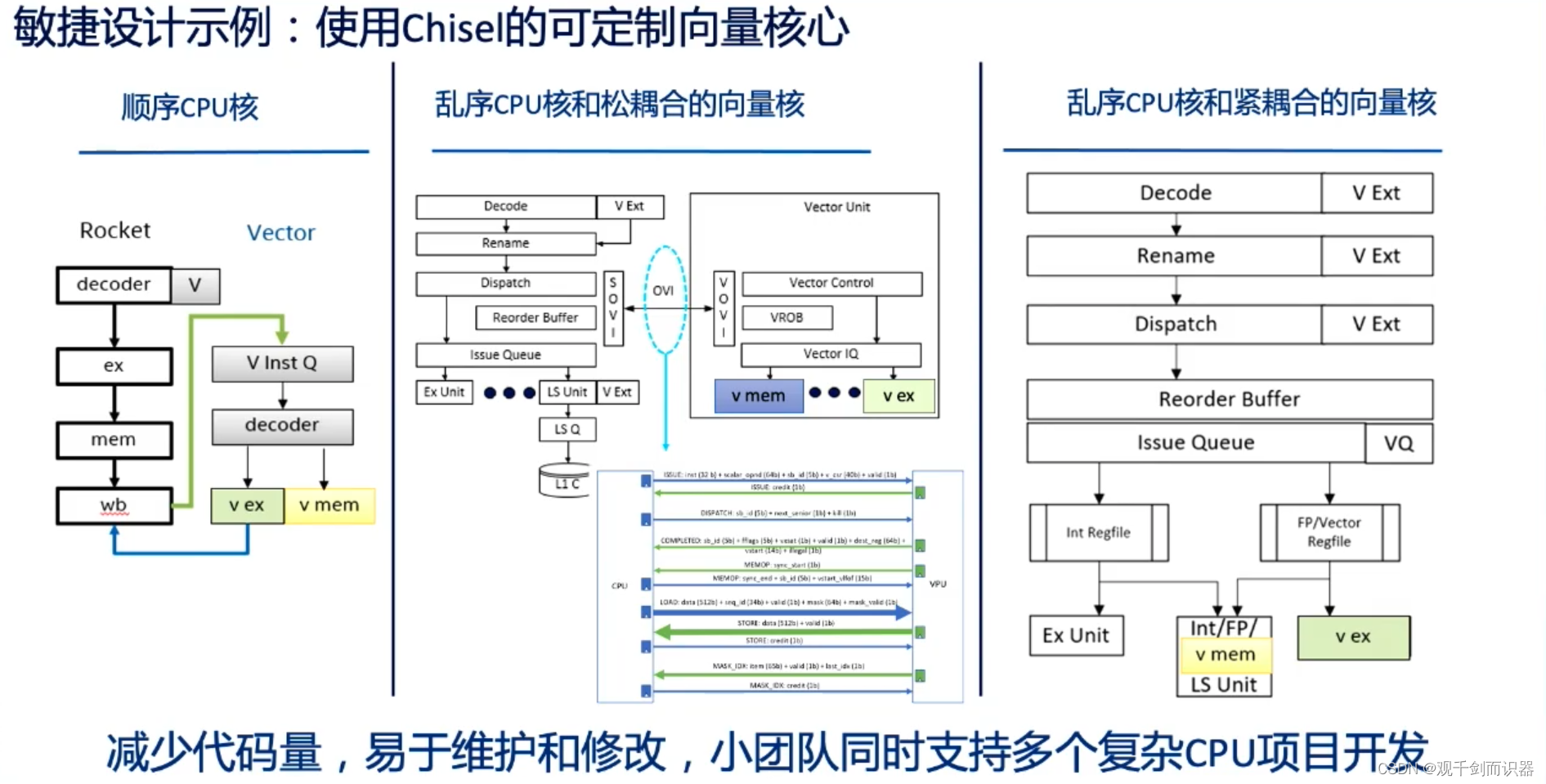

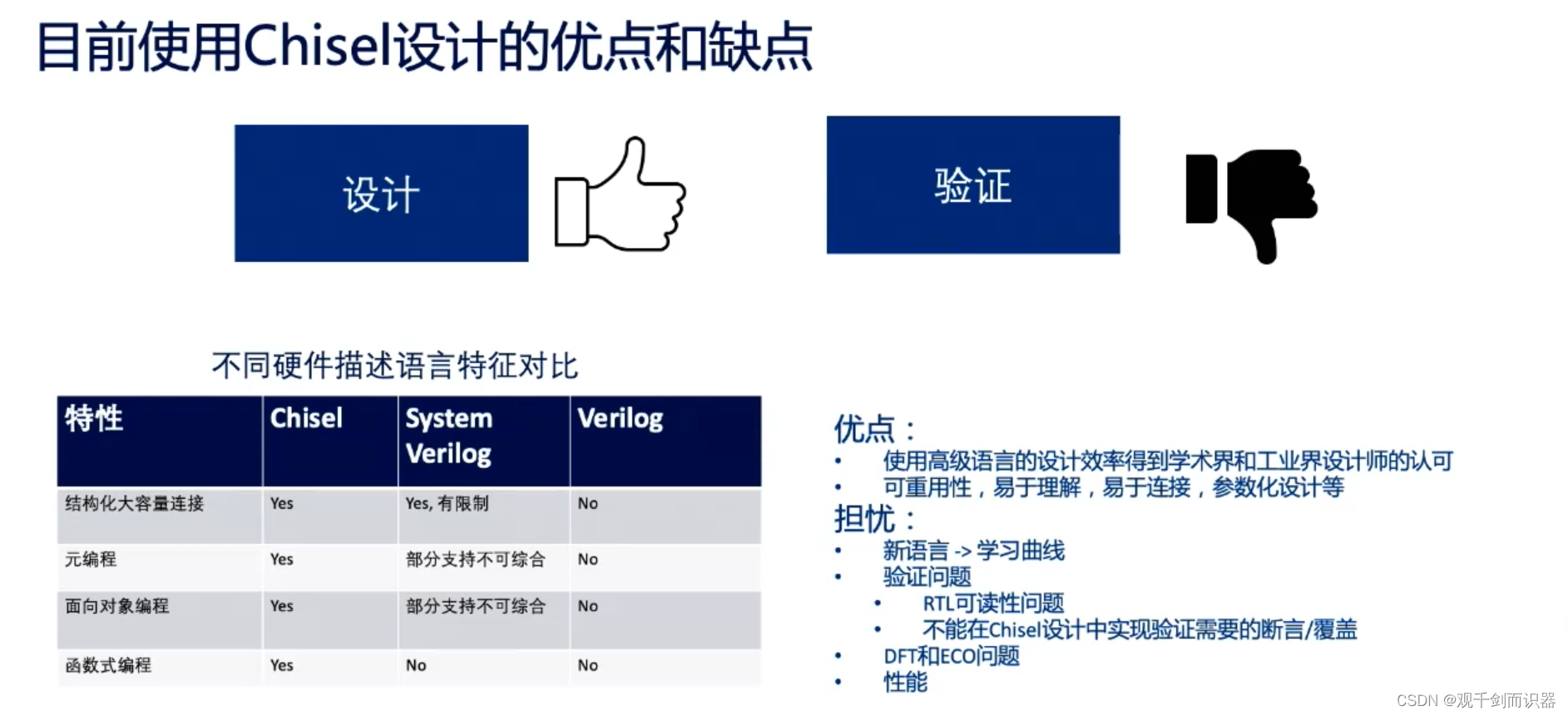

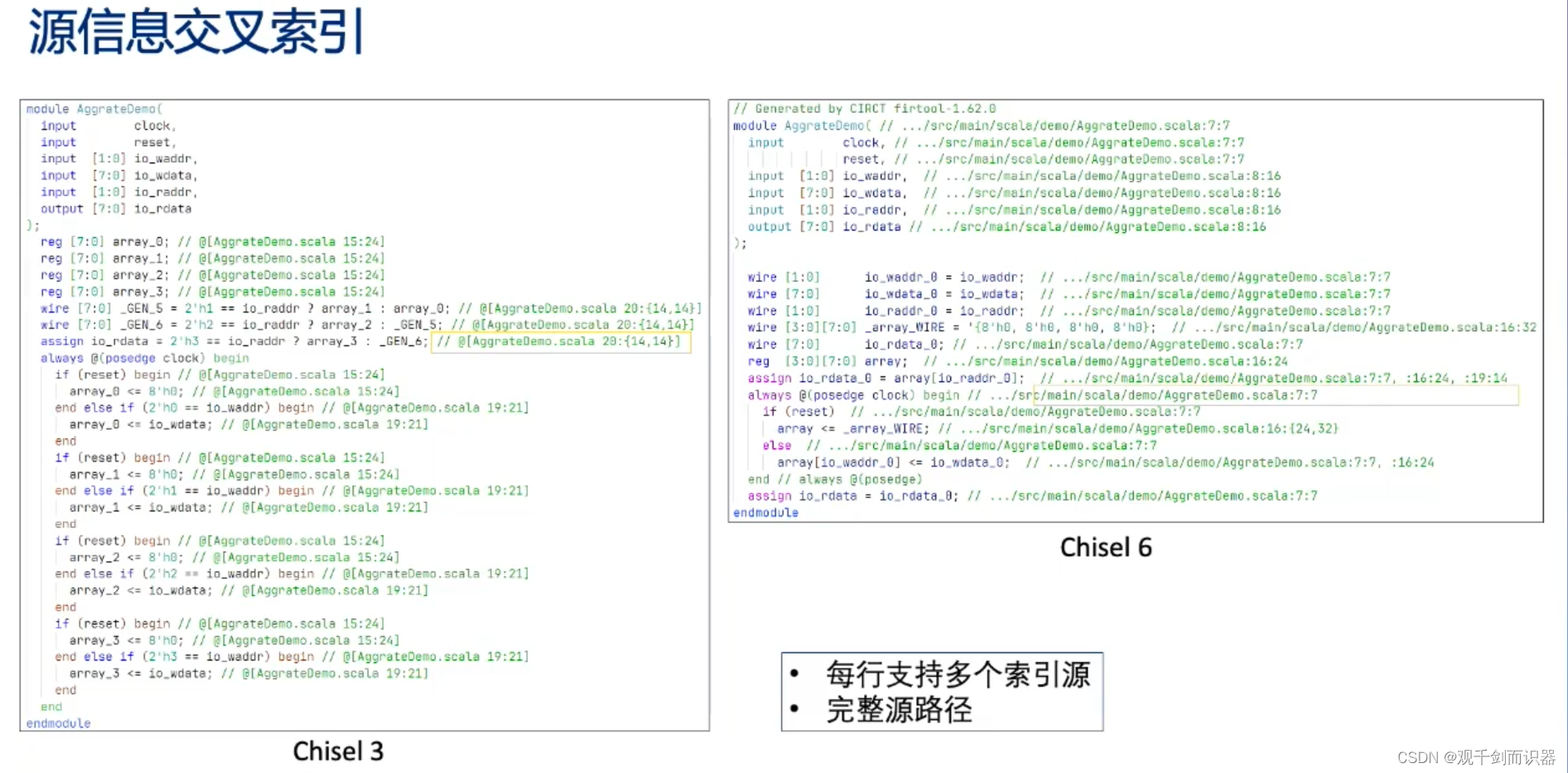

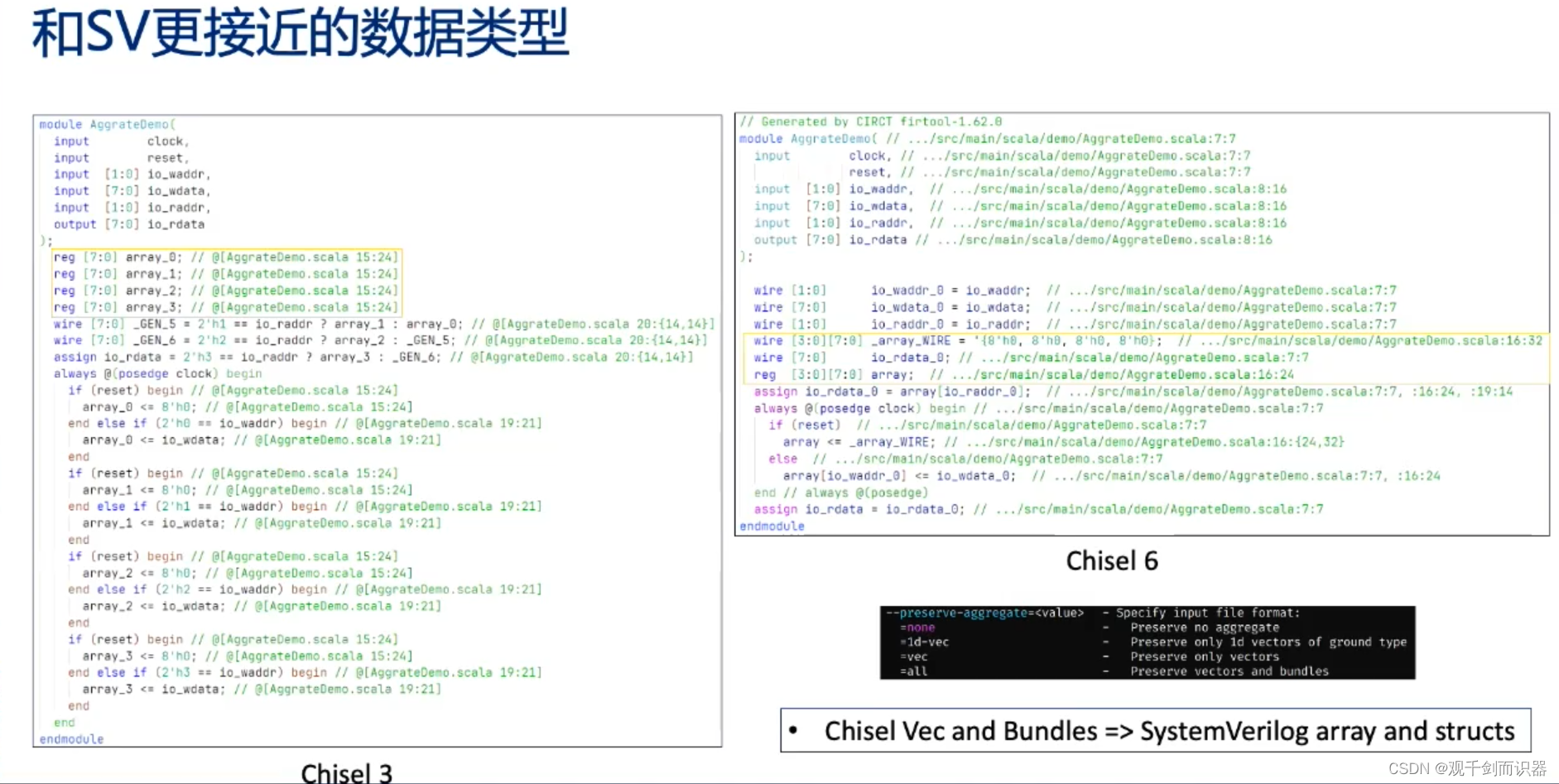

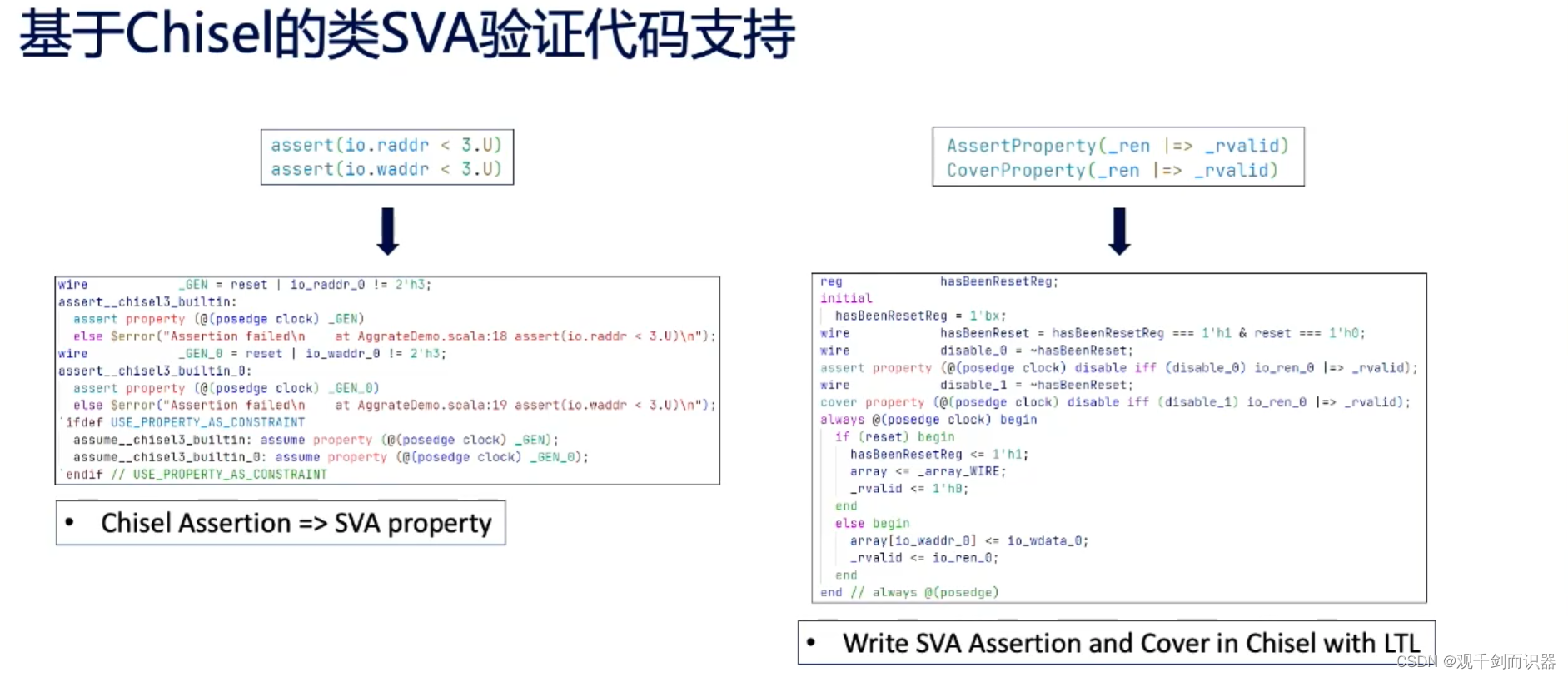

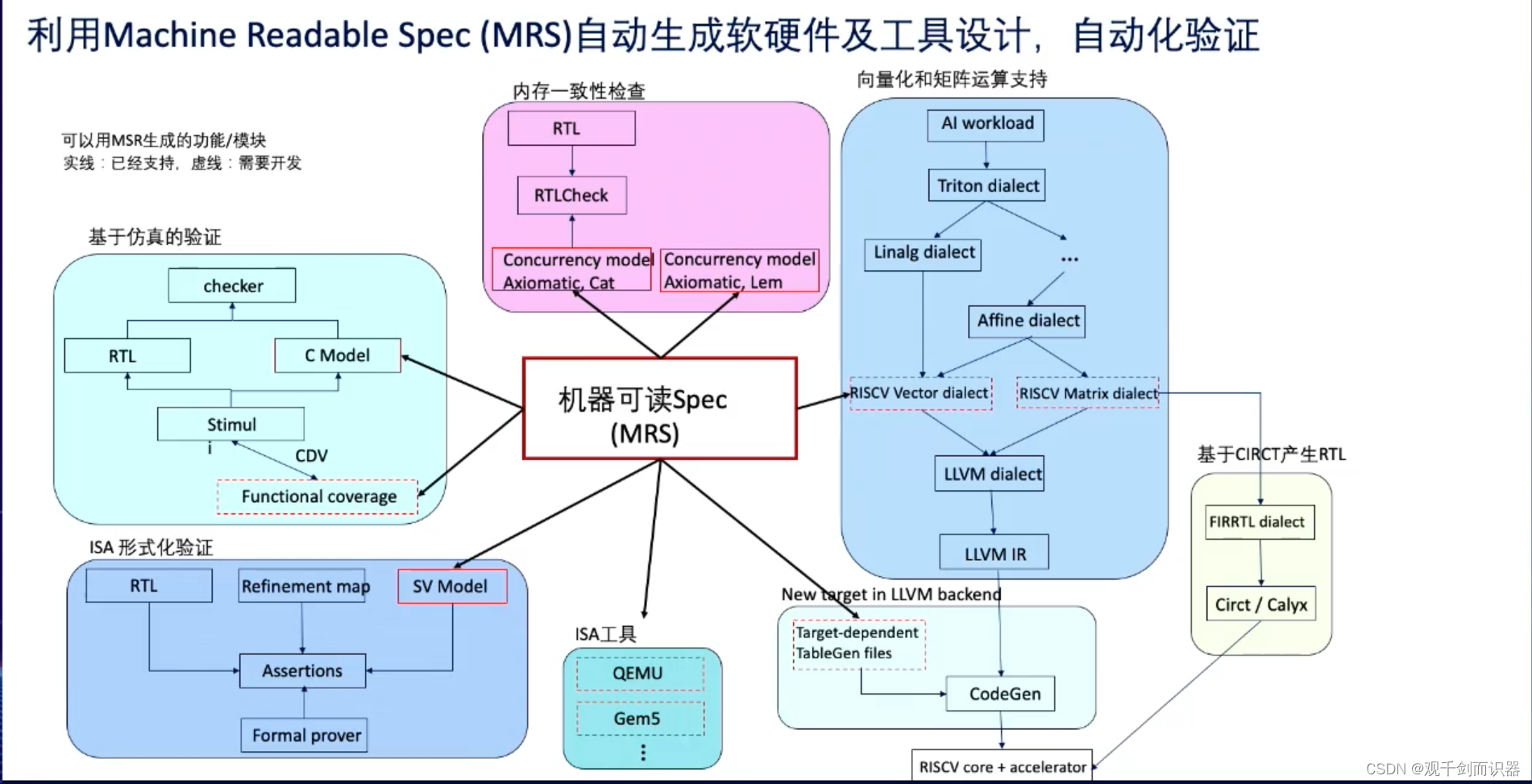

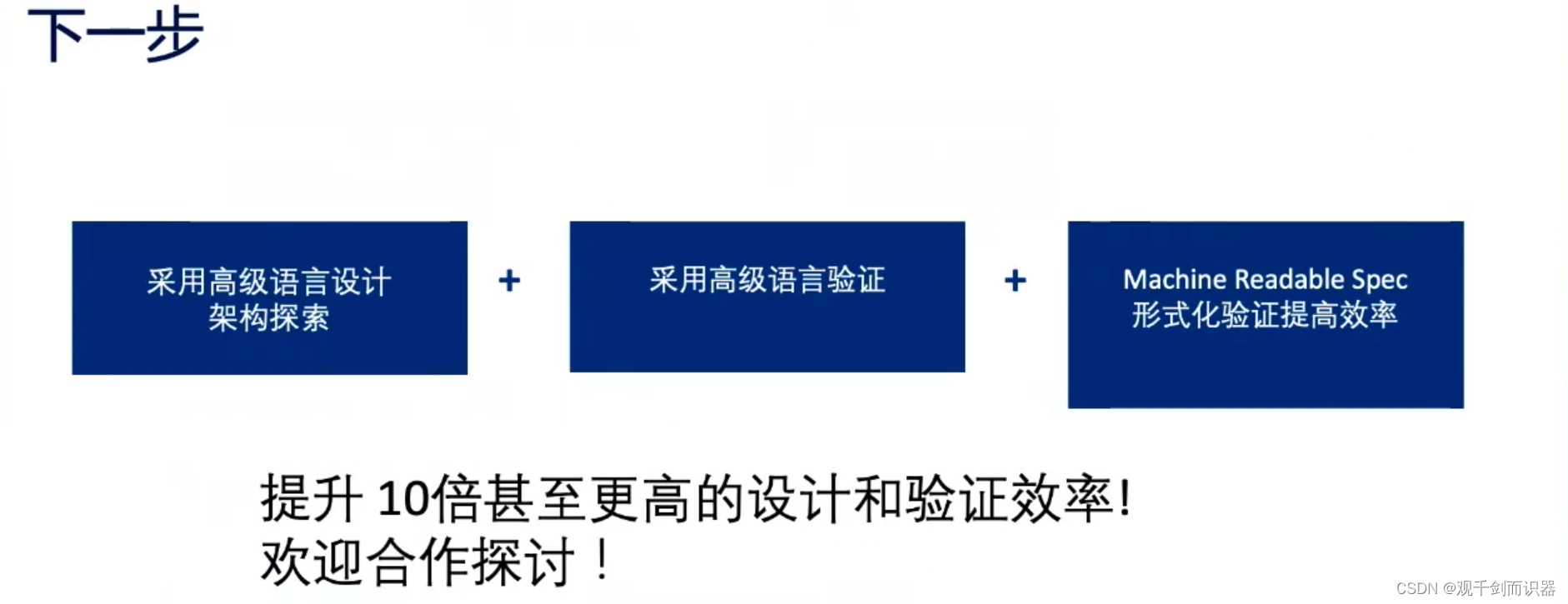

RISC-V敏捷设计与验证,张旭,英特尔中国研究院

b站视频传送门:张旭 RISC-V敏捷开发实验室总监(RADL)英特尔中国研究院首席工程师

内容来自RADL团队任永青,高一川,徐刚,李孟明,程宏

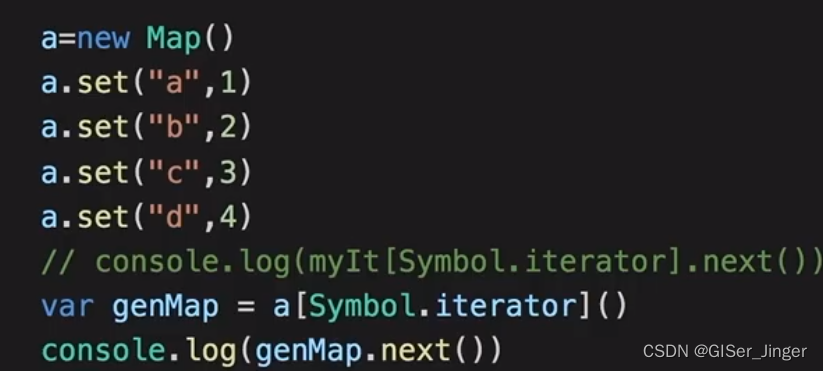

- 参数化

专题二:RISC-V软件生态

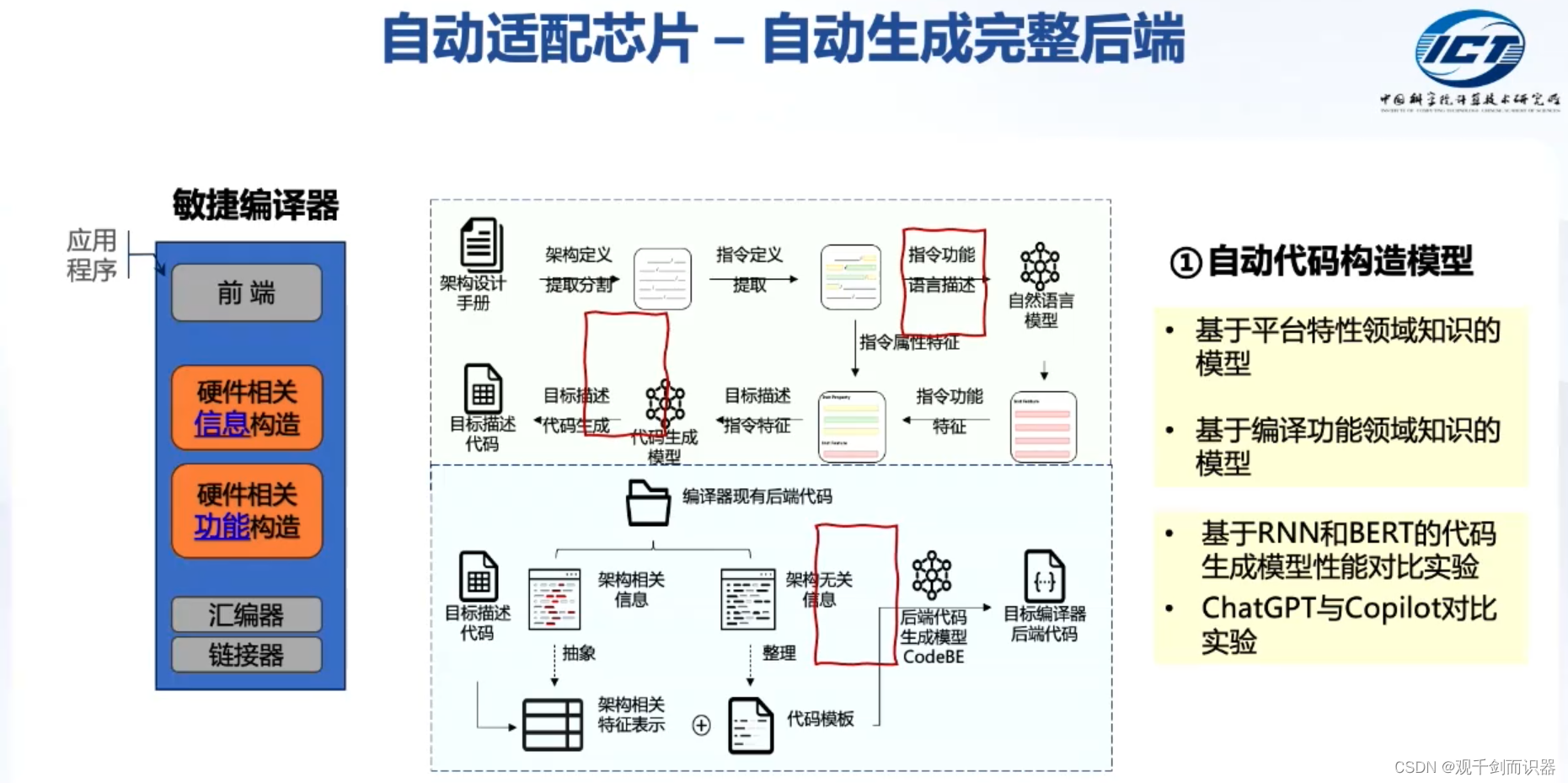

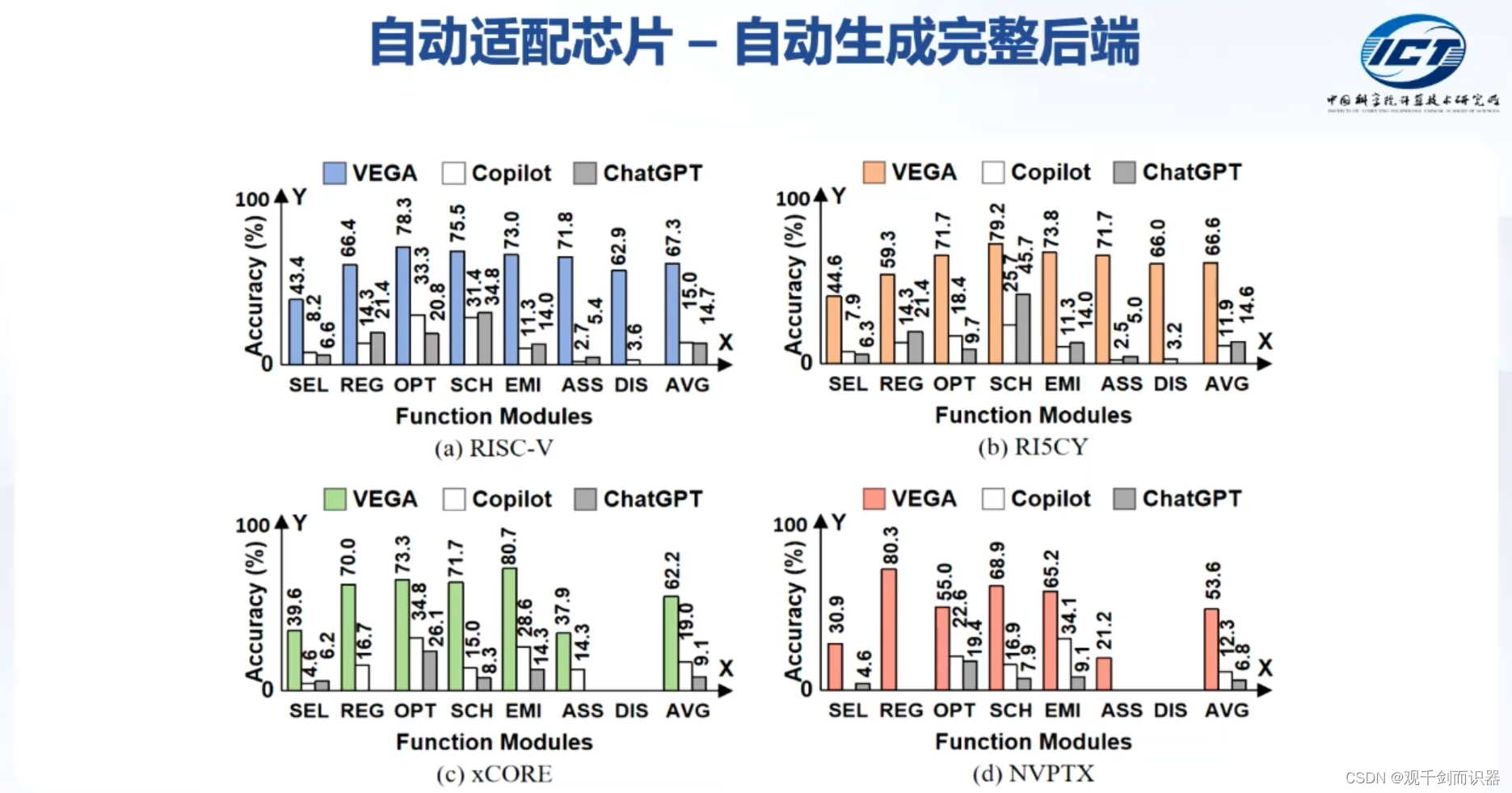

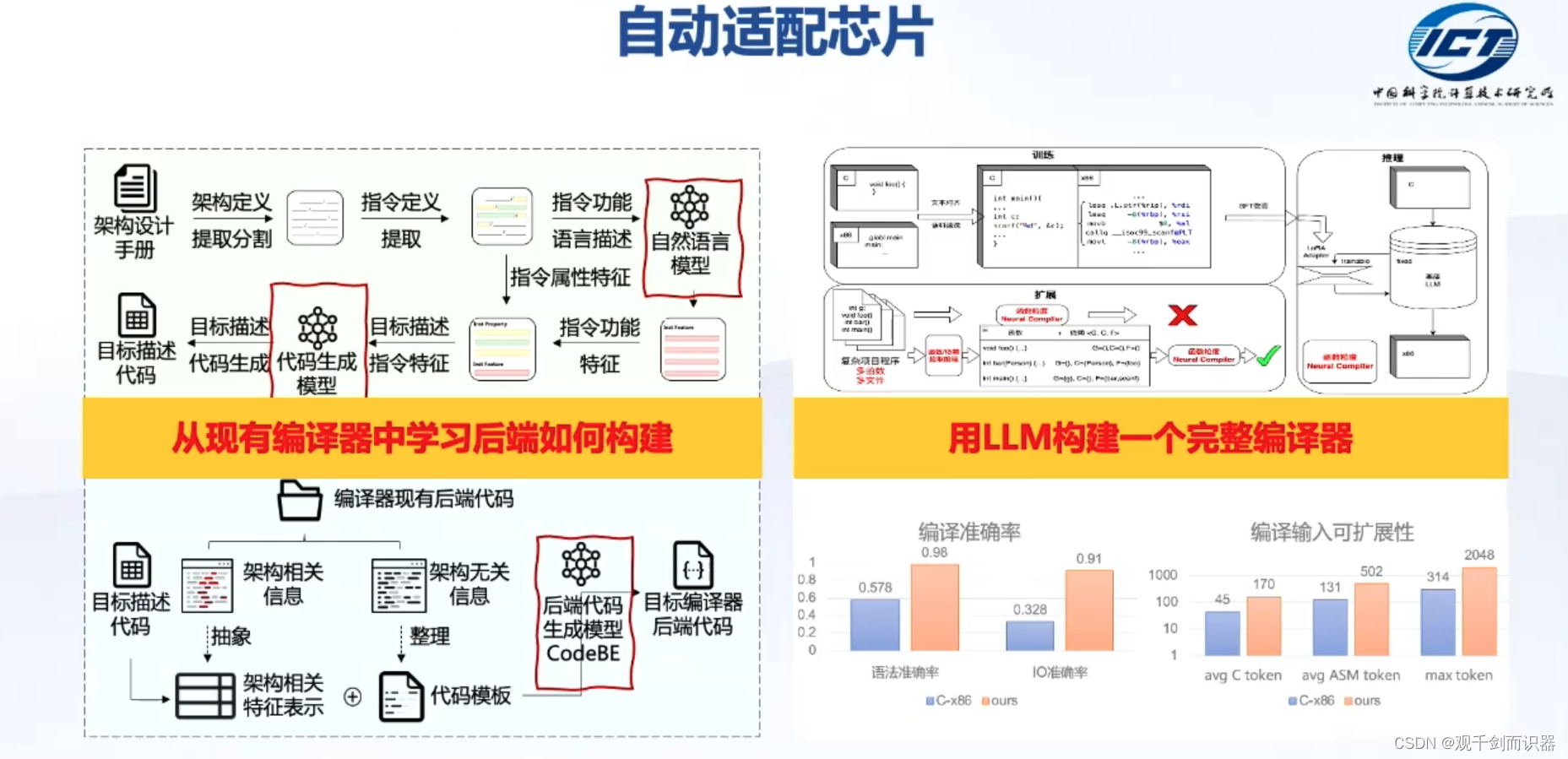

编译在新型应用发展下的潜力,崔慧敏,中国科学院计算技术研究所

b站视频传送门:编译在新型应用发展下的潜力,崔慧敏,研究员(中国科学院计算技术研究所)

- TD芯片定义:(GPT4o生成,请注意甄别)

在芯片设计中,TD 文件通常指的是 “Timing Definition” 文件或 “Timing Data” 文件。这些文件在芯片设计和验证过程中起着关键作用。以下是一些有关 TD 文件的详细解释:

- 什么是 TD 文件?

TD 文件包含关于芯片设计中的时序约束和规范的信息。这些文件用于定义和管理设计中的时序关系,确保芯片在给定的工作频率下能够可靠运行。它们可以包括各种时序约束,如时钟周期、输入输出延迟、路径延迟等。- TD 文件的作用

- 时序约束:定义芯片中不同模块之间的时序关系,确保信号在正确的时间到达目的地。

- 时钟定义:指定时钟信号的频率、周期和相位关系。

- 延迟约束:设置输入输出延迟和路径延迟,确保数据传输在指定时间内完成。

- 静态时序分析:帮助进行静态时序分析(STA),验证设计在各种工艺、电压和温度(PVT)条件下的时序性能。

- TD 文件的内容

TD 文件的具体内容可能会因设计工具和具体设计流程而异,但通常包括以下部分:

- 时钟定义:定义时钟源、时钟树结构及其频率。

- 路径约束:定义关键路径及其最大和最小延迟要求。

- 输入输出约束:设置输入和输出信号的时序要求。

- 多周期路径:定义那些需要多个时钟周期才能完成的数据路径。

- 假设路径:标识那些不需要考虑时序约束的路径。

- 示例

以下是一个简化的 TD 文件示例,使用了常见的时序约束语法:create_clock -name clk1 -period 10 [get_ports clk1] set_input_delay -clock clk1 2 [get_ports data_in] set_output_delay -clock clk1 3 [get_ports data_out] set_max_delay 5.5 -from [get_ports data_in] -to [get_ports data_out]

create_clock定义了一个名为clk1的时钟,周期为 10 单位时间。set_input_delay设置输入端口data_in相对于时钟clk1的输入延迟为 2 单位时间。set_output_delay设置输出端口data_out相对于时钟clk1的输出延迟为 3 单位时间。set_max_delay设置从data_in到data_out的最大路径延迟为 5.5 单位时间。

- 工具支持

TD 文件通常与各种电子设计自动化(EDA)工具结合使用,这些工具包括:

- 静态时序分析工具:如 Synopsys PrimeTime、Cadence Tempus。

- 综合工具:如 Synopsys Design Compiler、Cadence Genus。

- 布局布线工具:如 Cadence Innovus、Synopsys IC Compiler。

总结

TD 文件在芯片设计中起着至关重要的作用,通过定义和管理时序约束,确保设计在预期条件下的可靠运行。理解和正确使用 TD 文件是实现高性能和高可靠性芯片设计的关键步骤。

专题三:RISC-V与先进计算

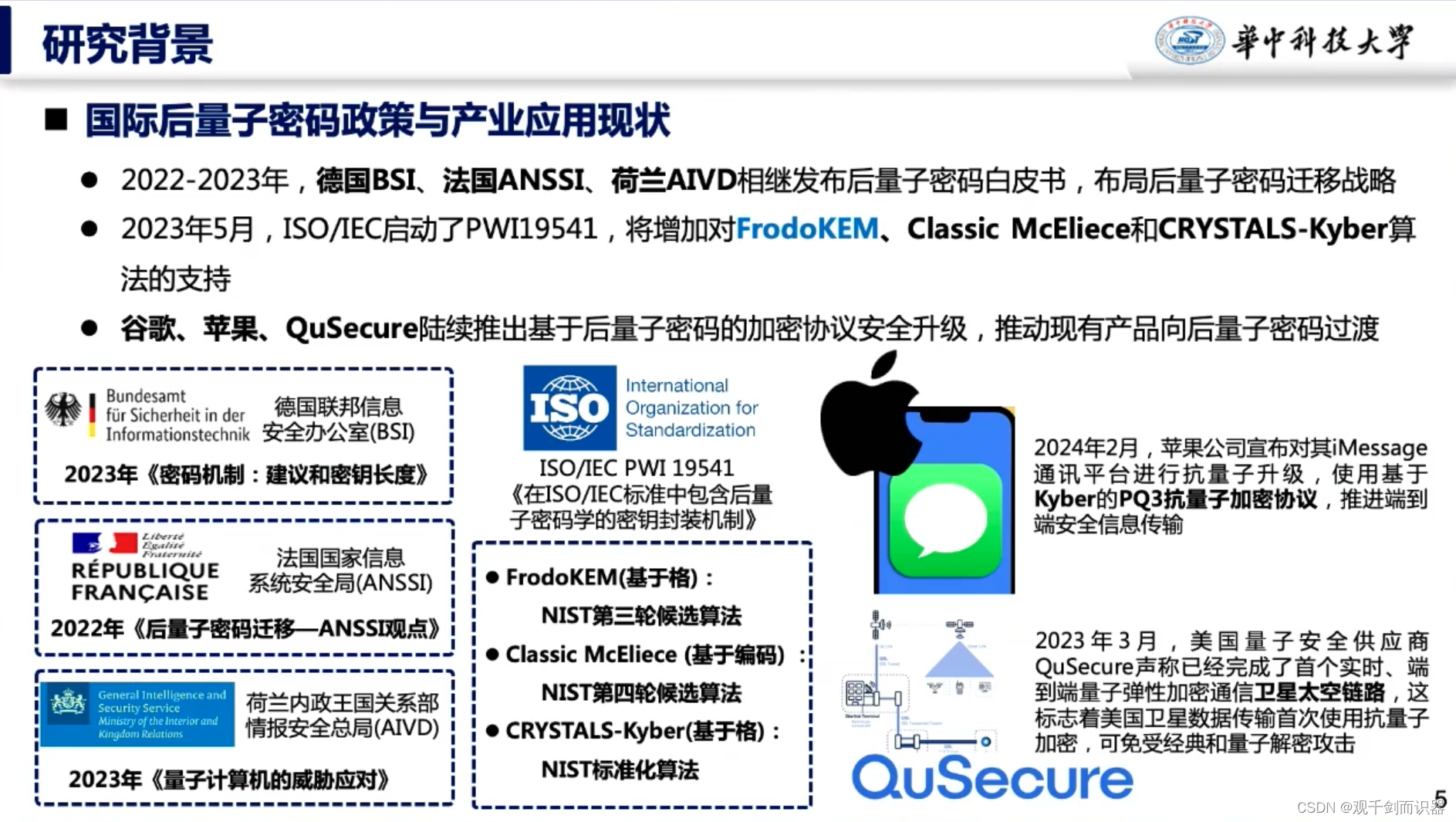

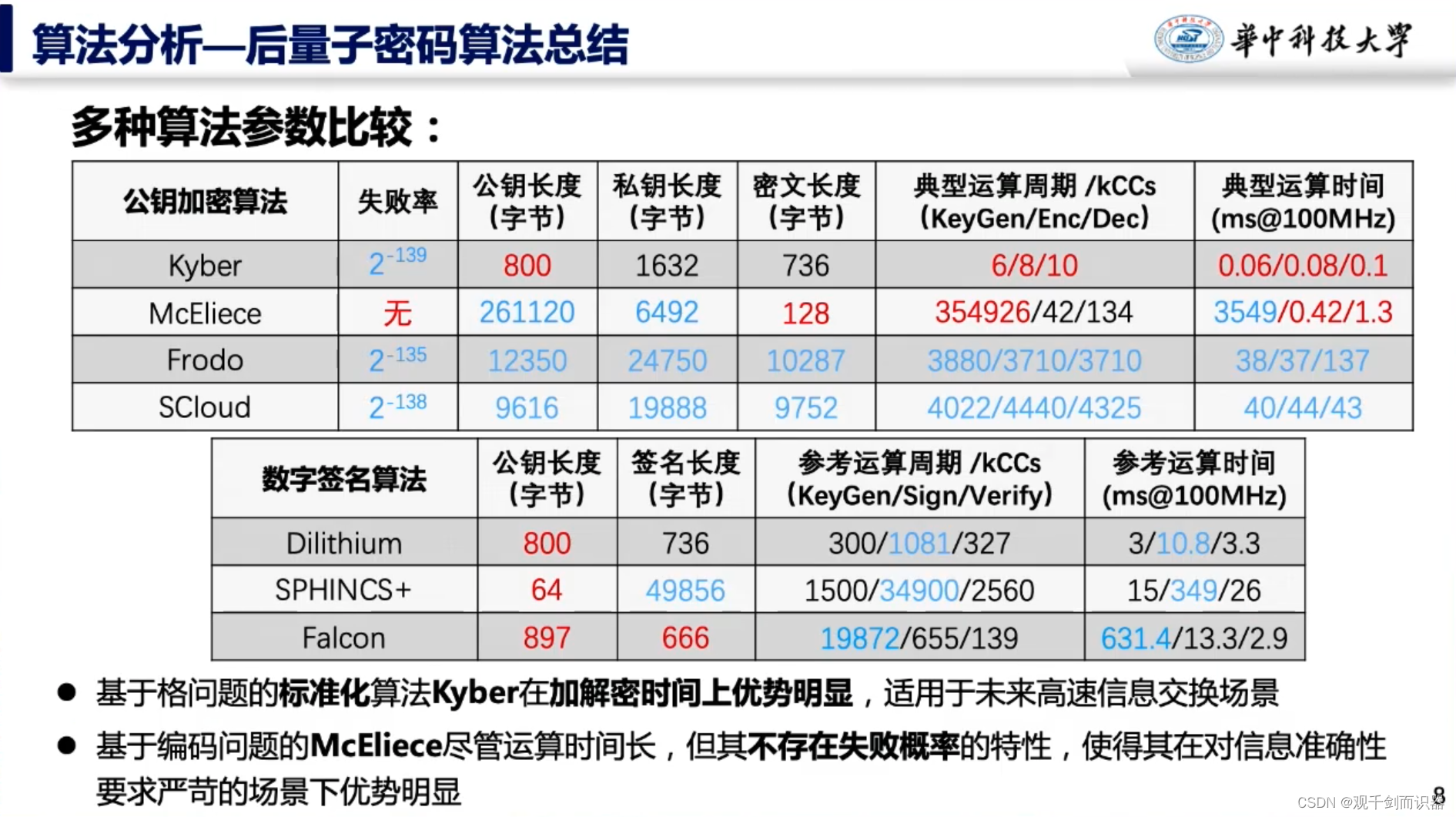

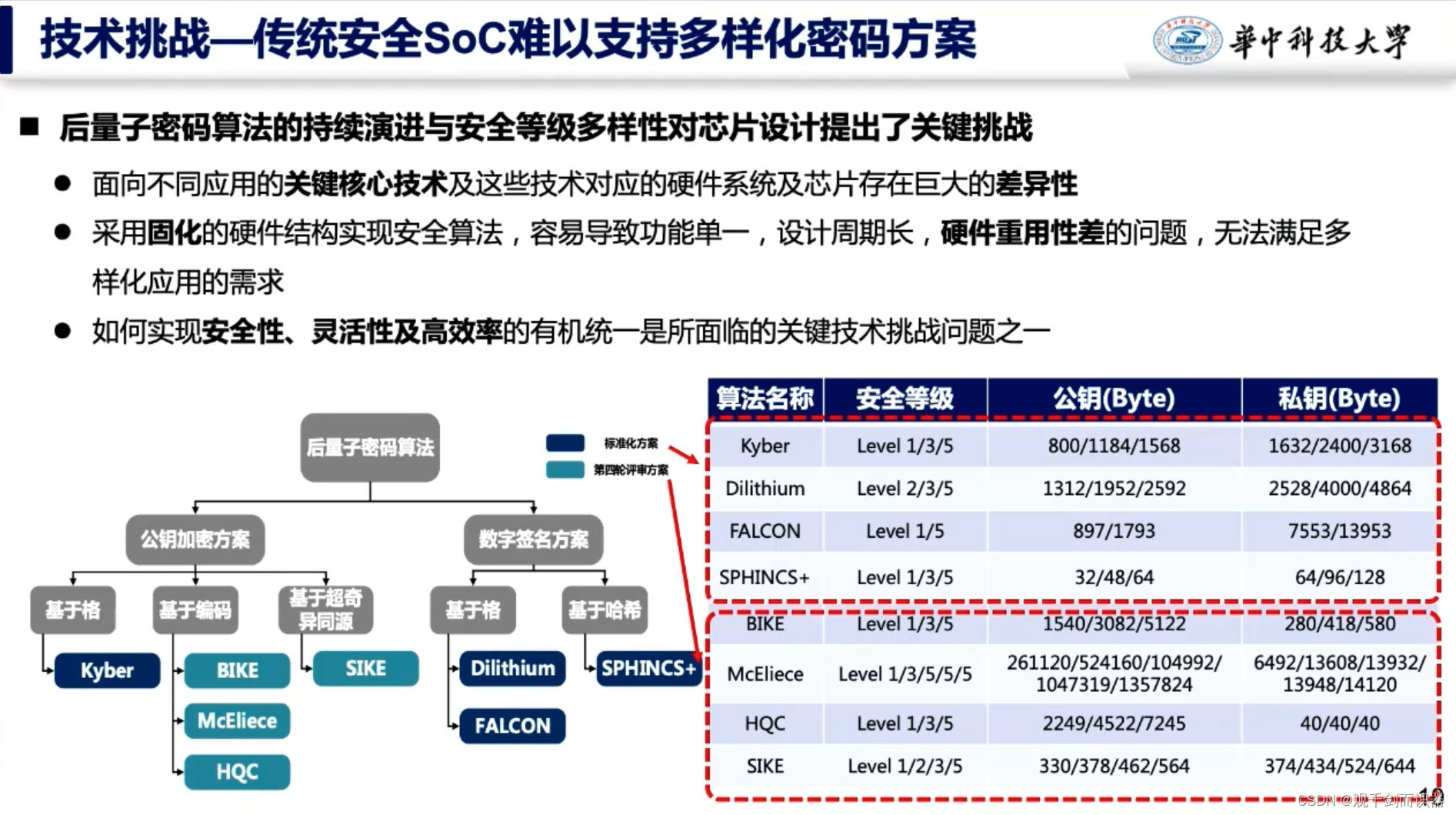

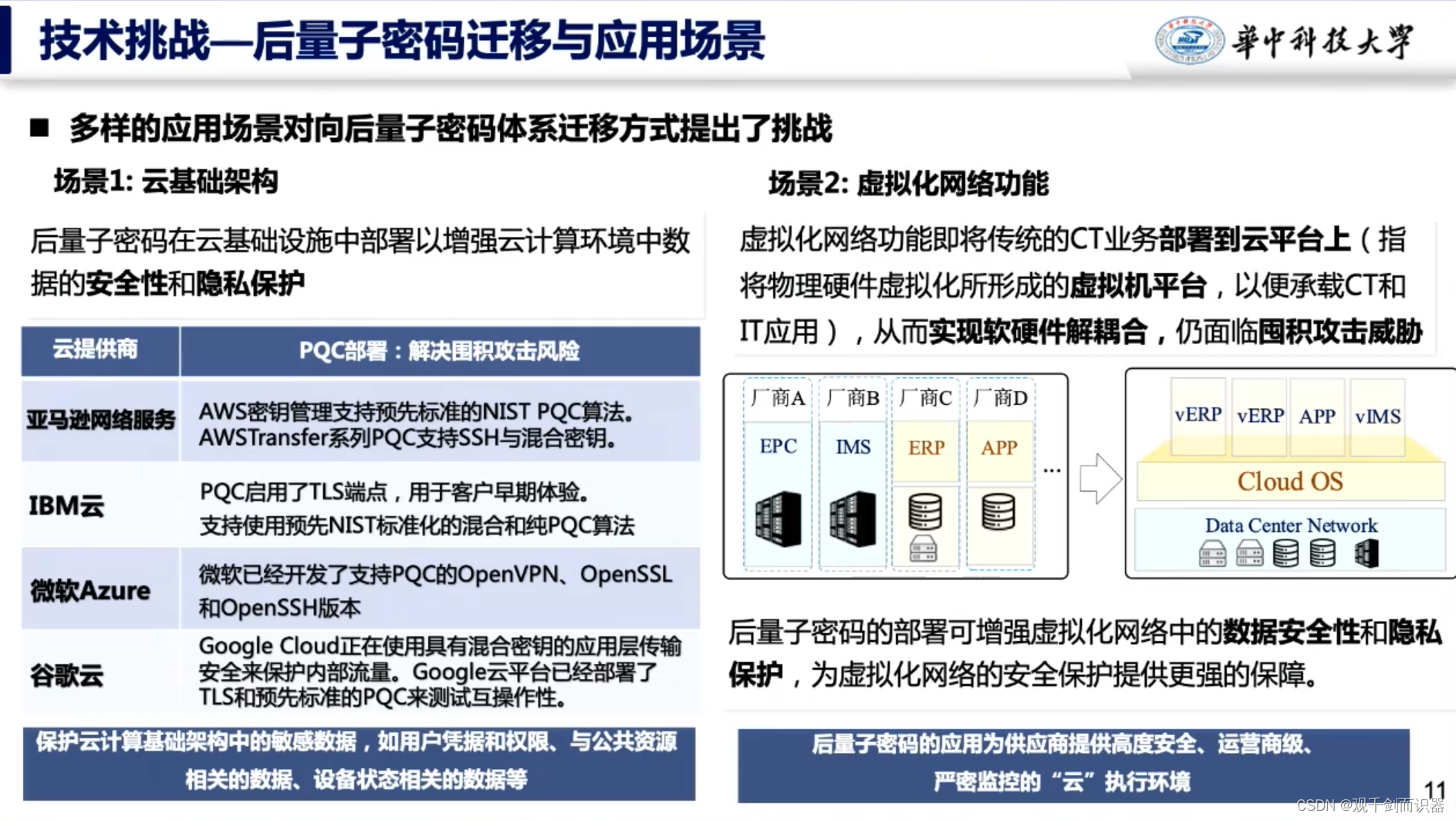

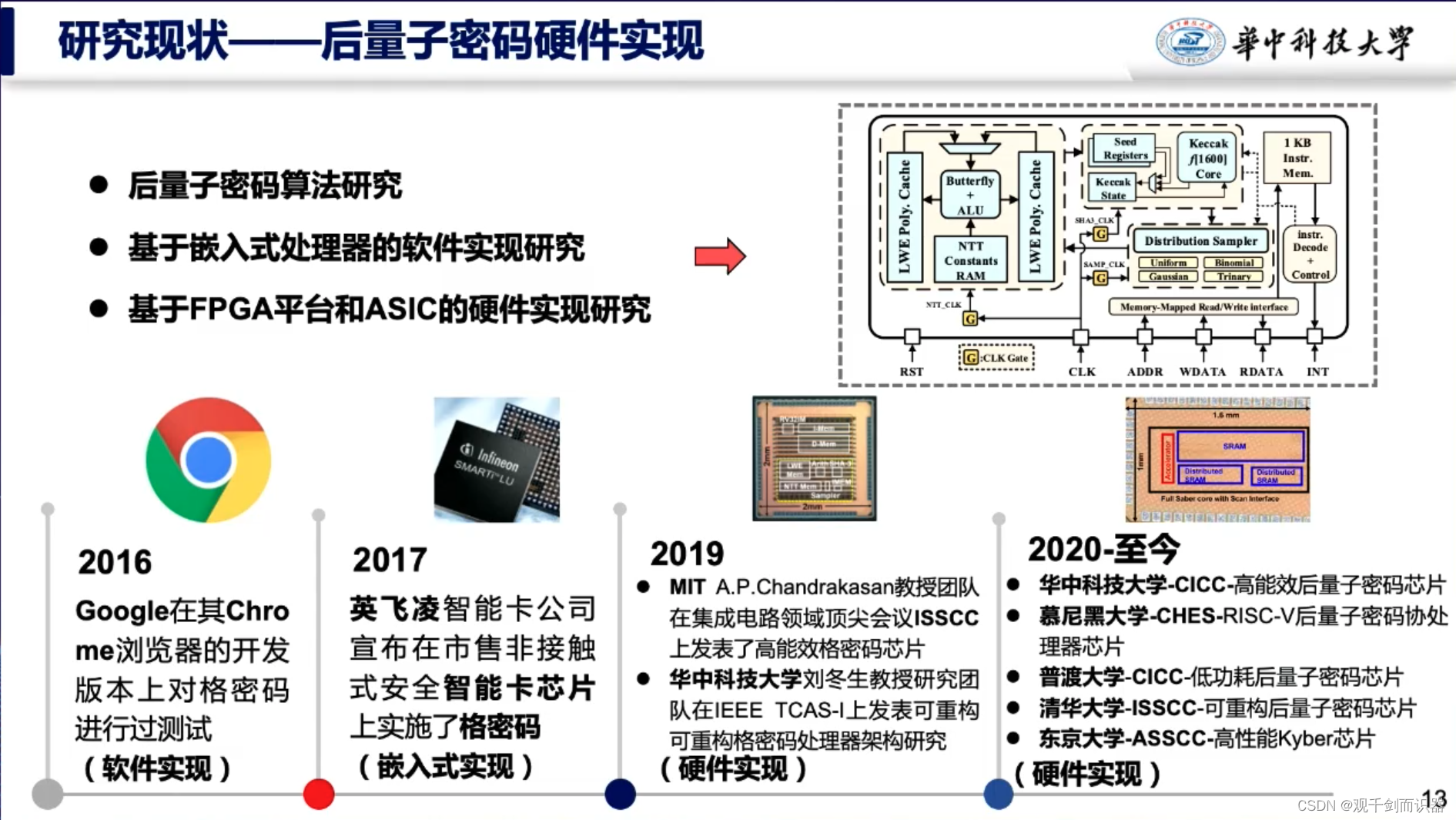

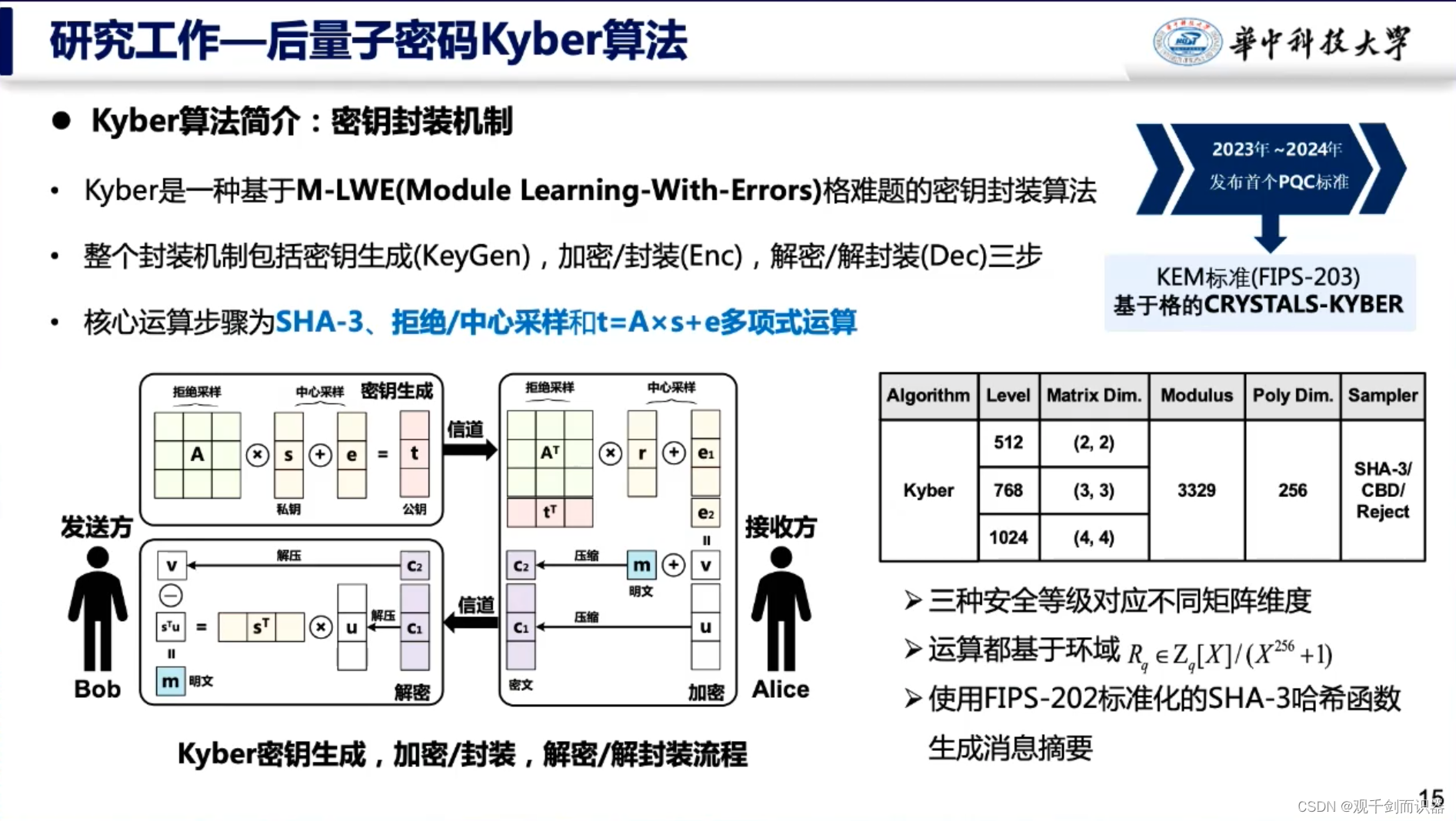

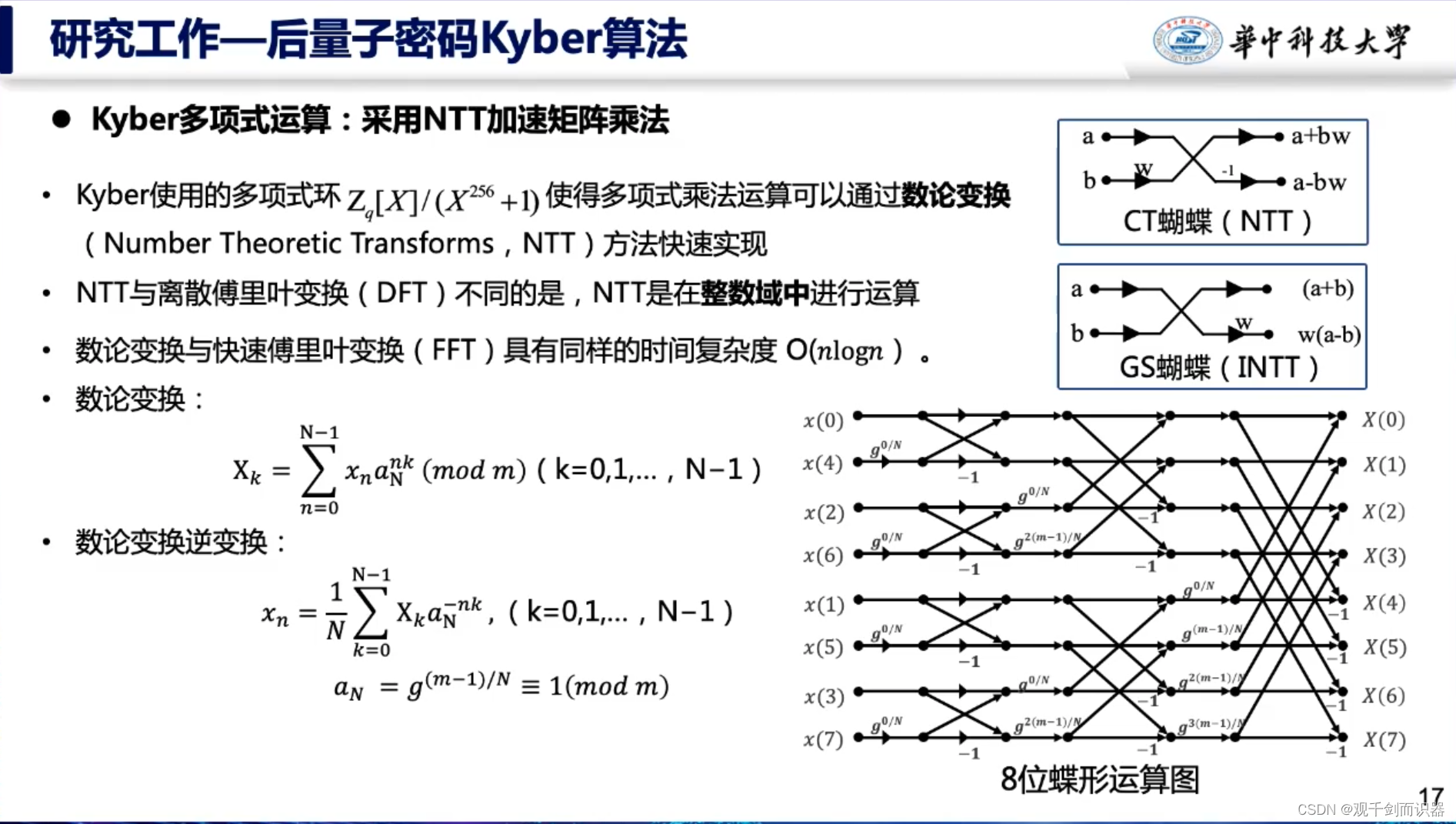

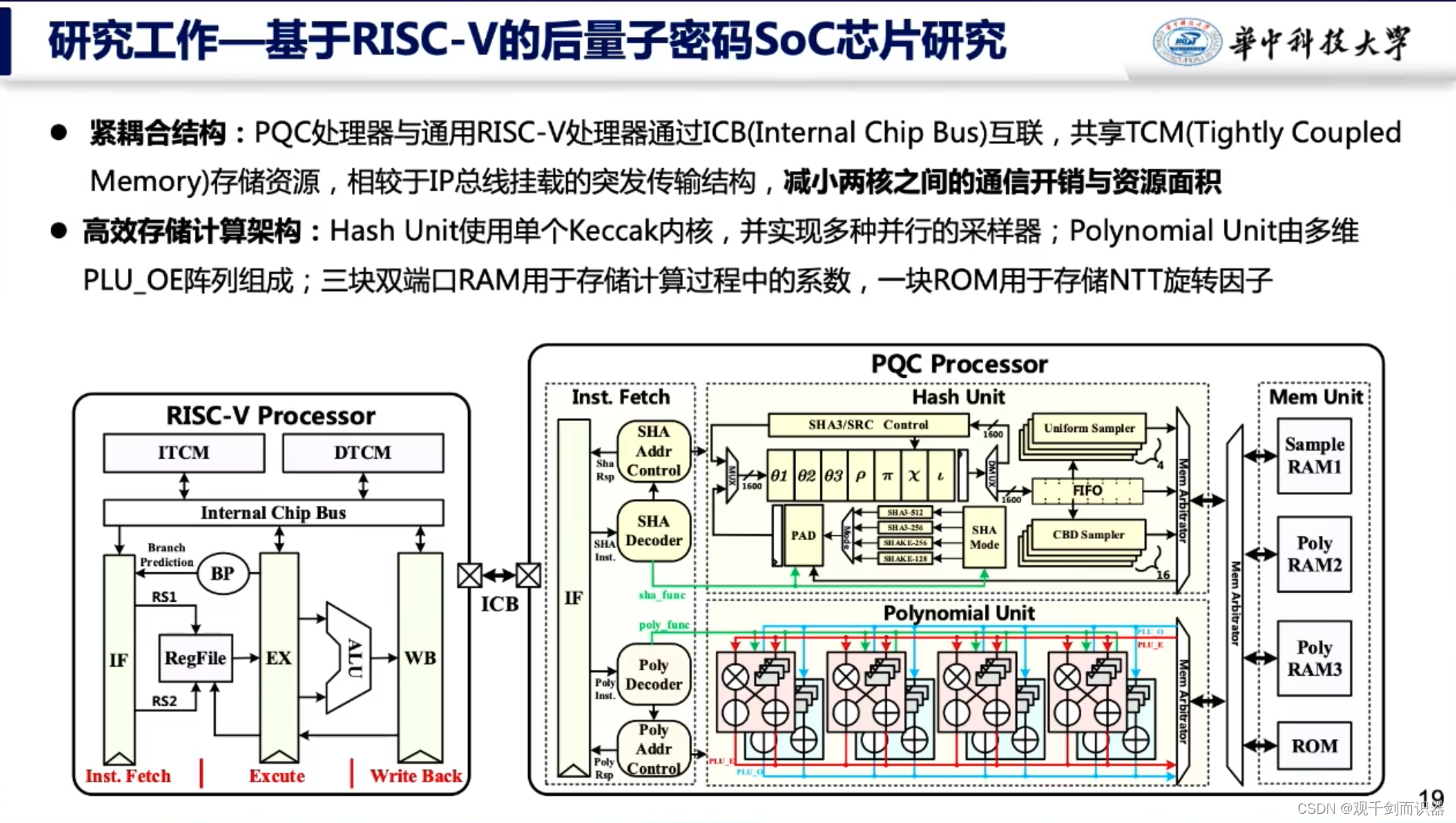

基于RISC-V的后量子密码芯片设计,刘冬生,华中科技大学

b站视频传送门:基于RISC-V的后量子密码芯片设计,刘冬生,华中科技大学 国家集成电路学院、国家集成电力产教融合创新平台

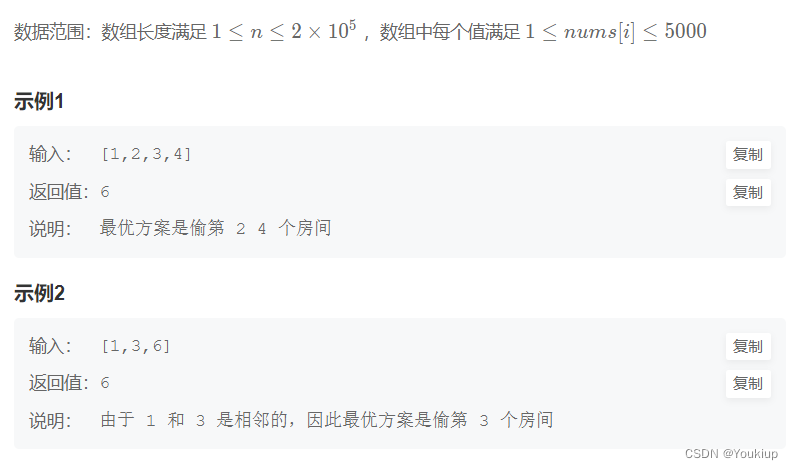

- 基于格的方案更具优势

- 三种安全等级对应不同维度

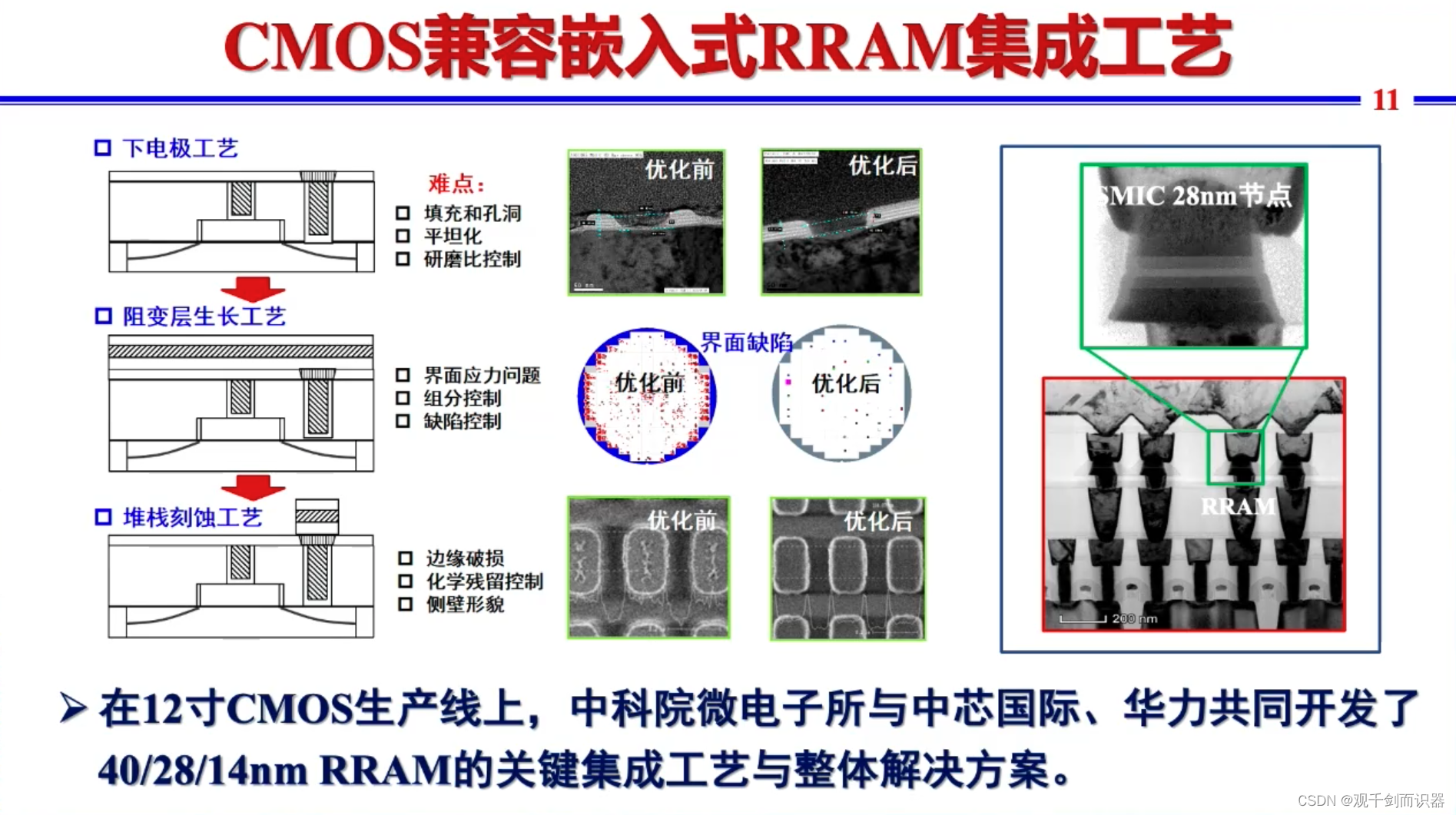

存算一体集成芯片,刘琦,复旦大学

b站视频传送门:存算一体集成芯片,刘琦,复旦大学芯片与系统前沿技术研究院 集成芯片与系统全国重点实验室

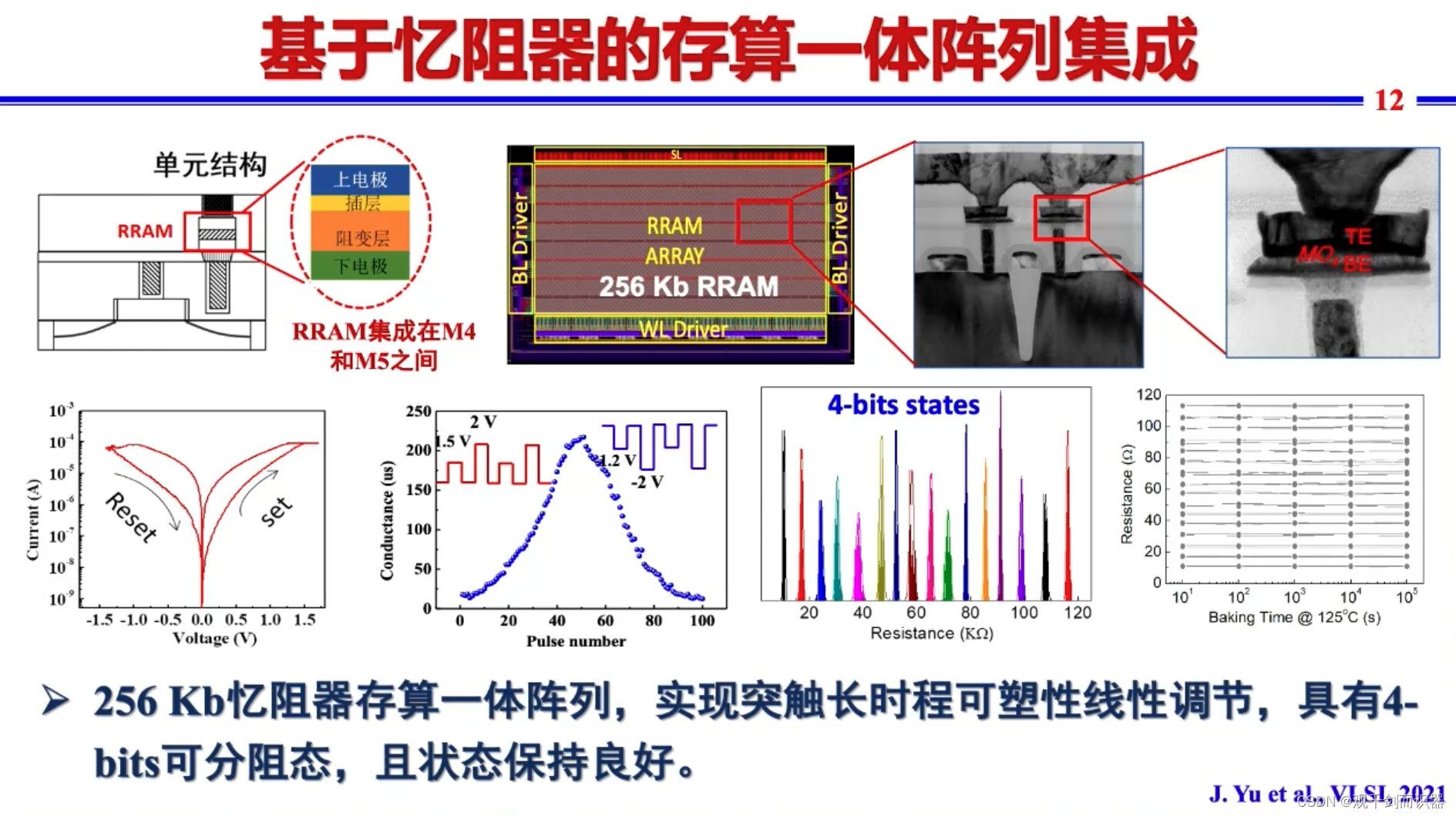

- 新原理存储器:电荷极化型——铁电存储器、自旋磁矩——自旋磁存储器、晶格结构变化的相变存储器、导电熔丝机制的阻变存储器

- 三明治结构(金属、介质、金属)

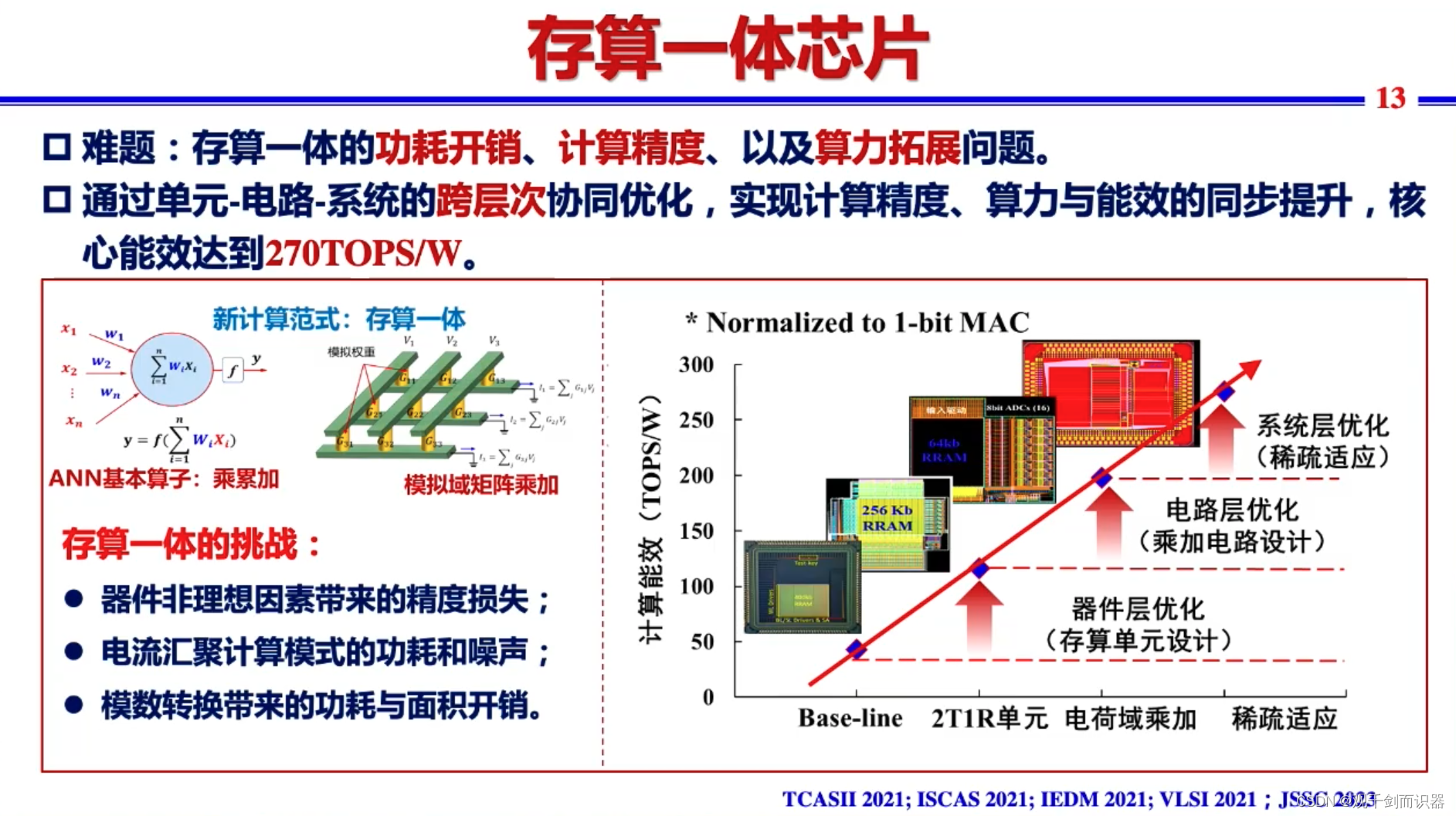

- 三种方式,终极目标是存内计算,主要为了解决神经网络-矩阵乘加运算

- 矩阵乘加是神经网络基本算子。模拟存算一体,利用:欧姆定律实现乘法(电压x电导=电流)+ 基尔霍夫定律实现加法(计算电流累加)→ 矩阵乘加,高能效、精度偏低。数字存算一体,定制化乘法器+数字加法器→高精度、高能效

- 阻变存储器(RRAM)性能更具优势

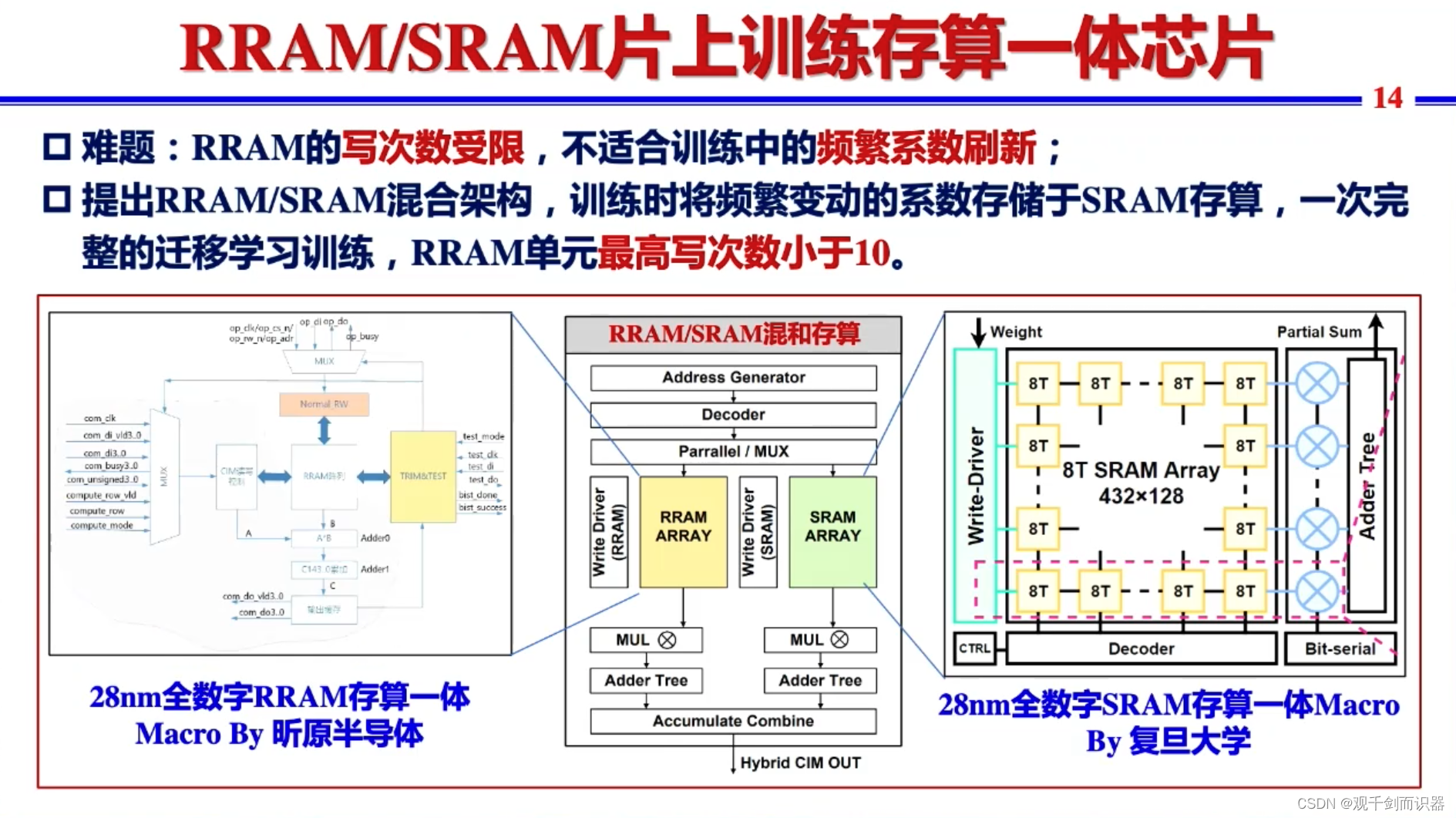

- RRAM耐久性不够,不适合系数频繁刷新。SRAM更适合频繁擦写,两者结合,实现更好的能效

- 优化矩阵乘、线性方程组求解通用算子

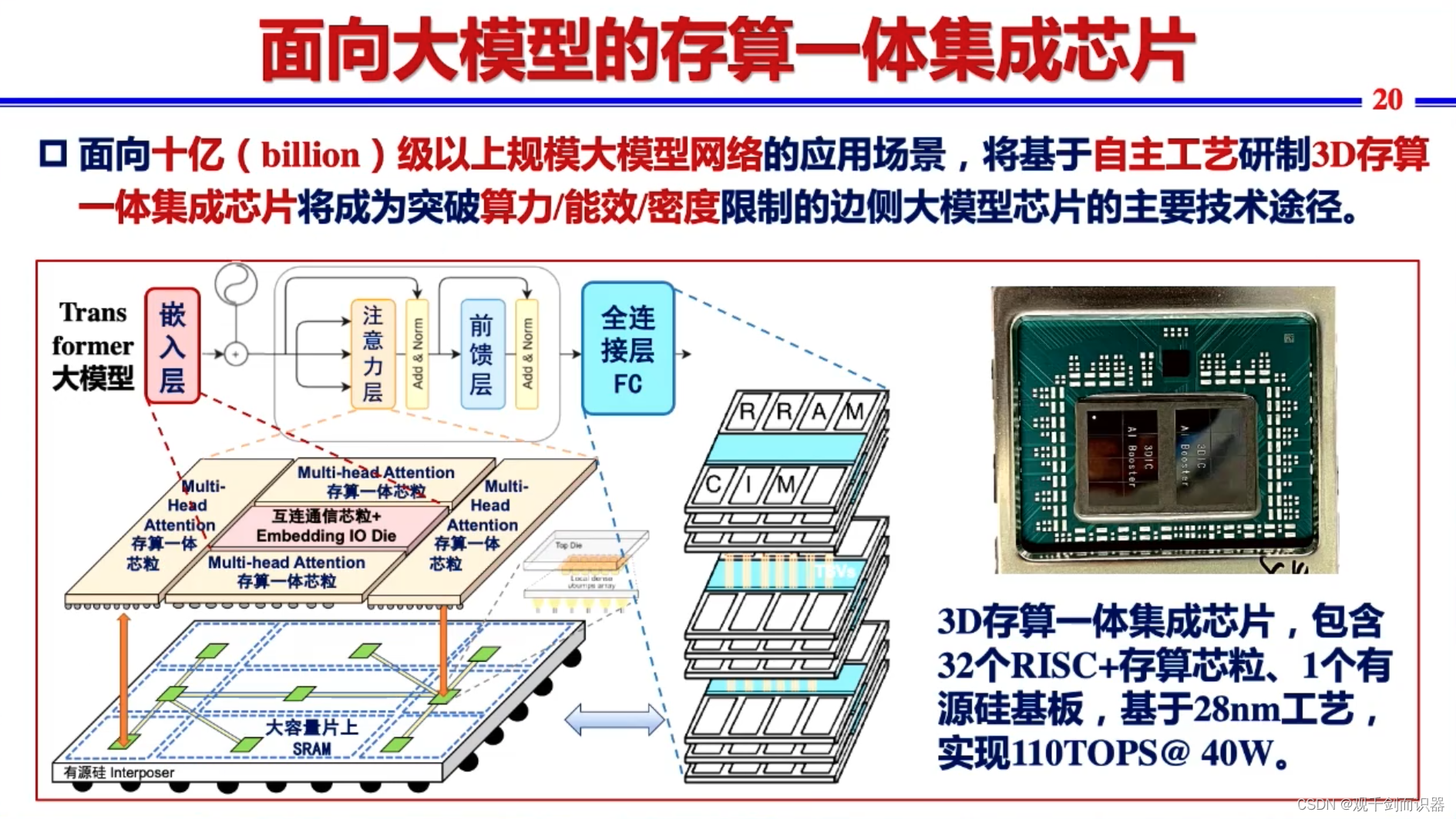

- Chiplet模式,

- 集成芯片结构,有希望用14nm工艺将性能接近于5nm芯片性能

- AI芯片的发展离不开:器件、架构、集成技术的创新

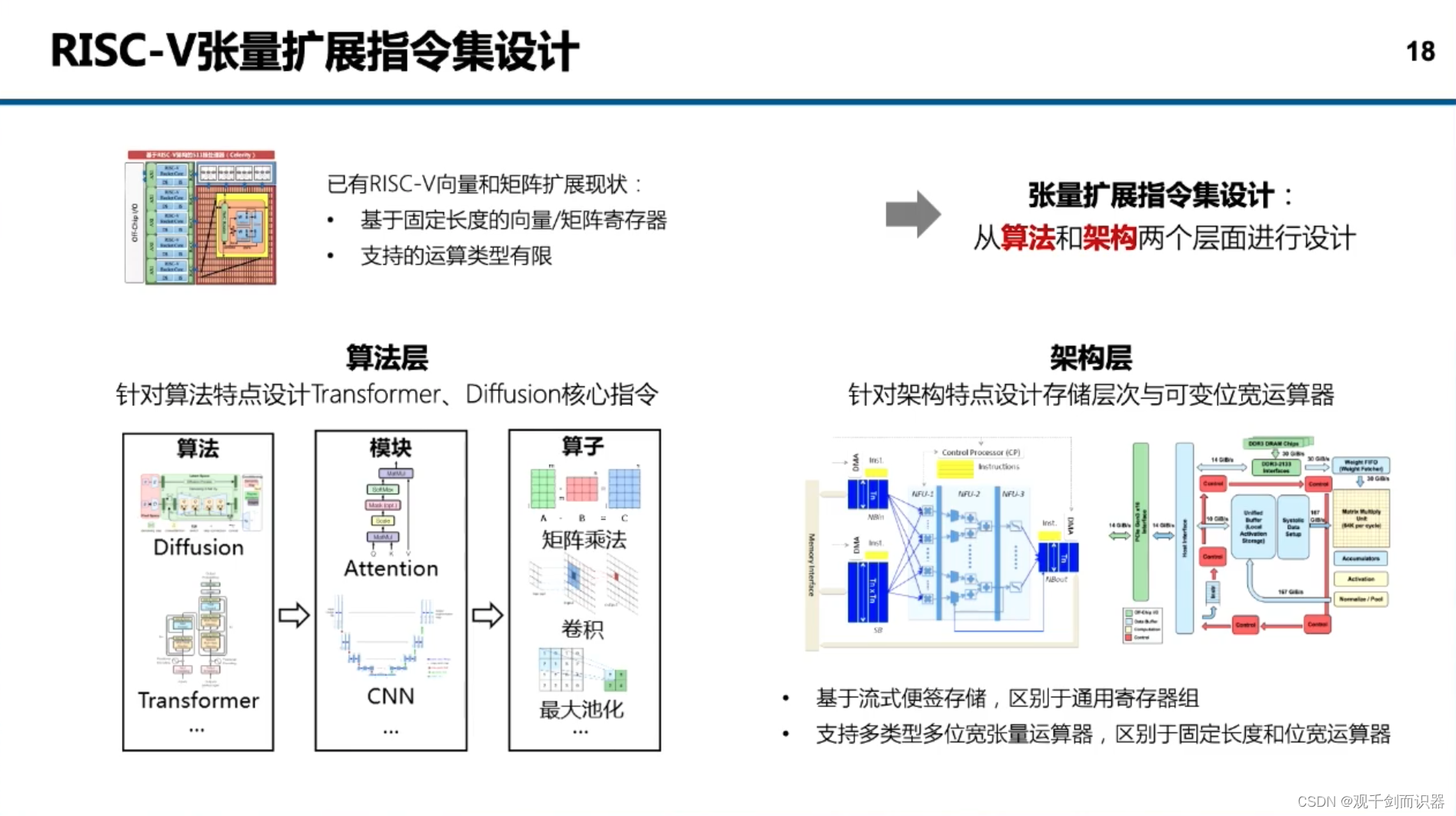

面向端侧大模型计算的RISC-V矩阵扩展架构,韩军,复旦大学

b站视频传送门:面向端侧大模型计算的RISC-V矩阵扩展架构,复旦大学,集成芯片与系统全国重点实验室,韩 军

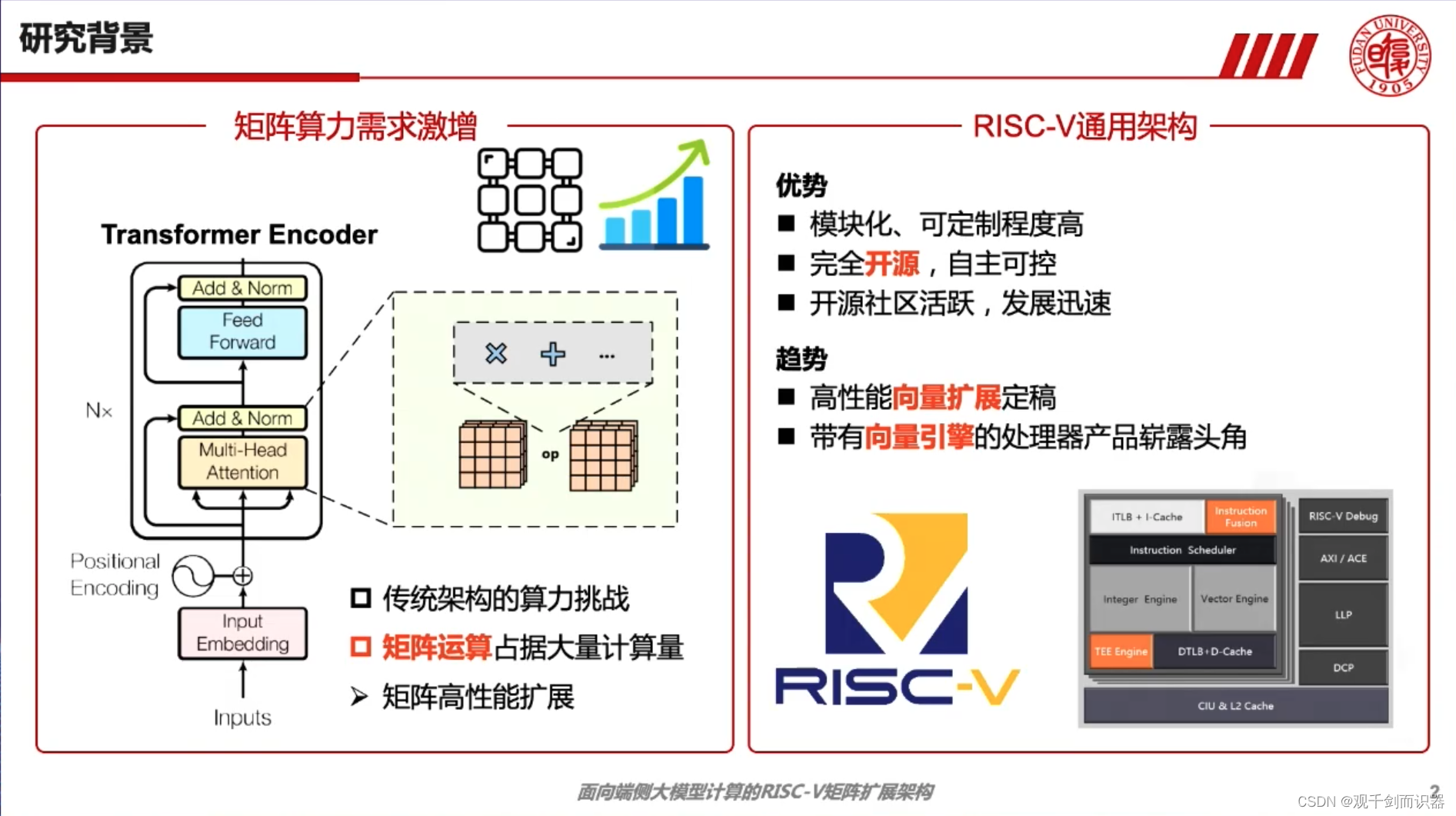

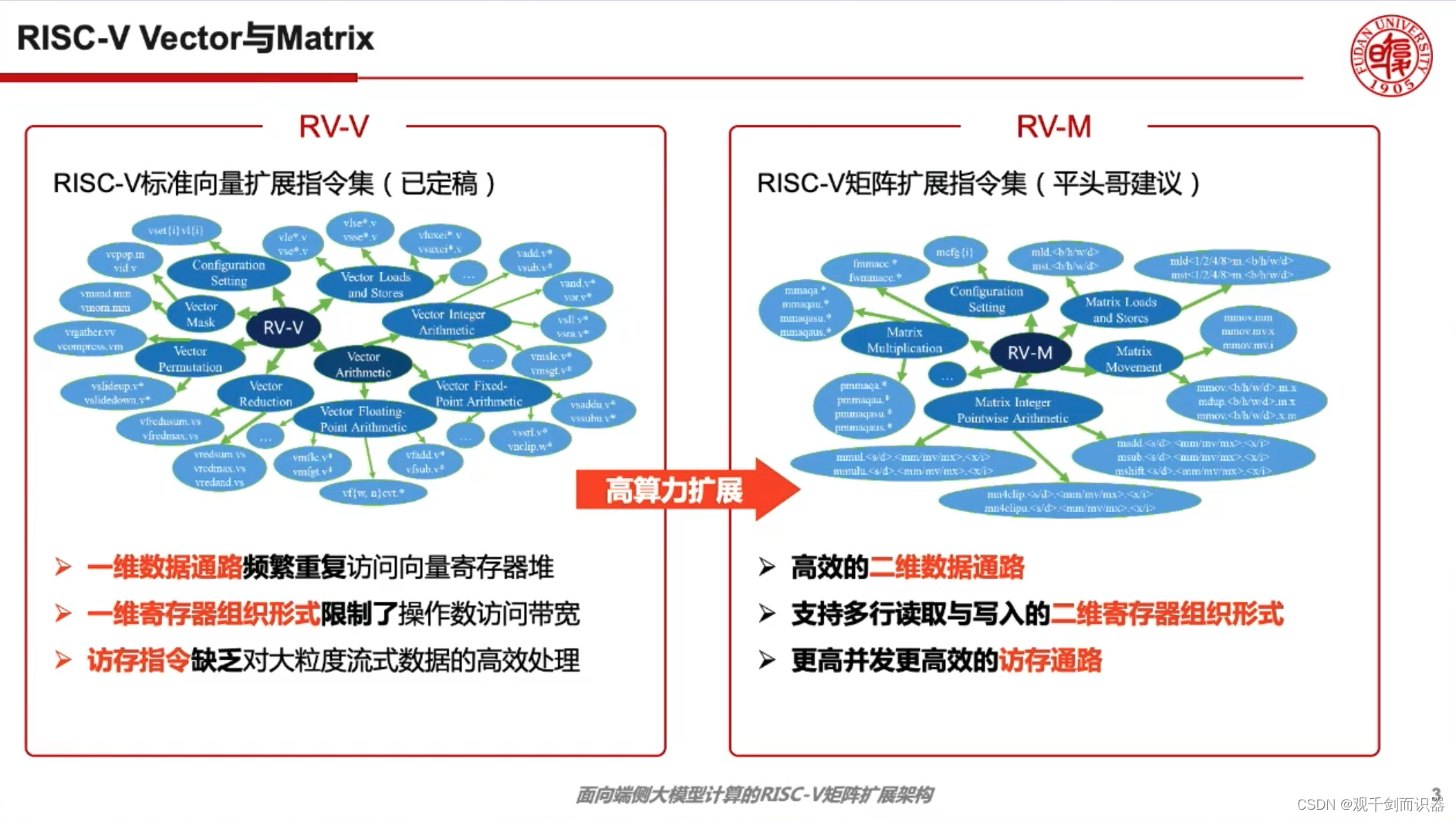

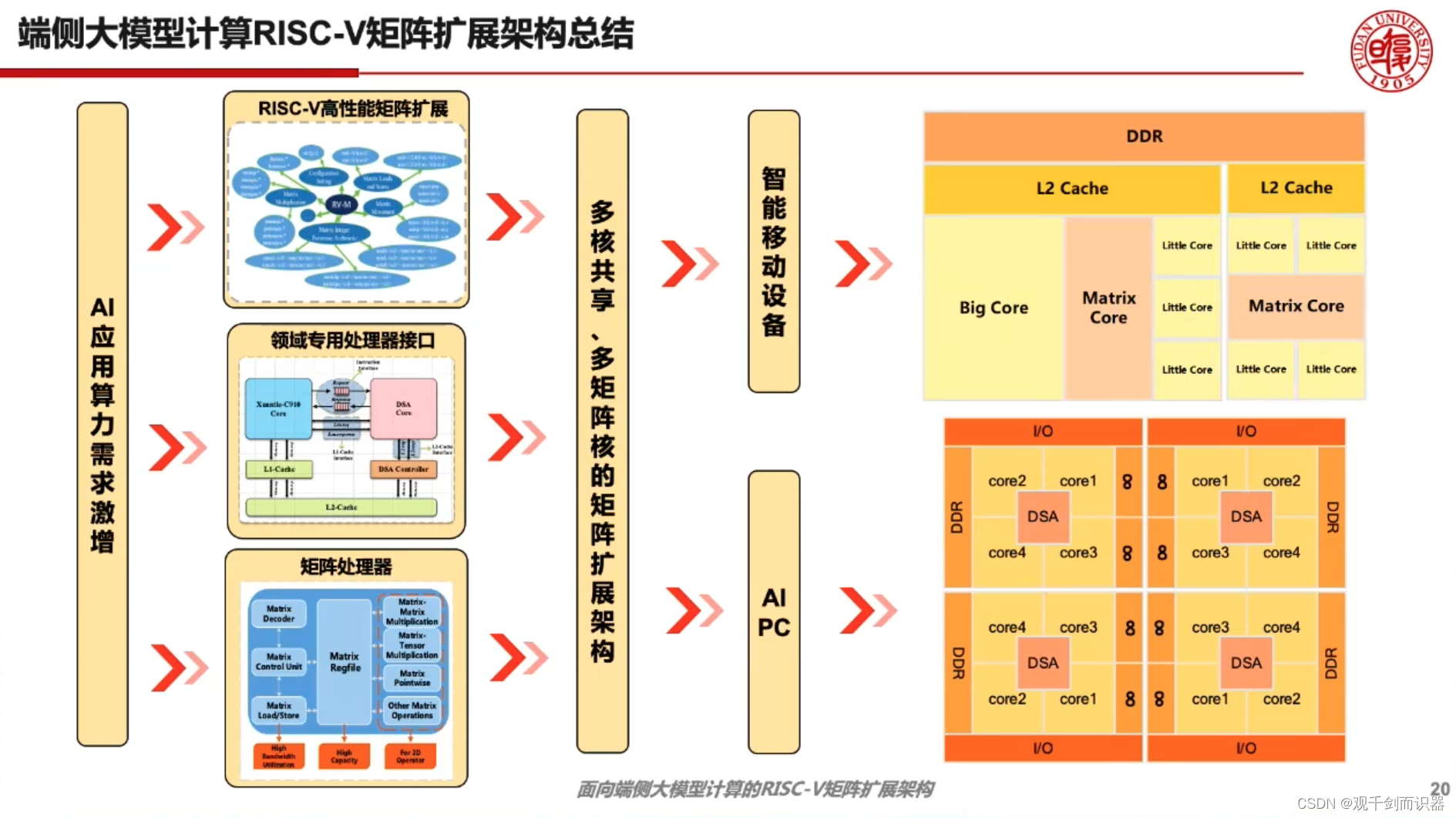

- Transformer Encoder核心是矩阵乘加运算、RISC-V向量扩展架构(平头哥向量处理器)

- 矩阵扩展指令集,更适合端侧大模型计算

- 发展AI电脑、智能移动设备,

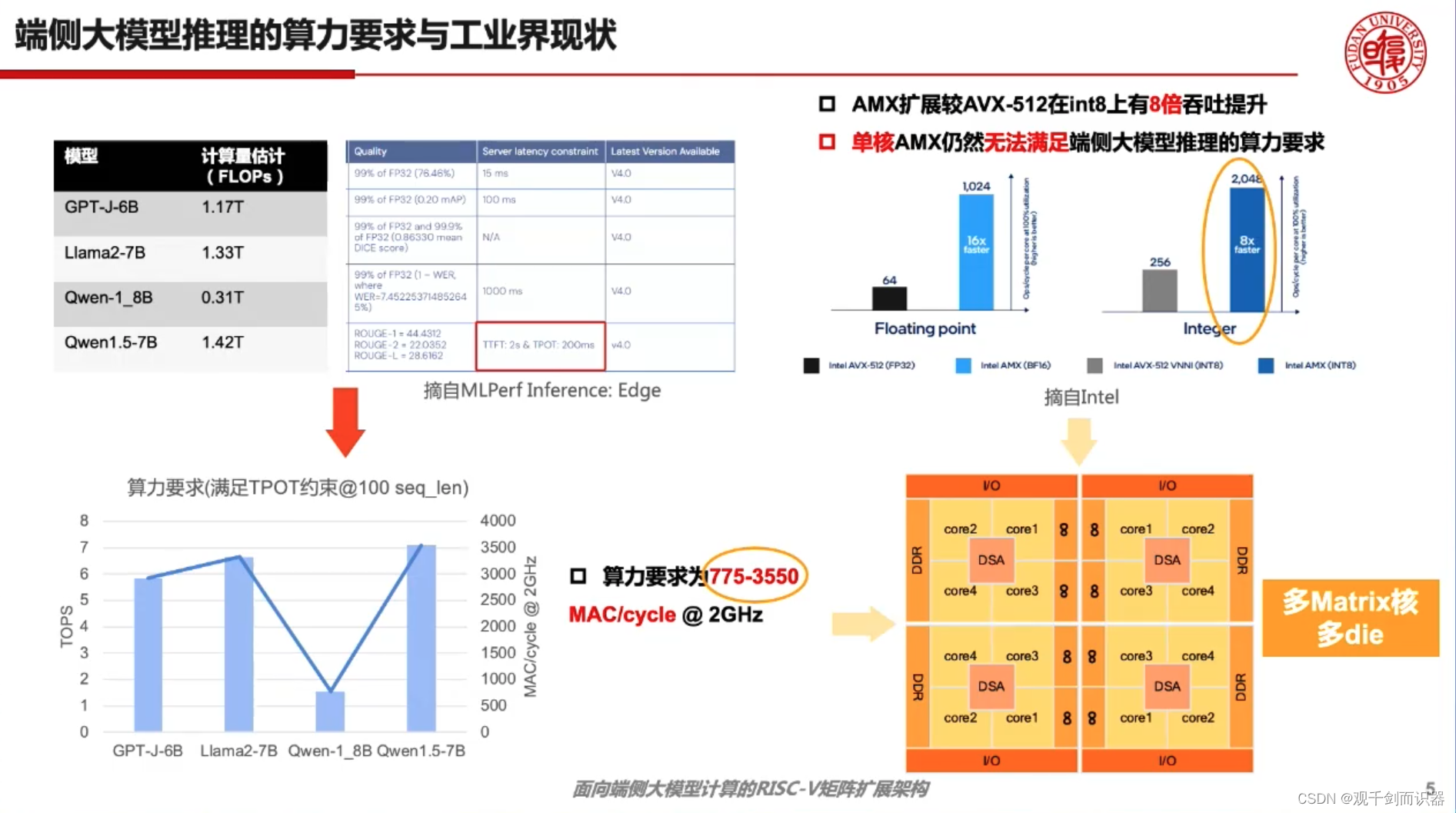

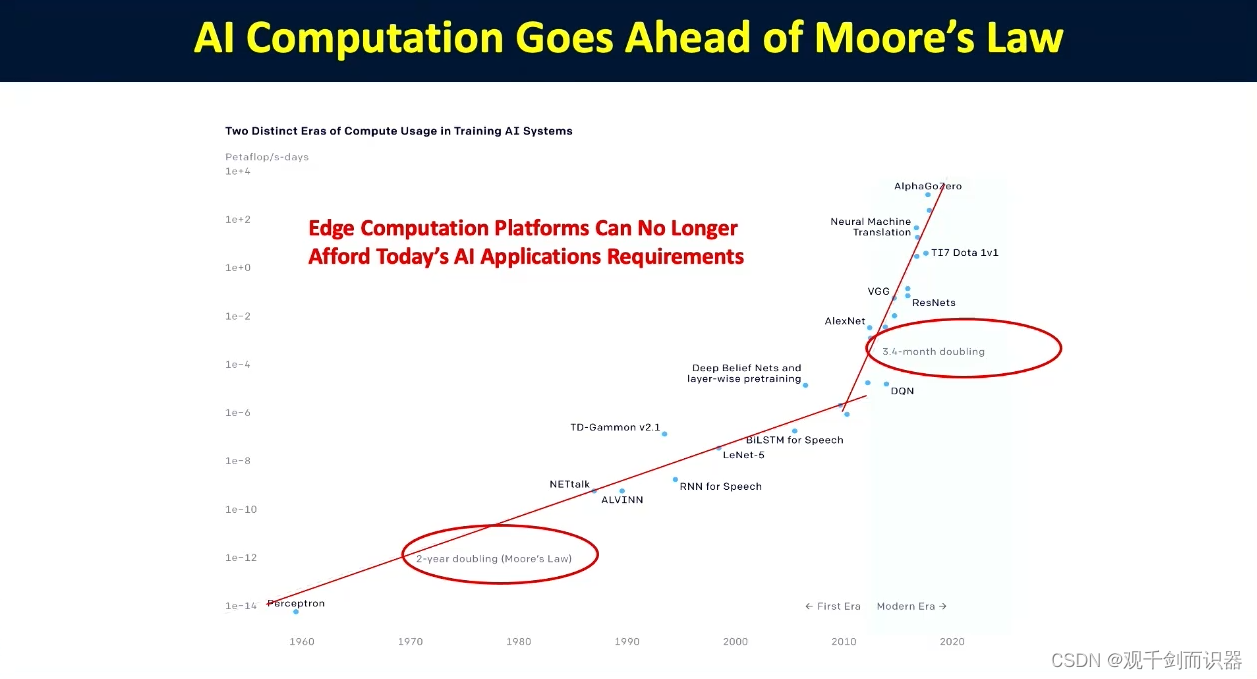

- 算力越多越好、端侧的算力却通常较小,算力指标有最低要求

把握新机遇弄潮新基建 平头哥发布1520计划

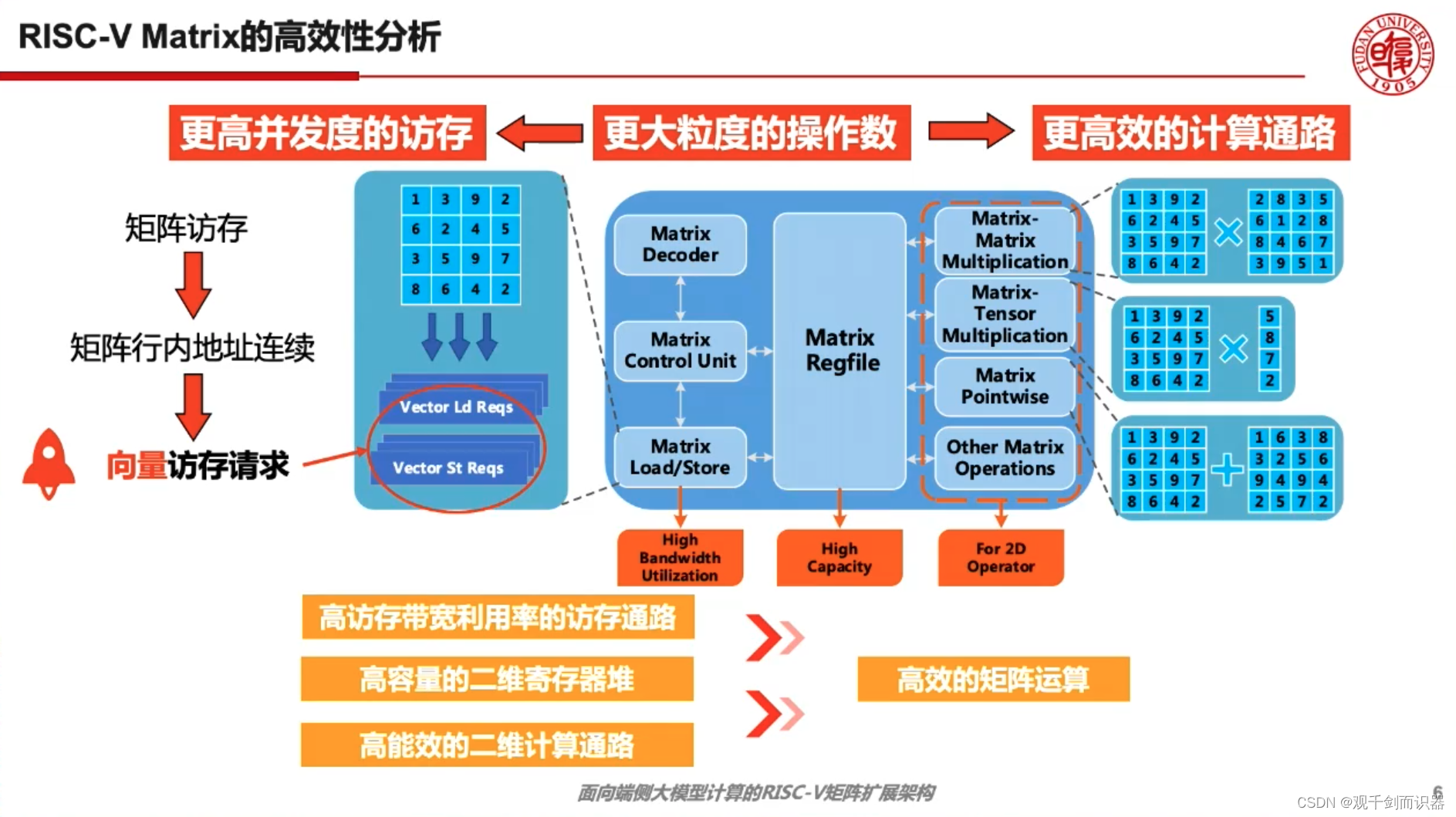

- RISC-V 矩阵扩展指令集,提供了更大操作数粒度。可设计二维矩阵乘,提升计算效率。支持更高并发度,一起64位访存,加大粒度实现连续访存,有效利用存储带宽。

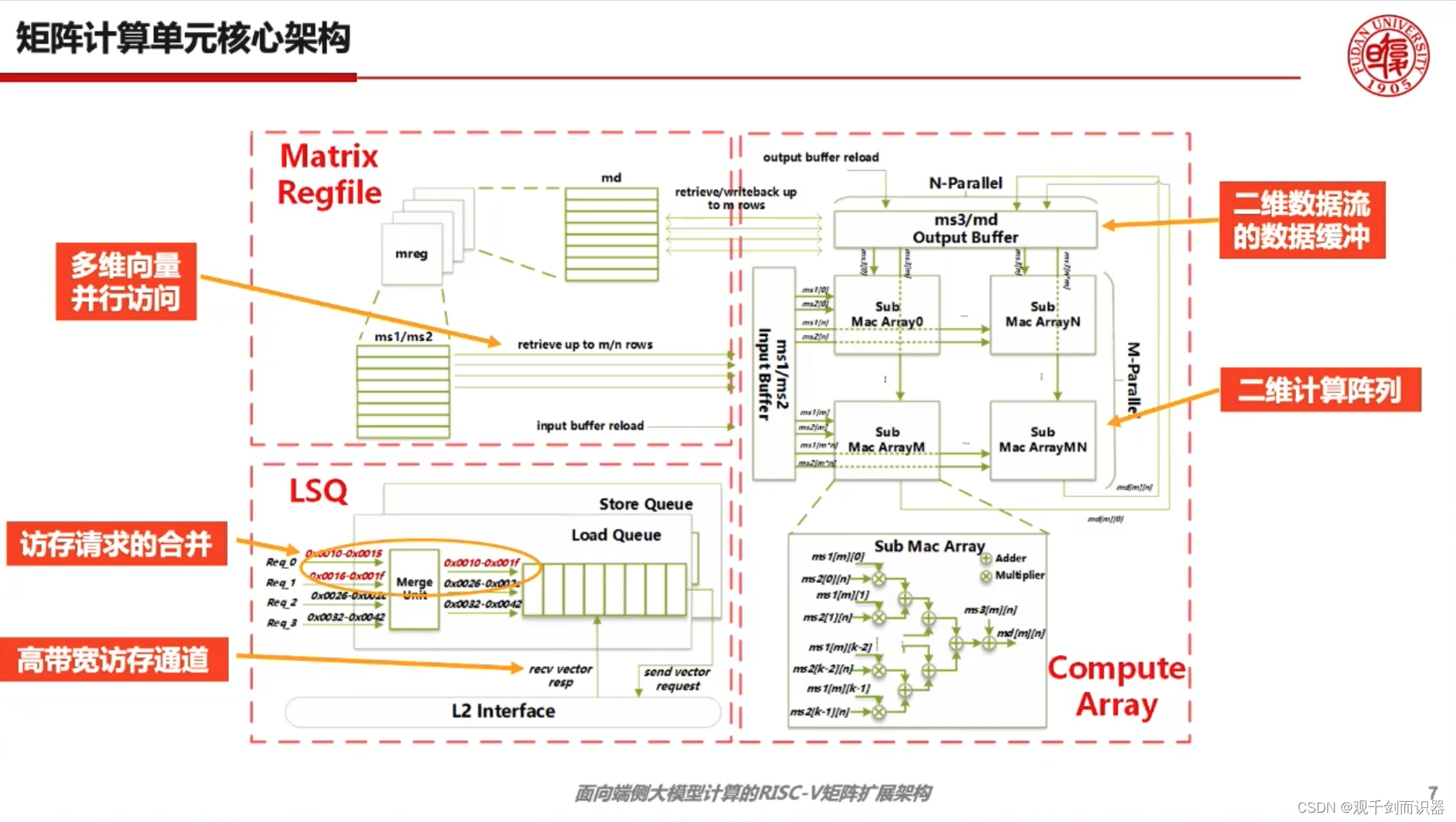

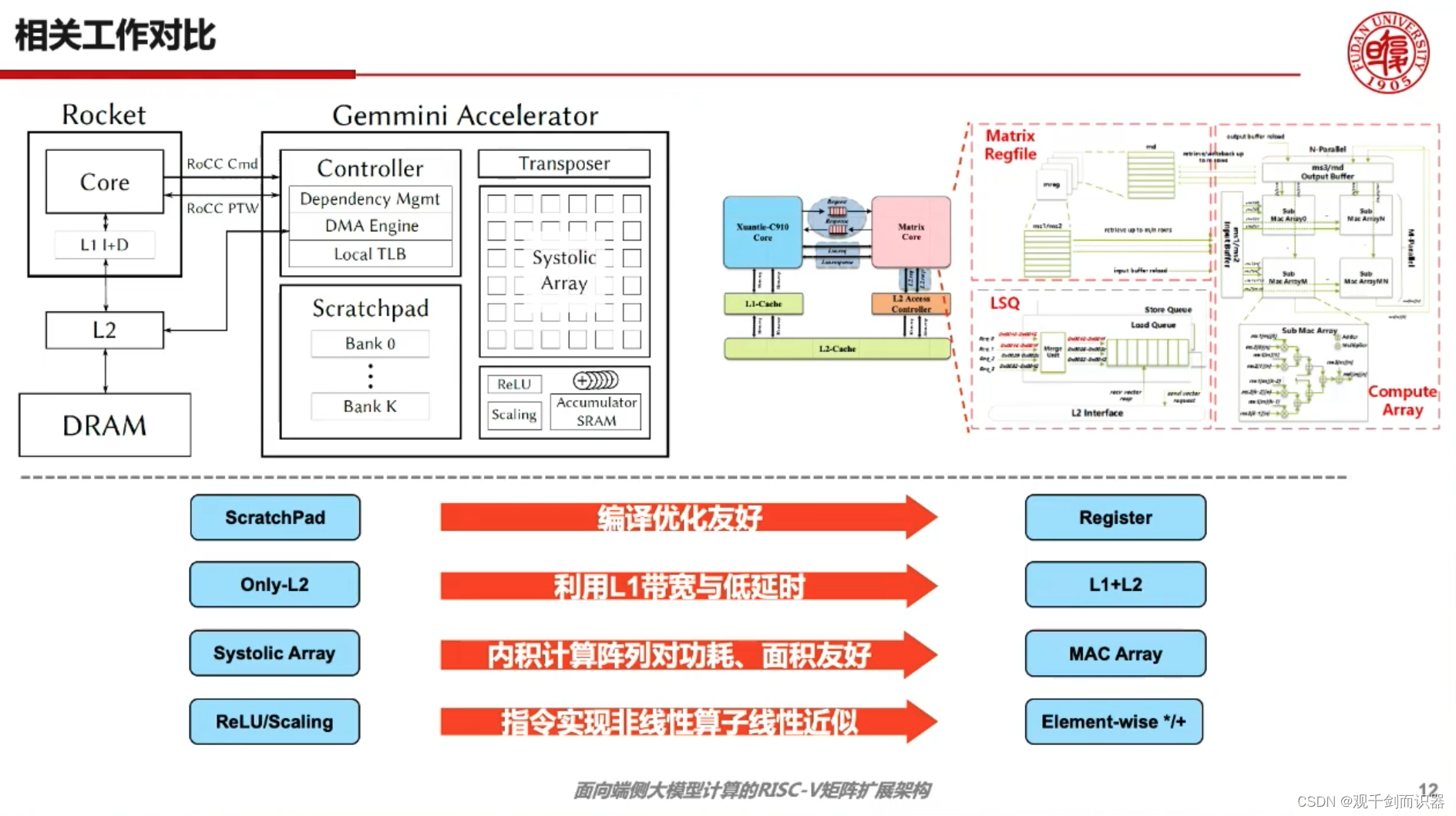

- 核心架构:二维计算阵列(神经网络加速器都会有)、Matrix RISC-V(多维向量并行访问)、矩阵访存单元(支持连续、高带宽访存,以及访存请求的合并)

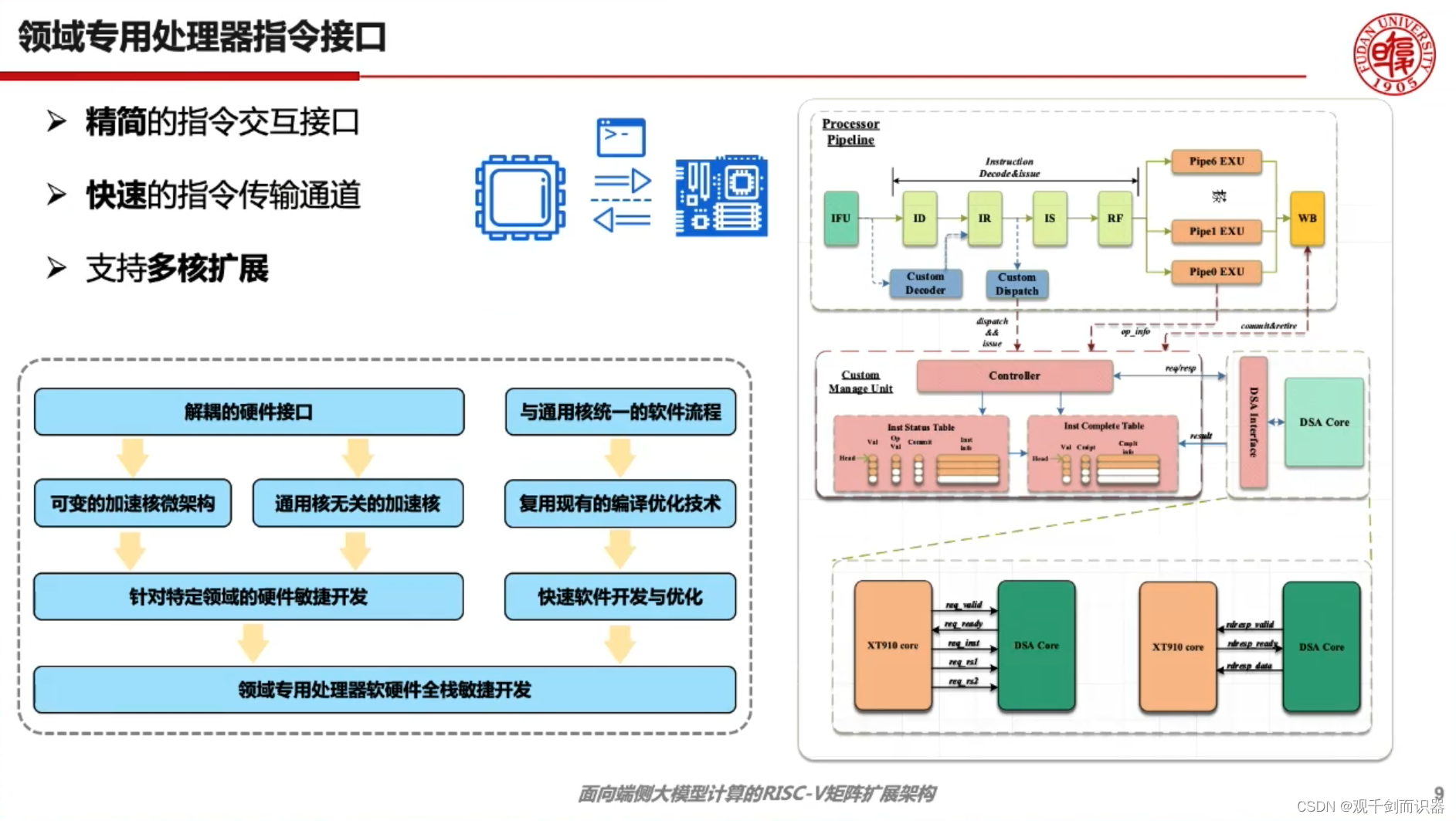

- 整合矩阵计算能力+通用计算,需要领域专用处理器接口(指令接口、L1访存接口、L2访存接口),DSA架构

- 接口优点:专用Core与通用Core——实现硬件解耦、专用Core共用软件栈且复用编译环境——实现软件统一,硬件加速与软件统一。

- 采用二级译码结构,将宏指令译码为微指令,再执行

- 三级流水线,访存、Matrix计算、CSR和寄存器堆可配置

- 超标量的思想,支持乱序执行。编译友好、L1L2访存、指令组合代替非线性操作单元

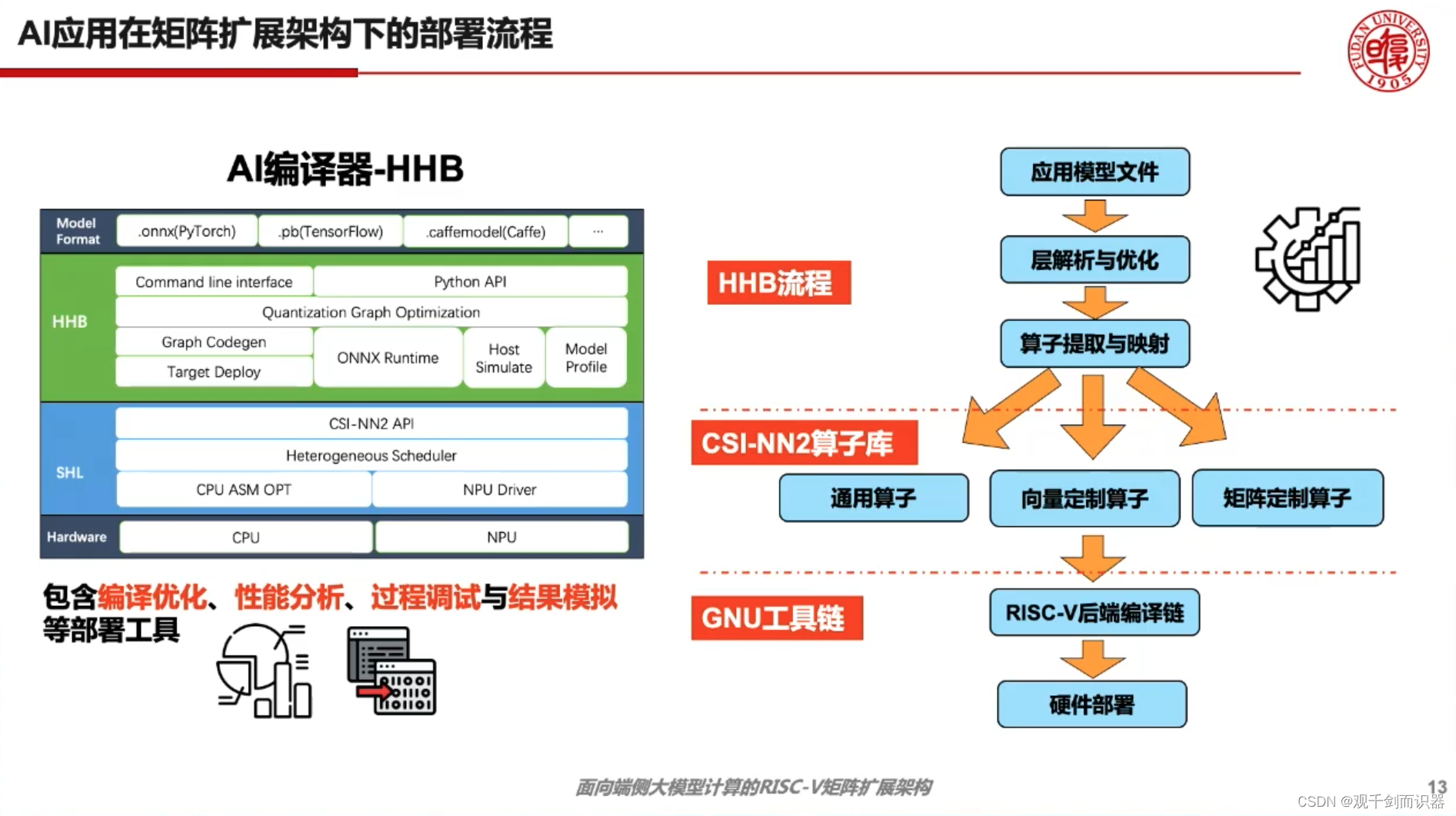

- DSA的通用处理器实现了可接入通用编译流程,

平头哥RISC-V 工具链-HHB神经网络模型部署工具

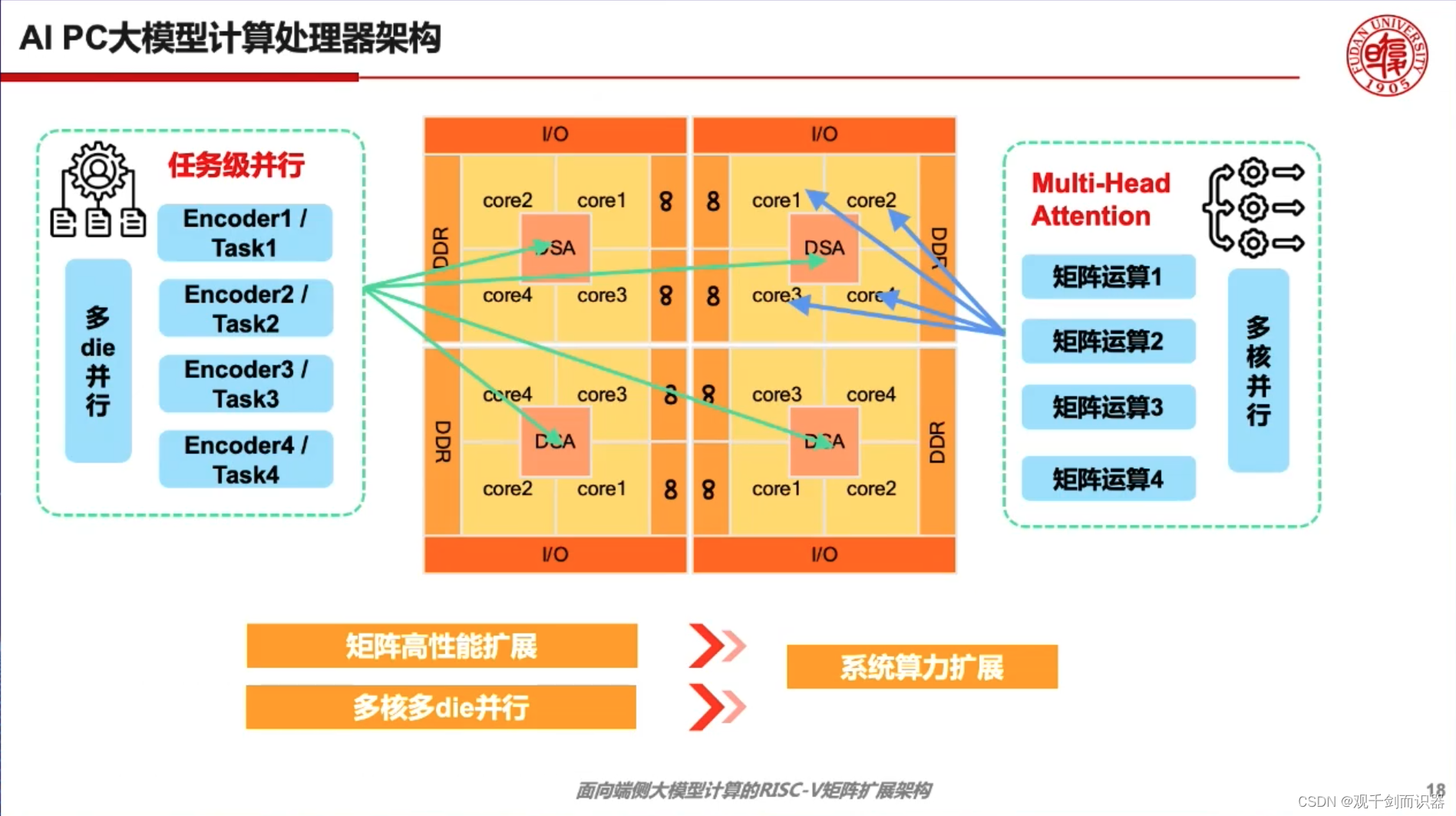

- AI PC高算力要求的场景,采用多核多die并行;

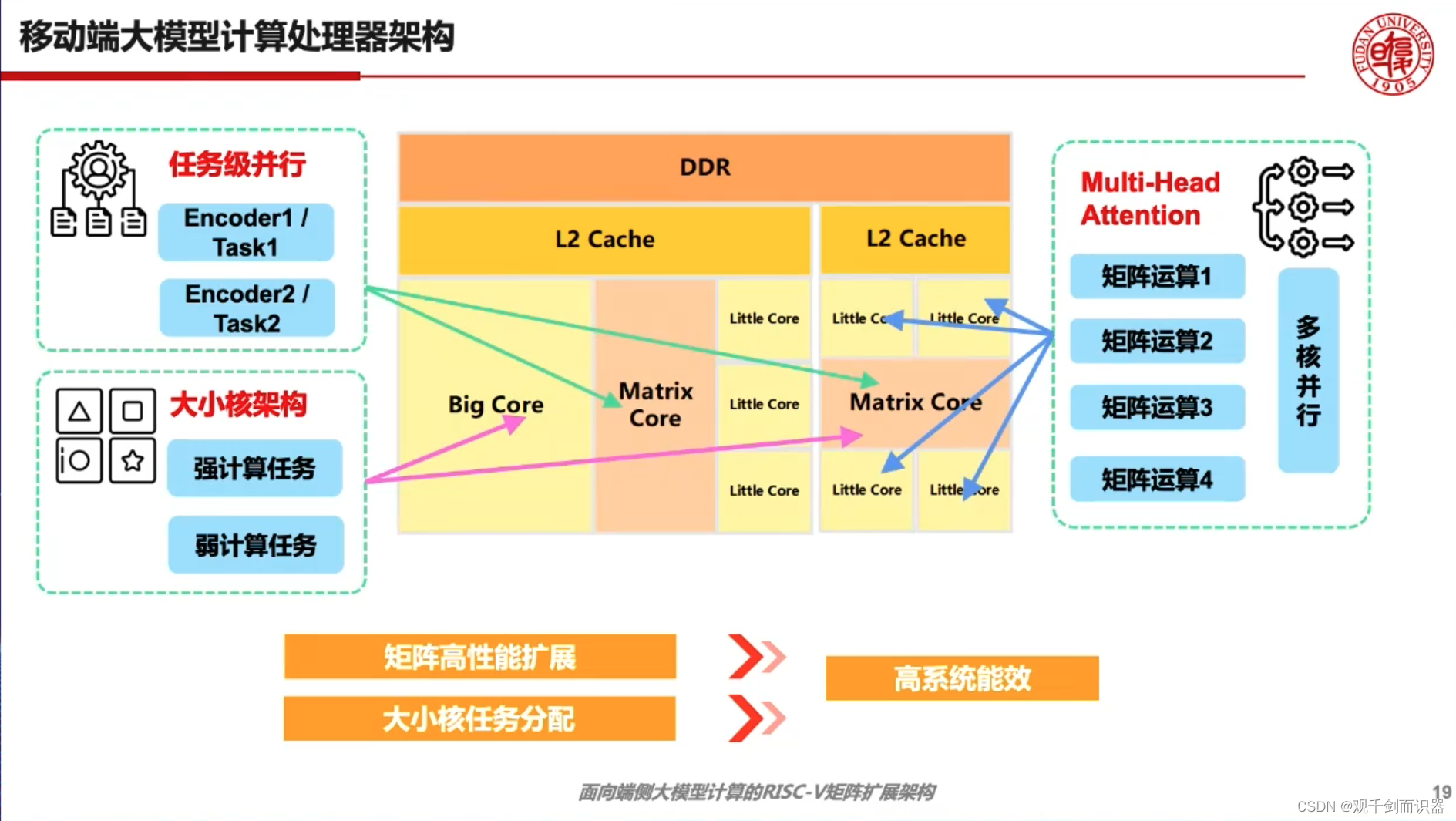

- 移动端小算力需求场景,采用大小核方式

基于RISC-V的神经网络加速运算算法及处理器结构优化,叶涛,南方科技大学

RISC-V ISA Extension for AI Acceleration,叶涛,南方科技大学

专题四:RISC-V与人工智能

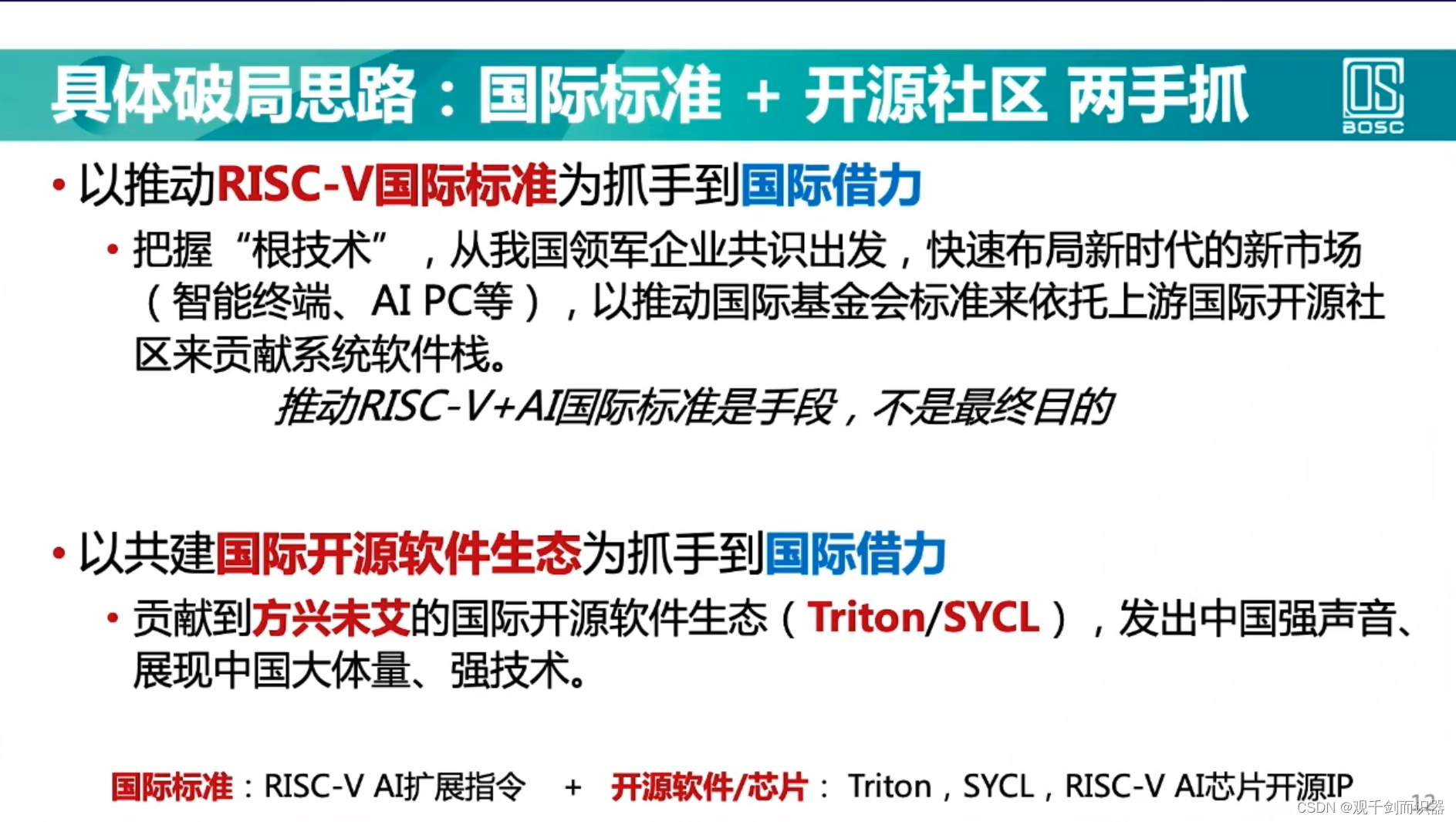

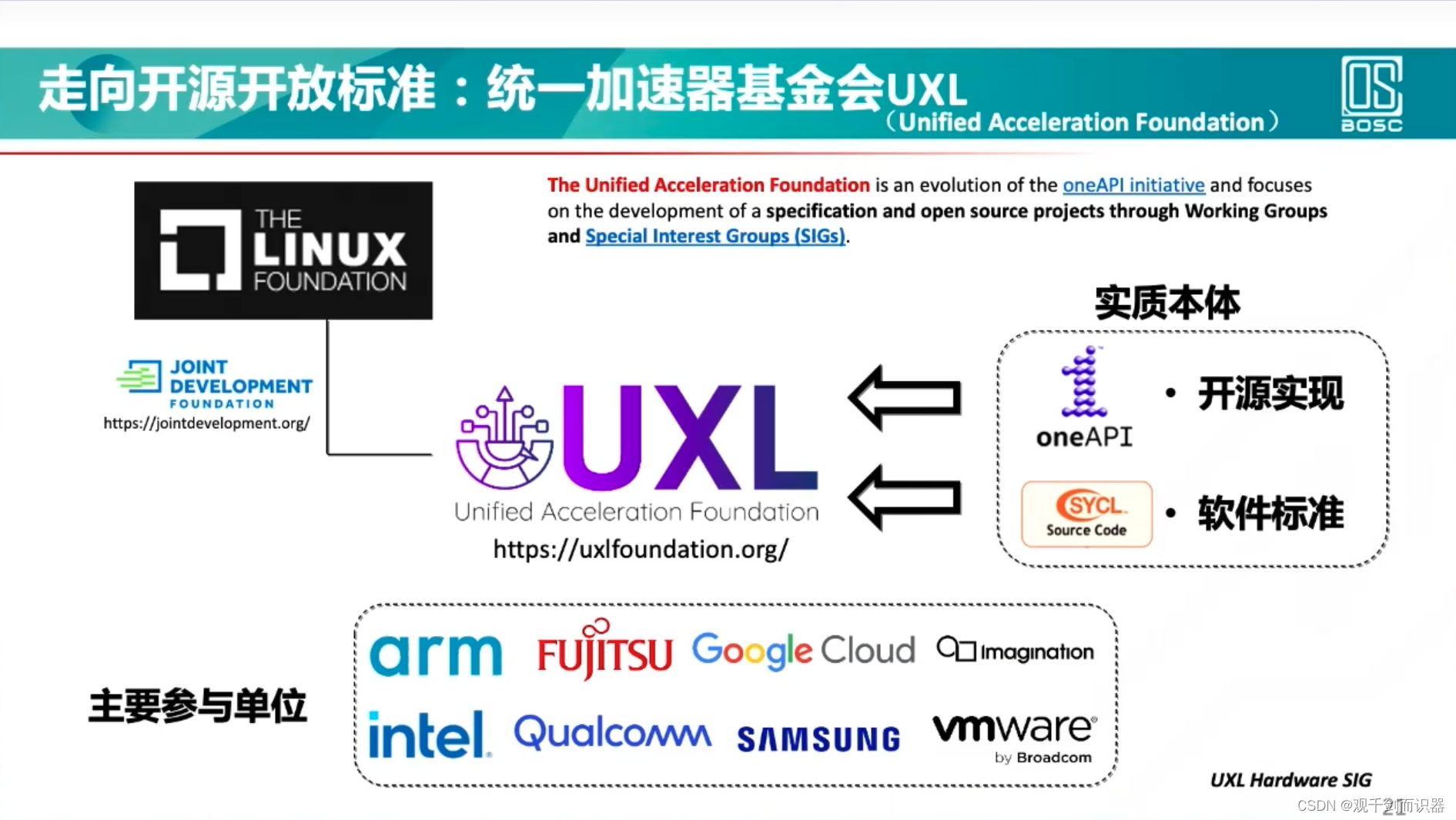

RISC-V+AI算力系统软件栈建设,谢涛,北京大学

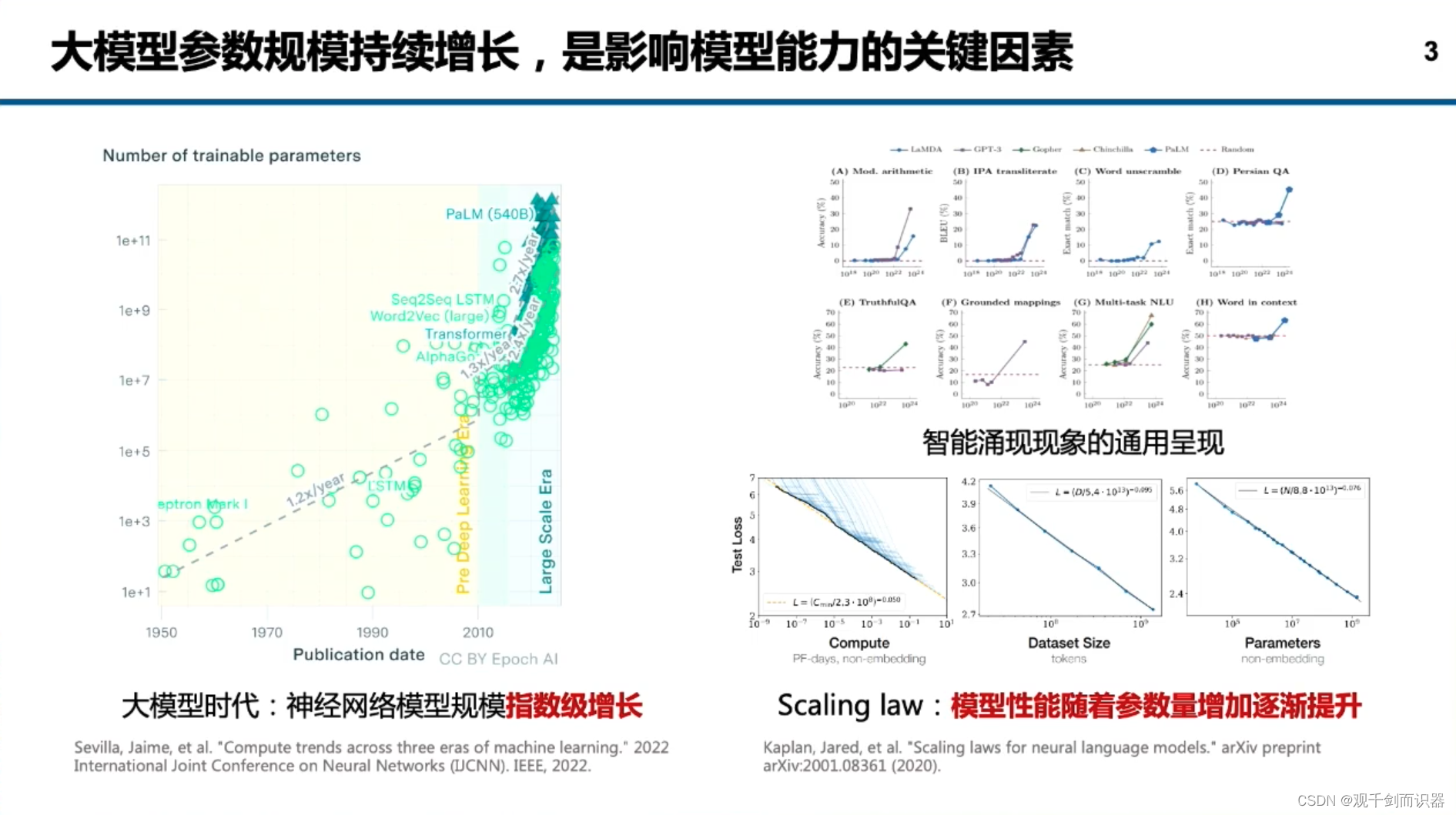

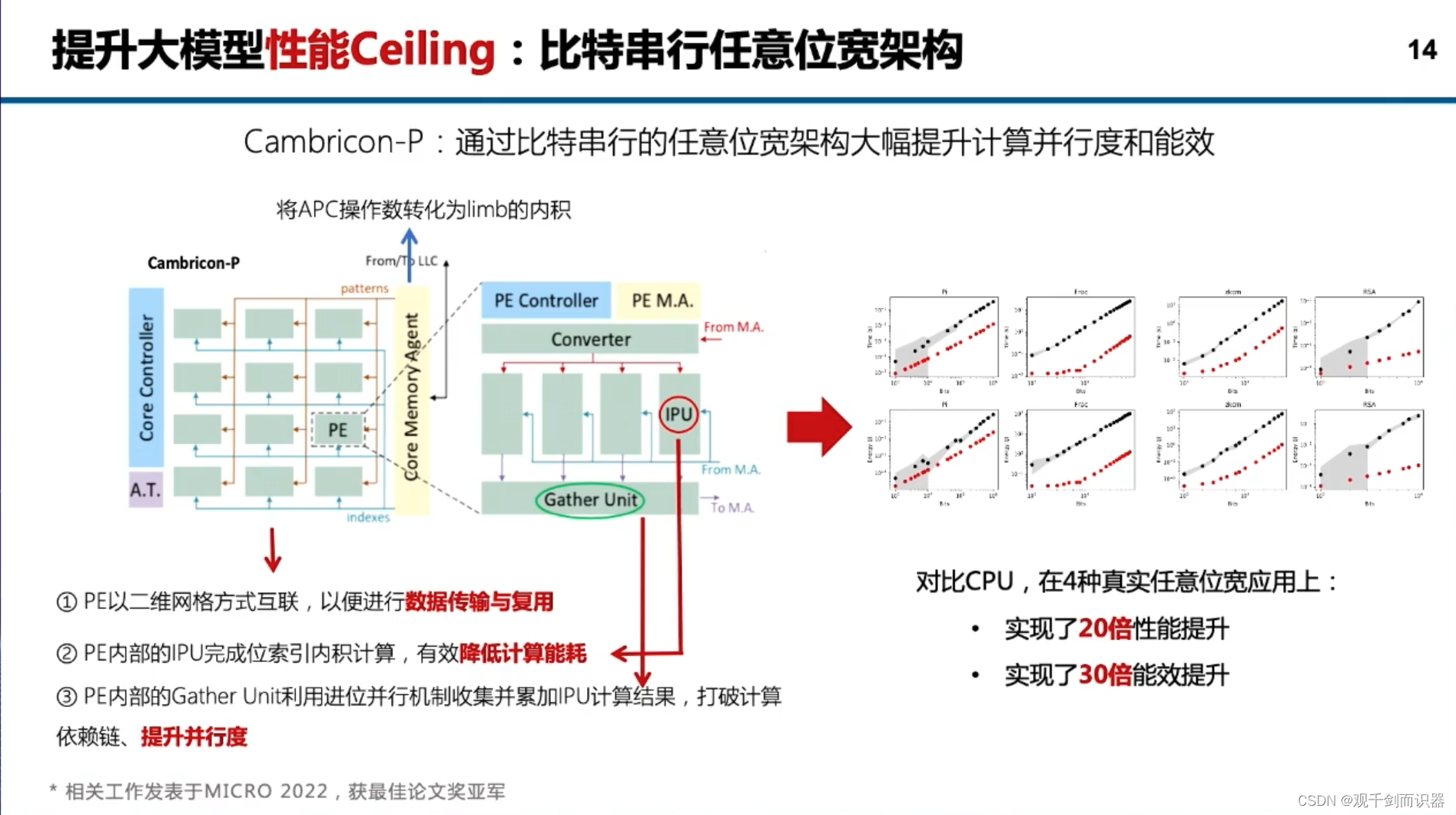

大模型AI芯片架构探索,郭崎,中国科学院计算技术研究所

b站视频传送门:大模型AI芯片架构探索 中国科学院计算技术研究所 郭崎

- 第二步,提升性能天花板;第三步,访存带宽天花板

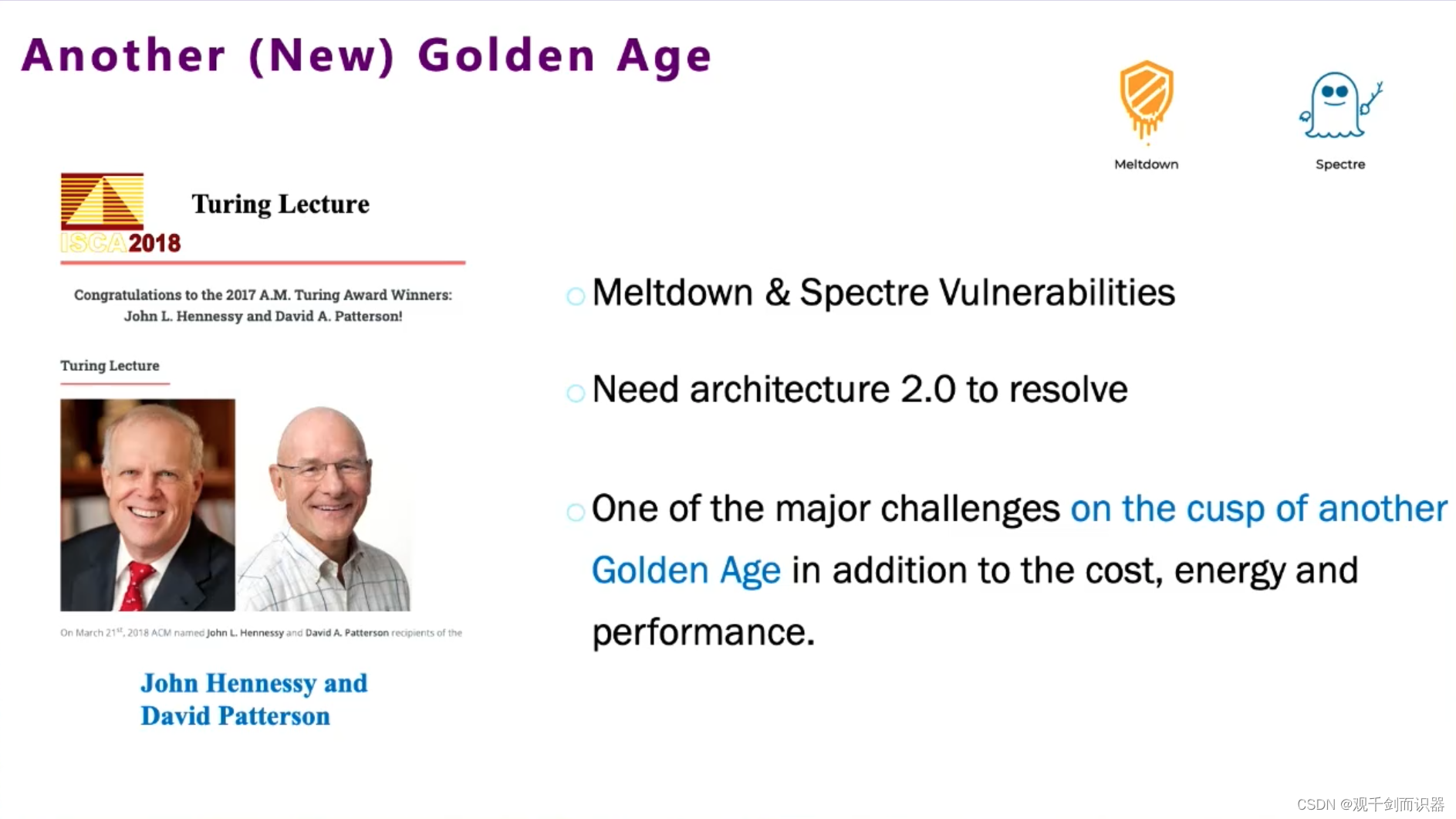

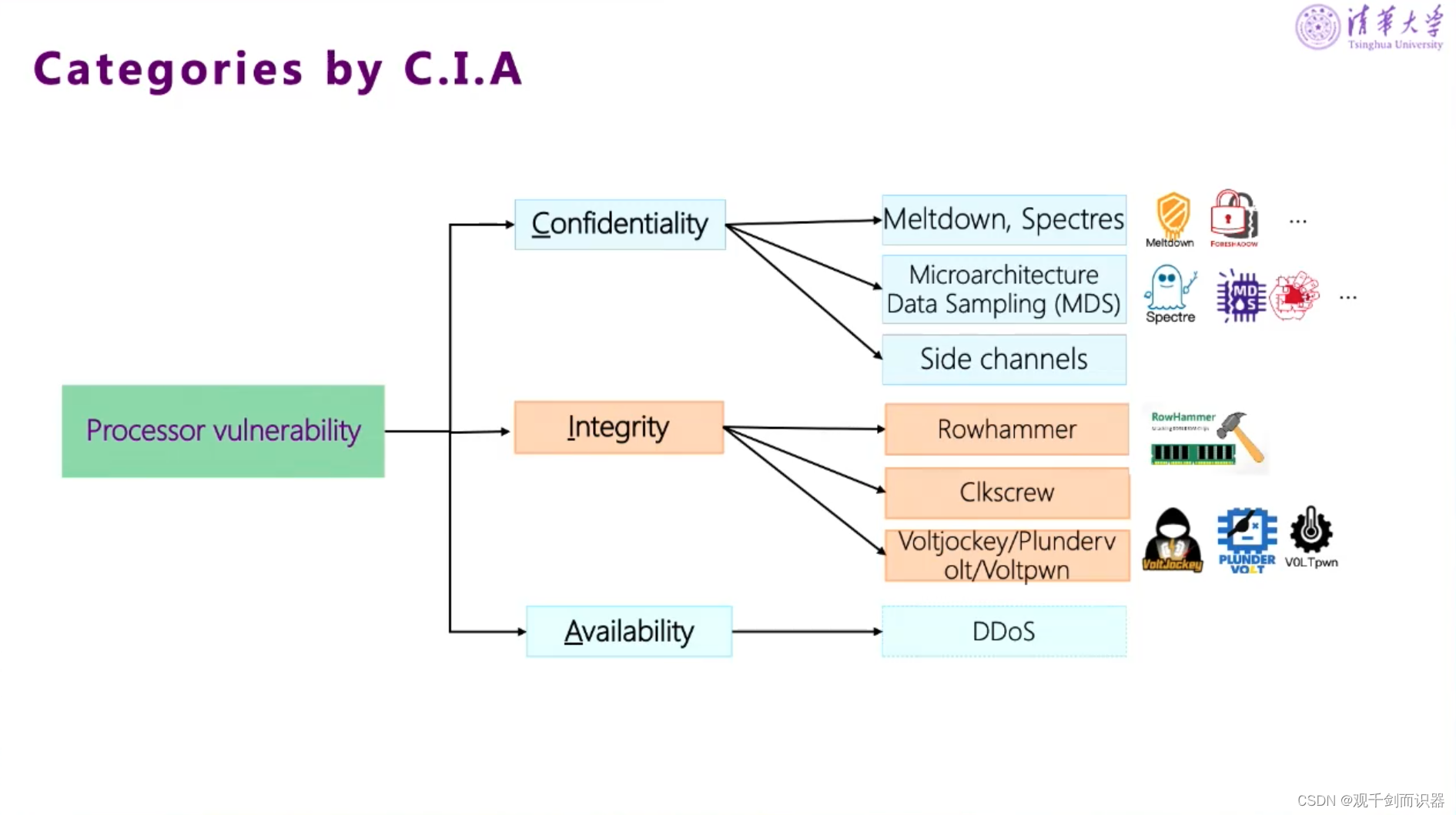

专题五:RISC-V与安全

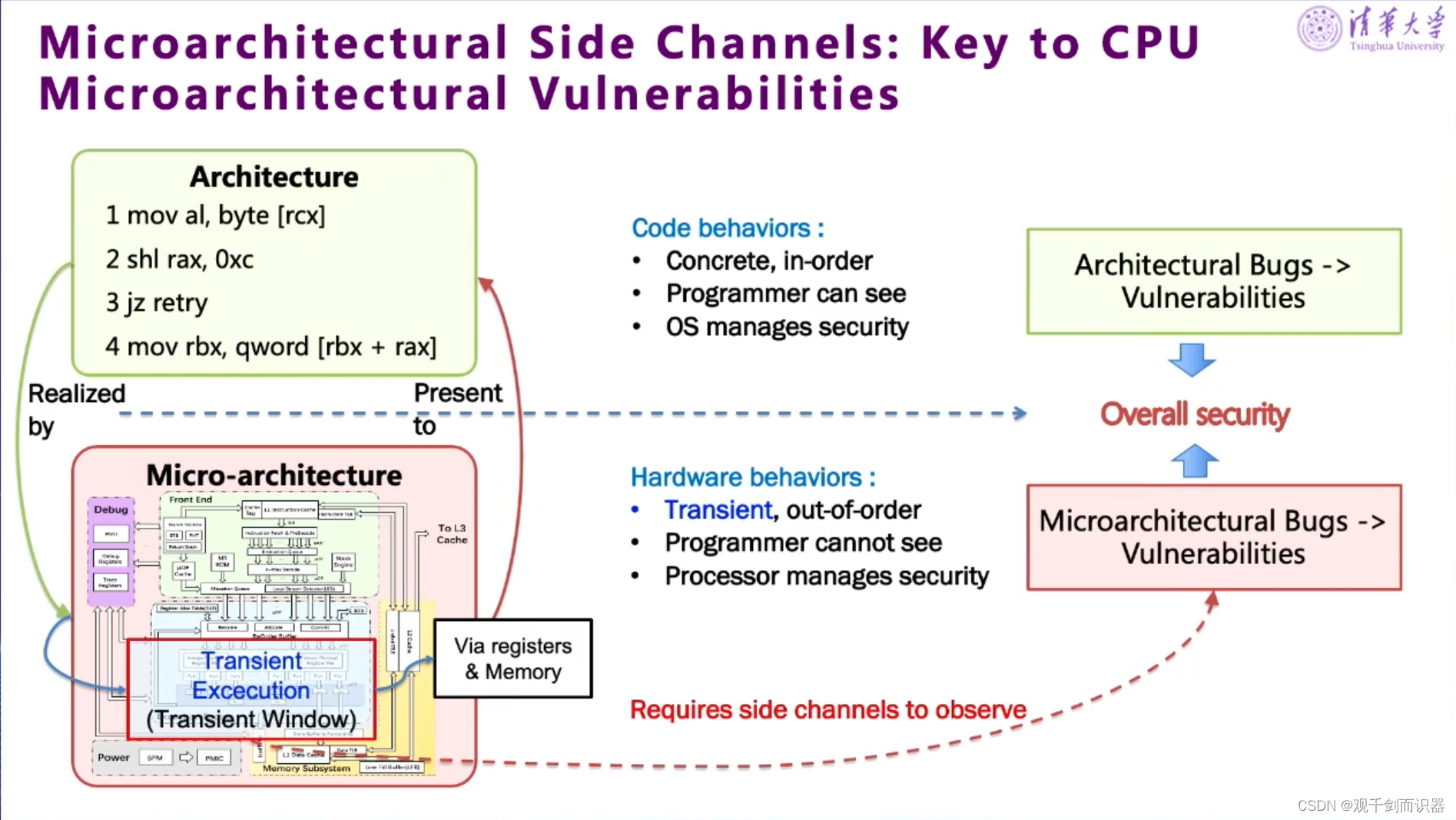

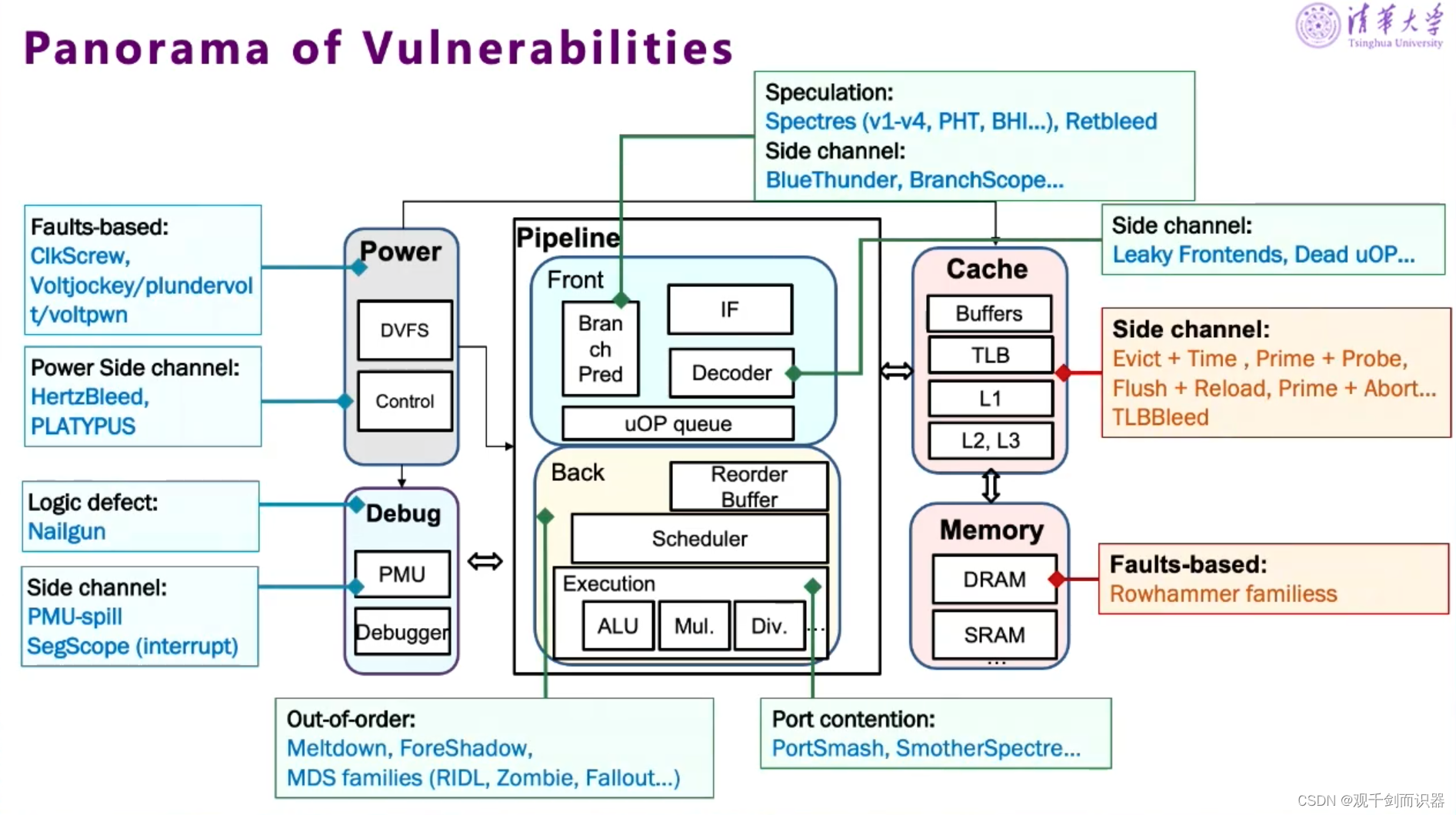

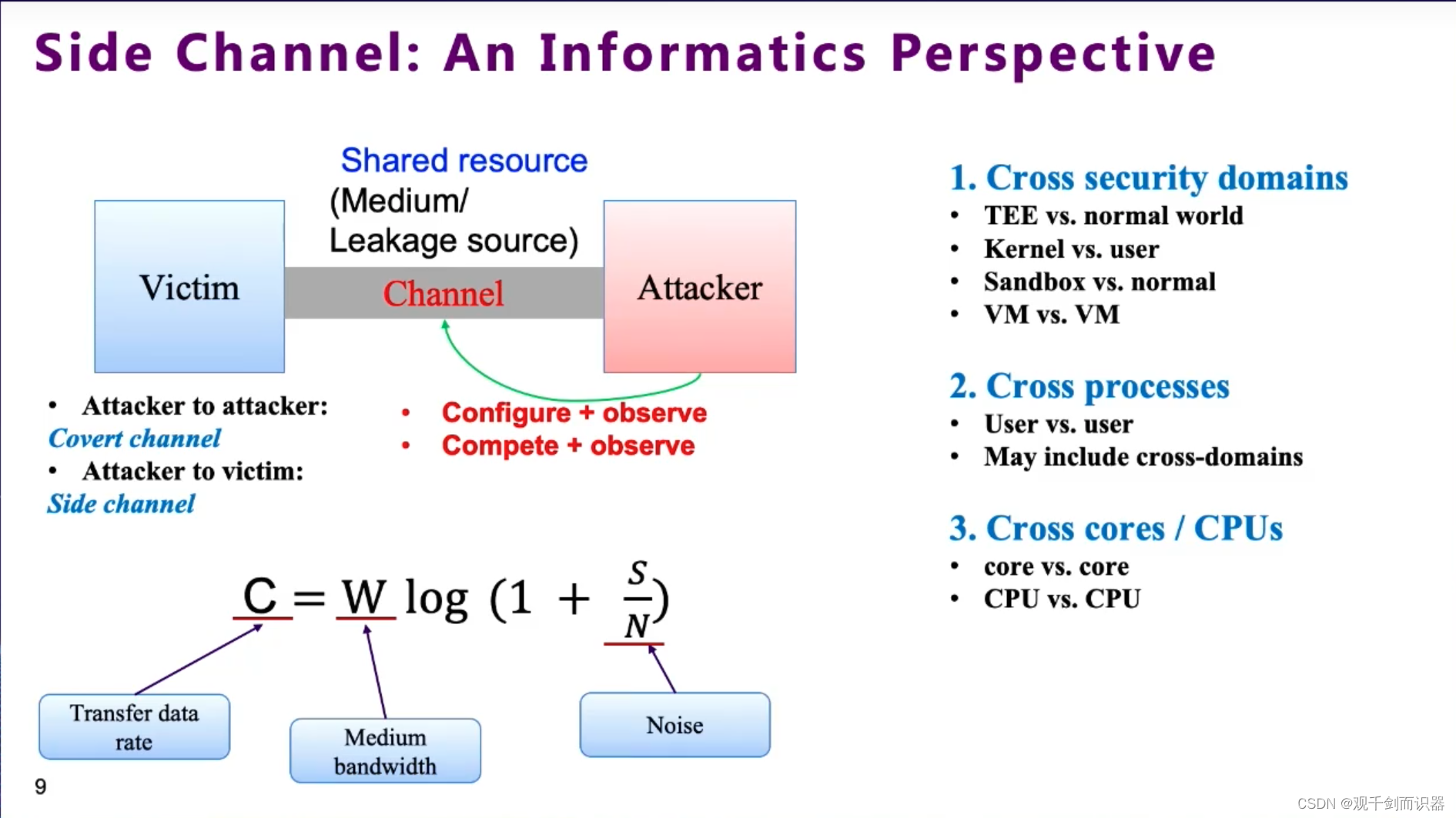

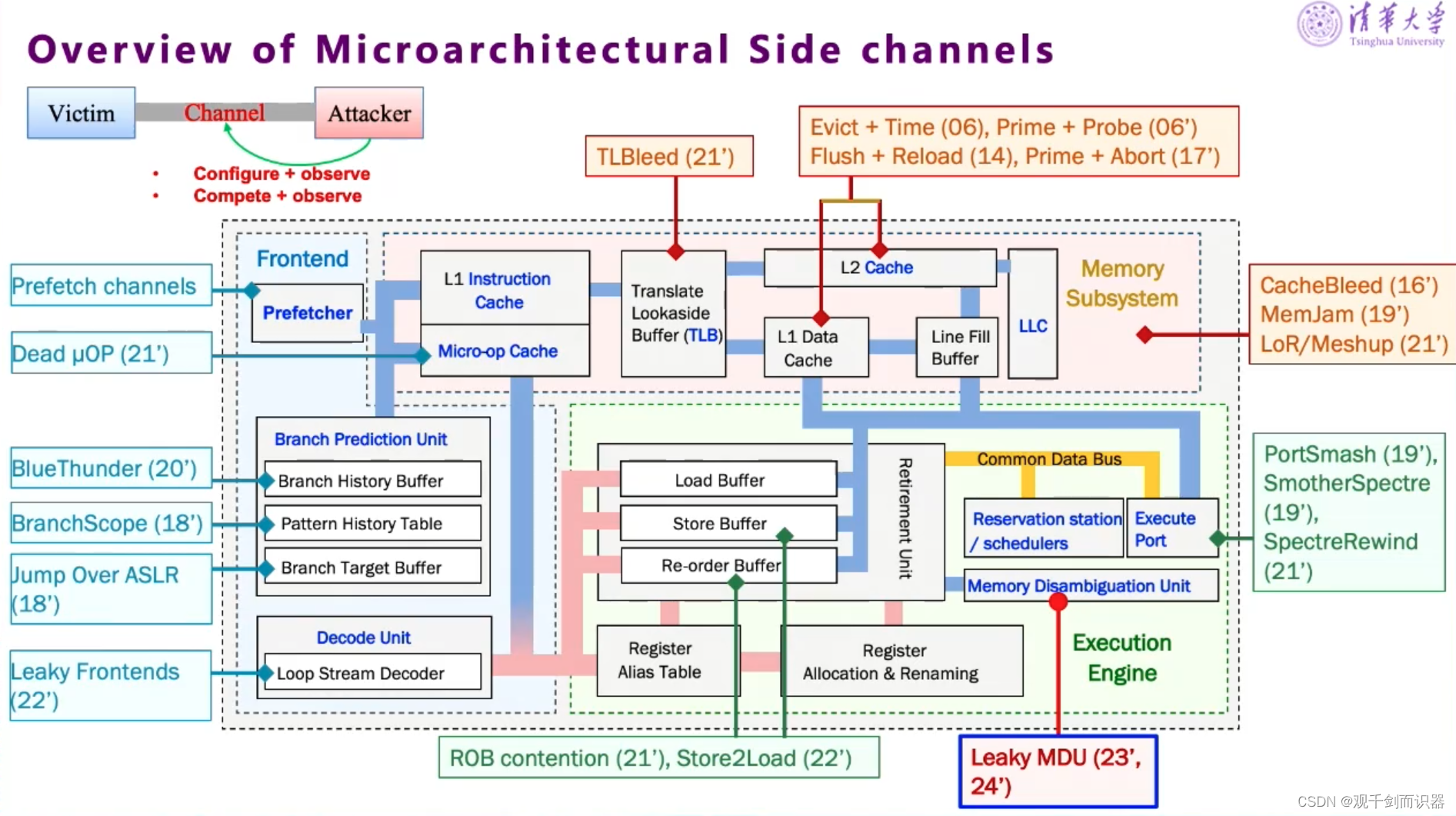

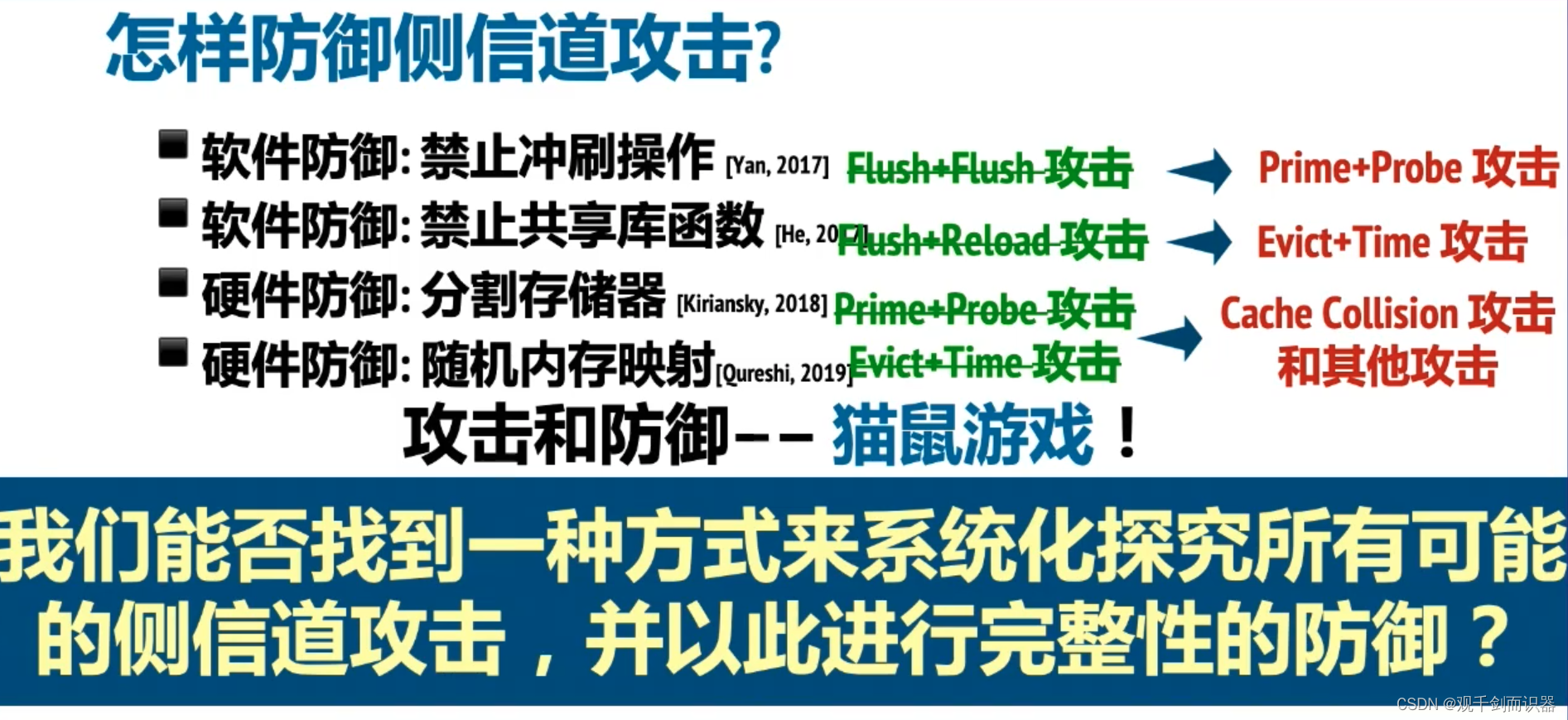

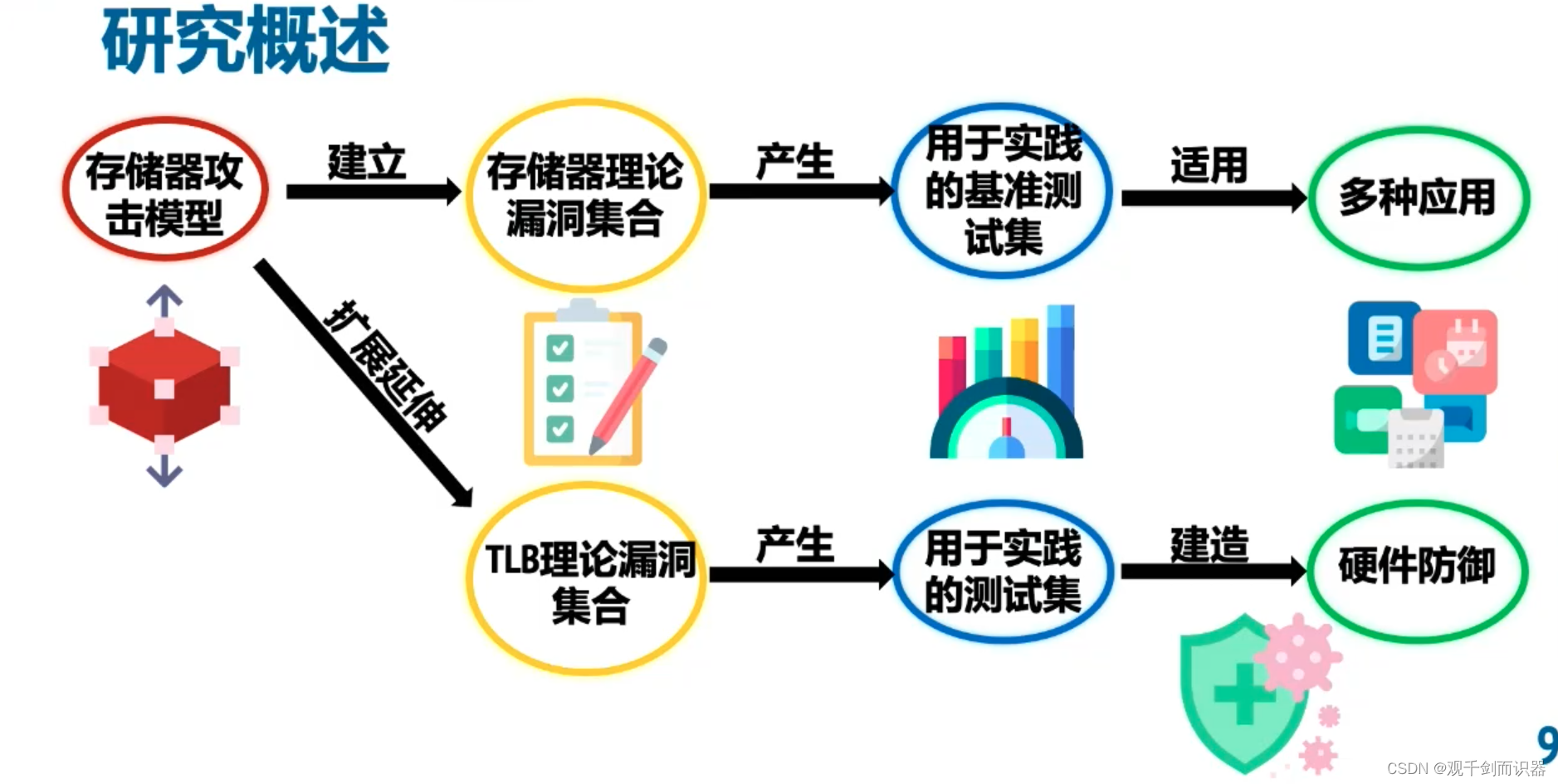

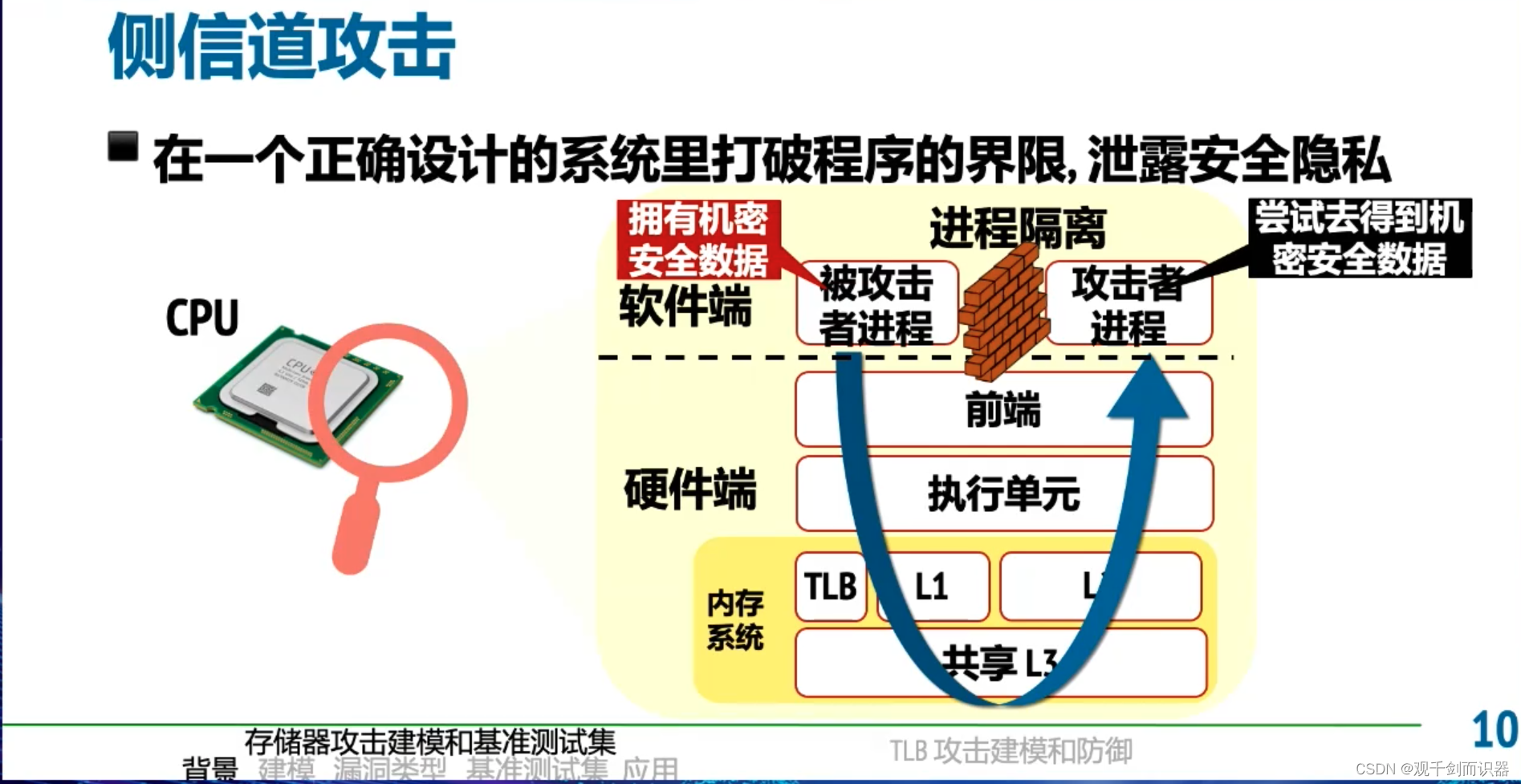

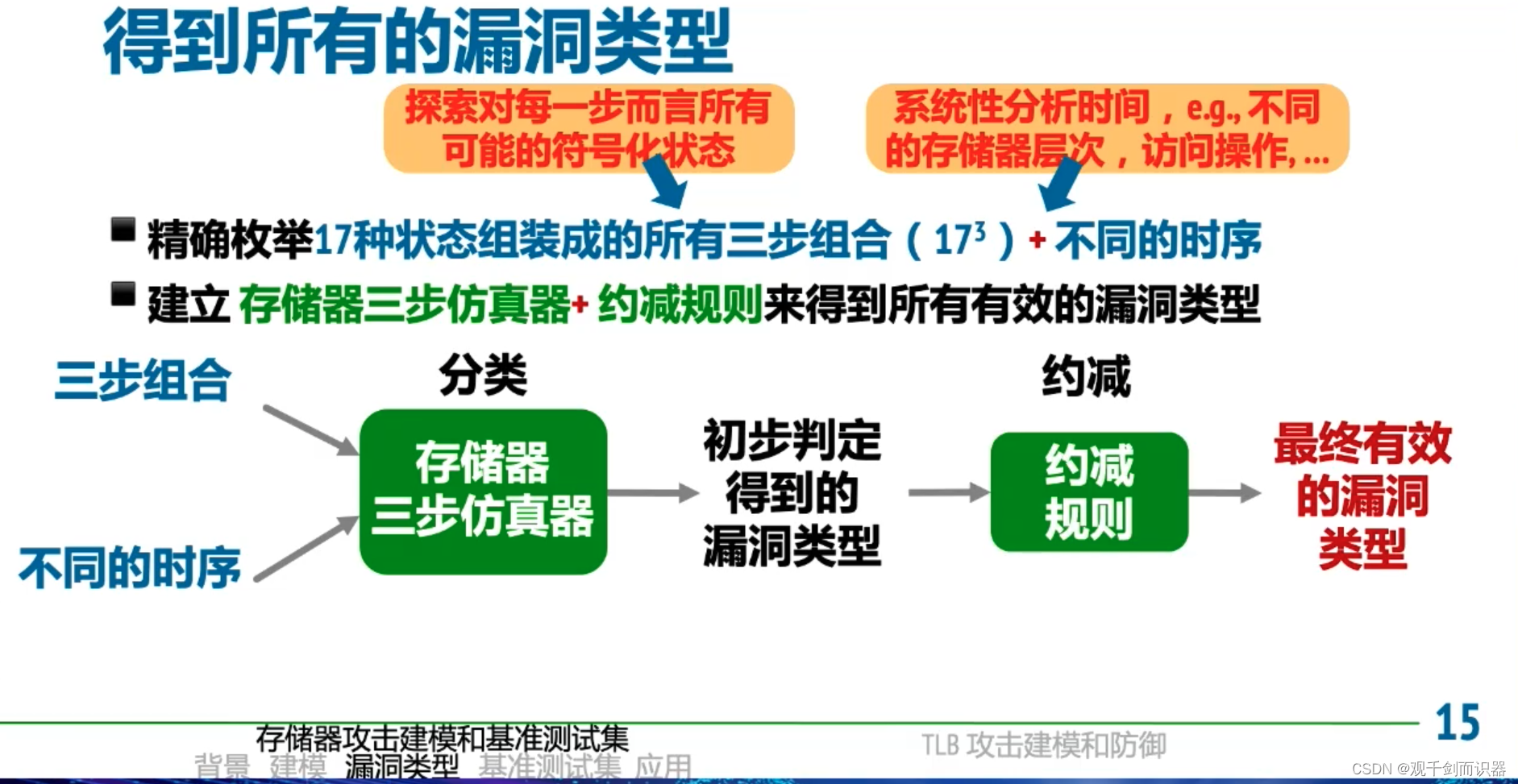

处理器侧信道攻击 吕勇强 清华大学

b站视频传送门:Microarchitectural Side Channels处理器侧信道攻击 吕勇强 清华大学 副研究员

- 处理器漏洞:私密性、完整性、可用性

- 架构指程序员能看到的部分,微架构程序员看不见(为了完成架构的功能)

- 供电(从power状态进行远程密码破译)、

- 常见物理信道:物理、能量等,攻击者在信道上对受害者进行观测,能得出受害者在做什么。所以攻击侧对受害侧所做的行为有一定的白盒知识,才能更好的获取信息

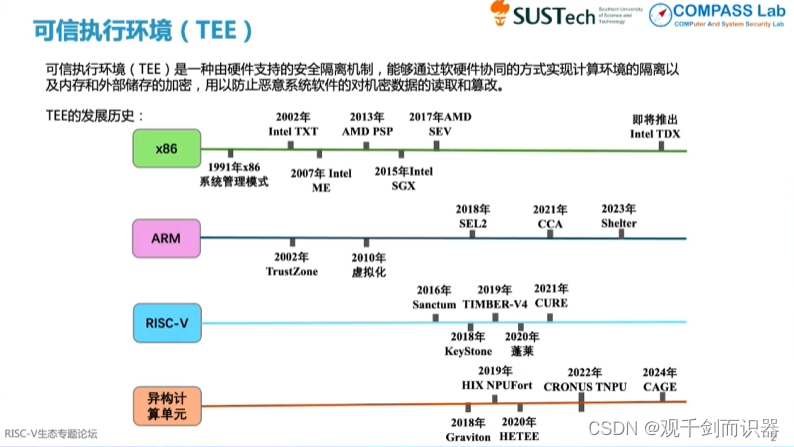

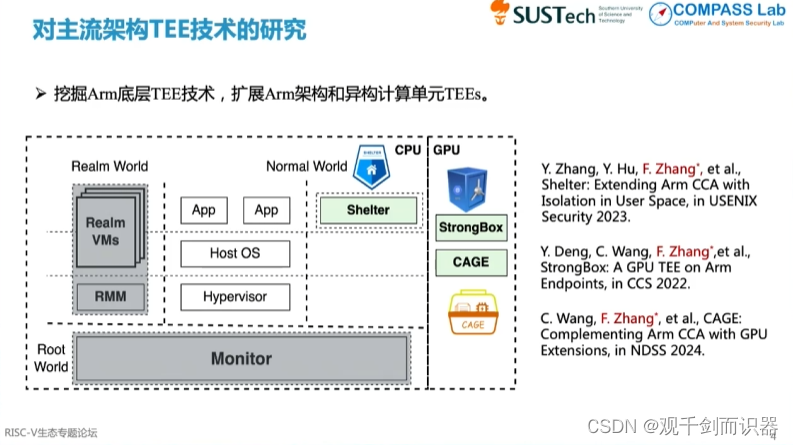

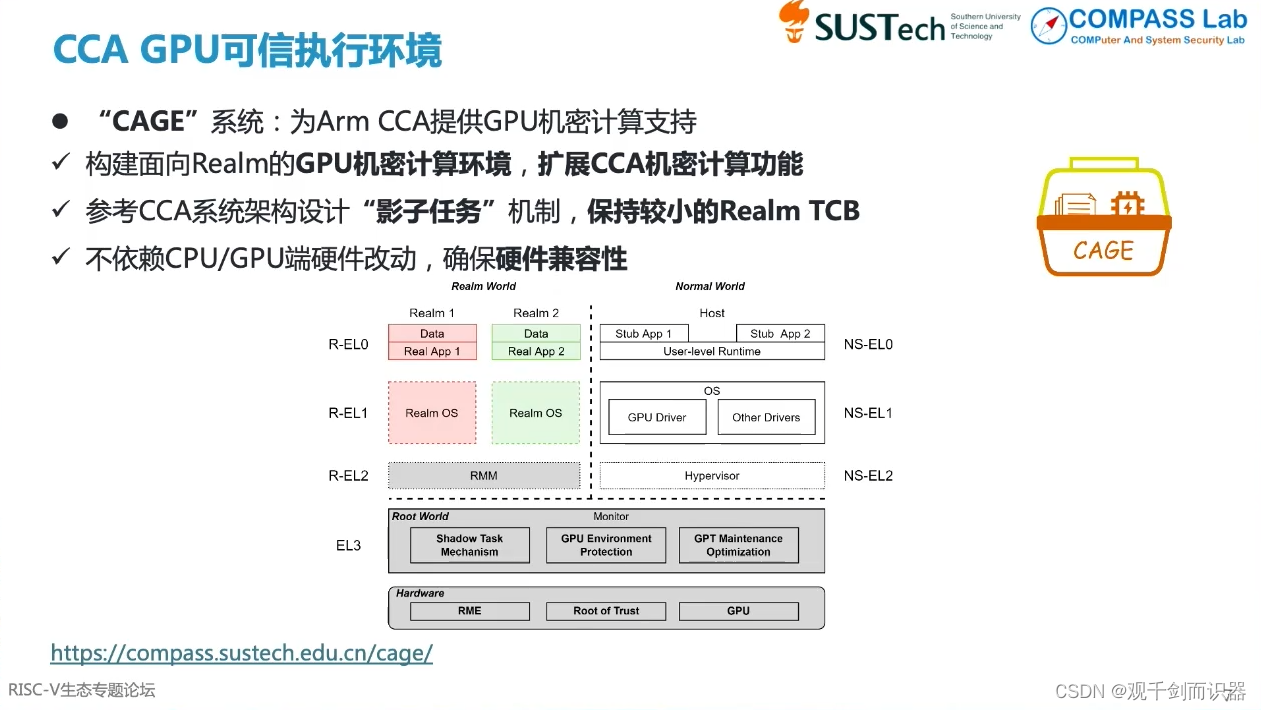

可信执行环境及关键技术研究,张锋巍,南方科技大学

b站视频传送门:可信执行环境及关键技术研究,张锋巍,南方科技大学

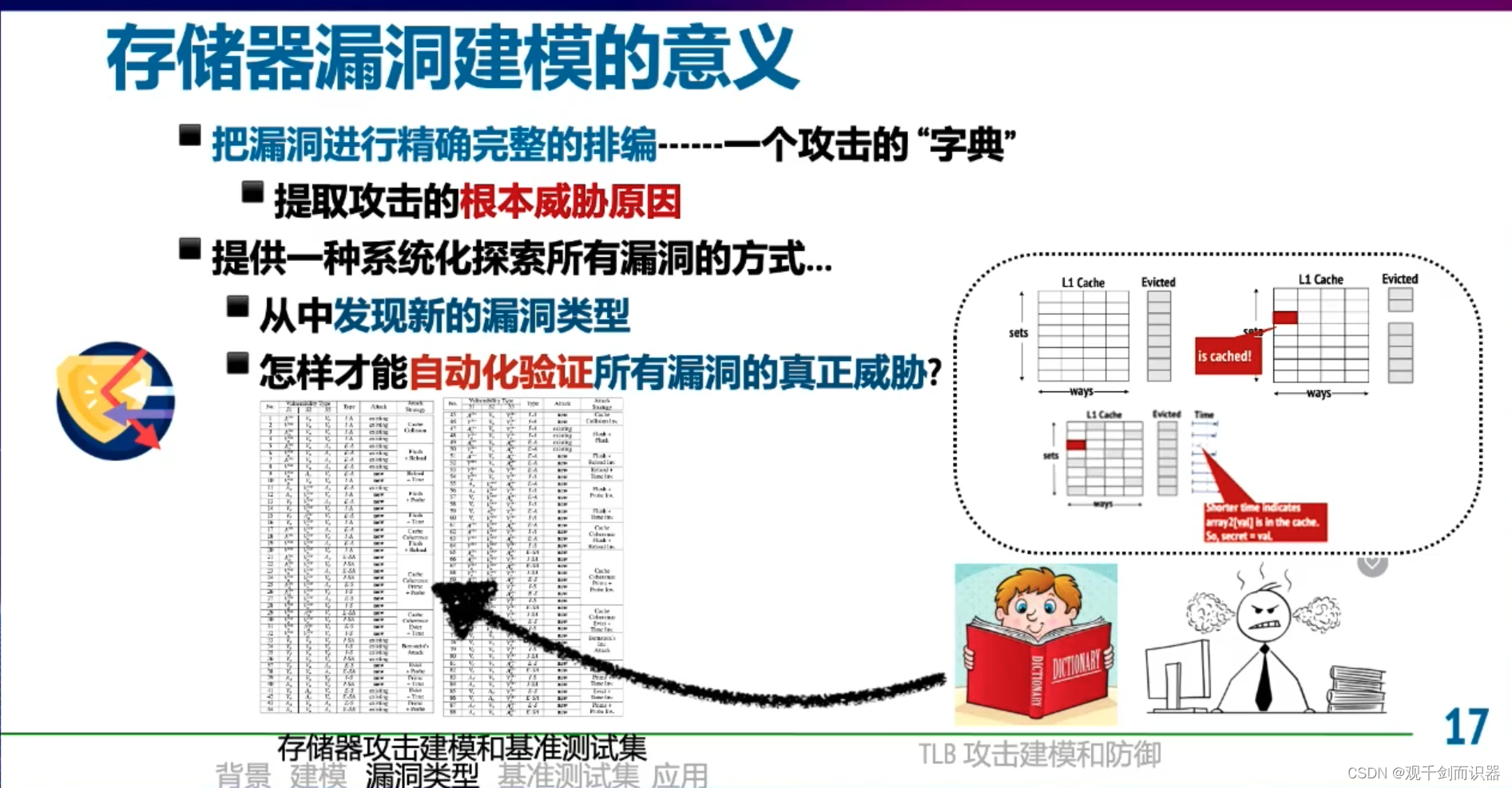

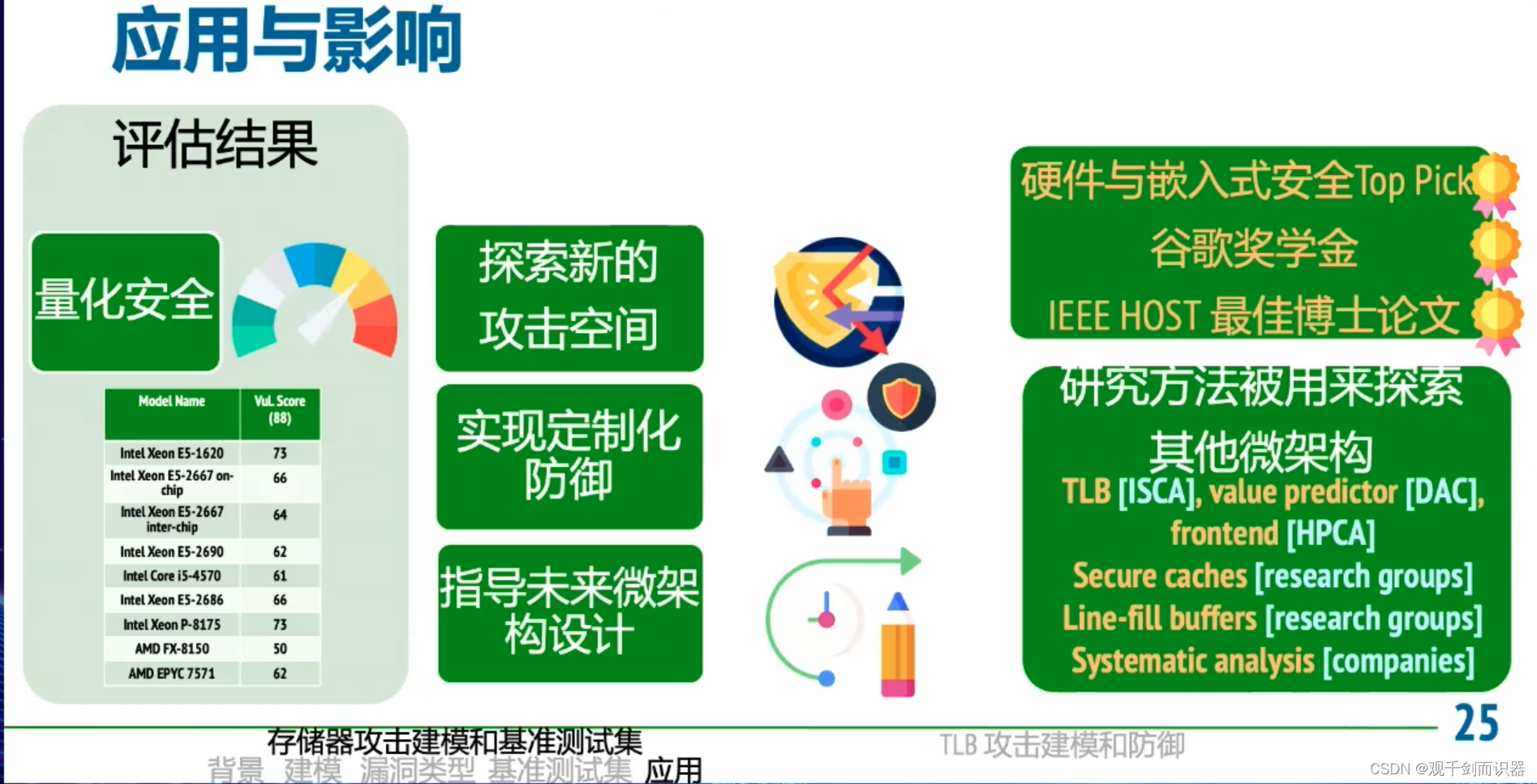

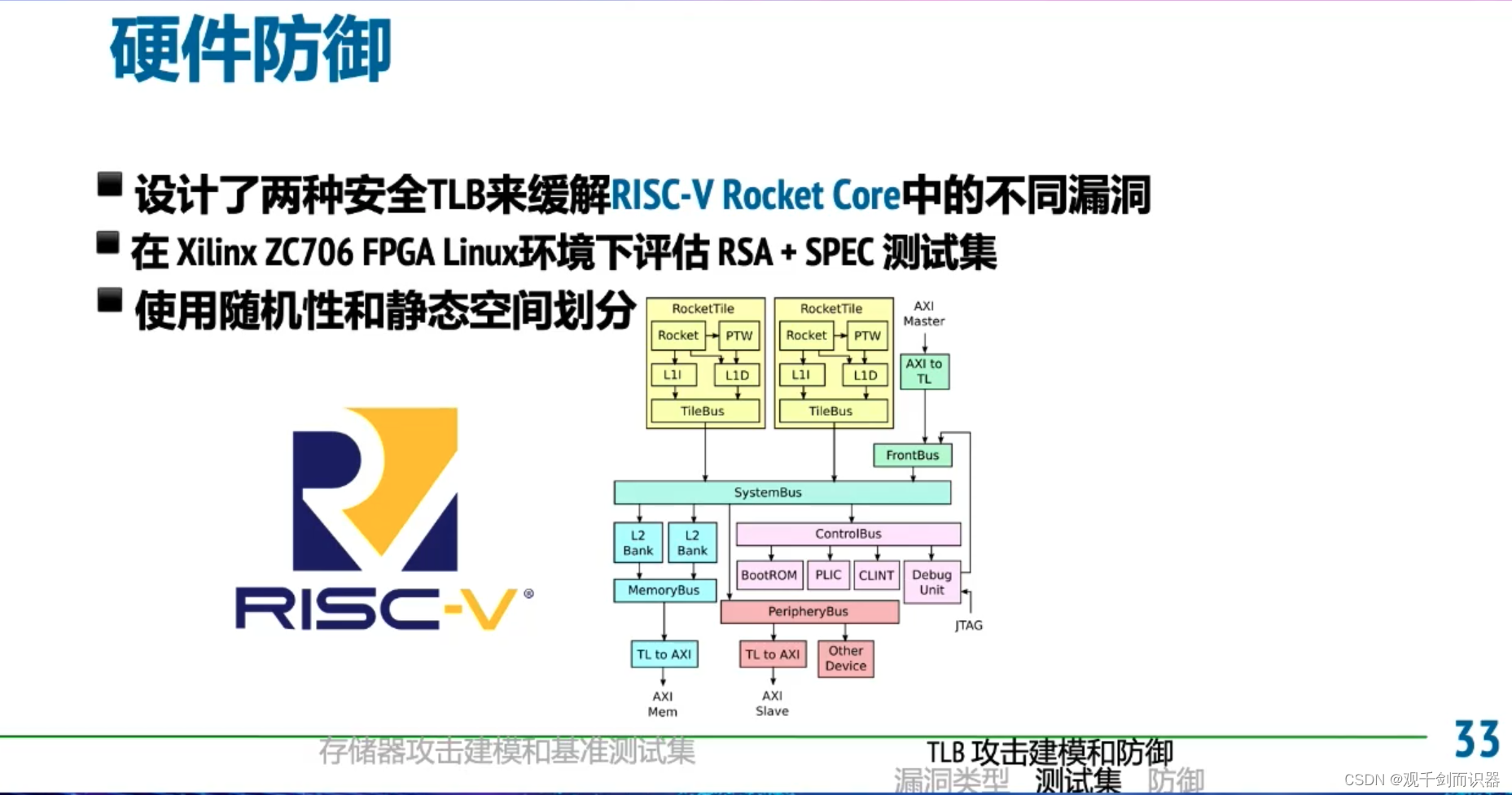

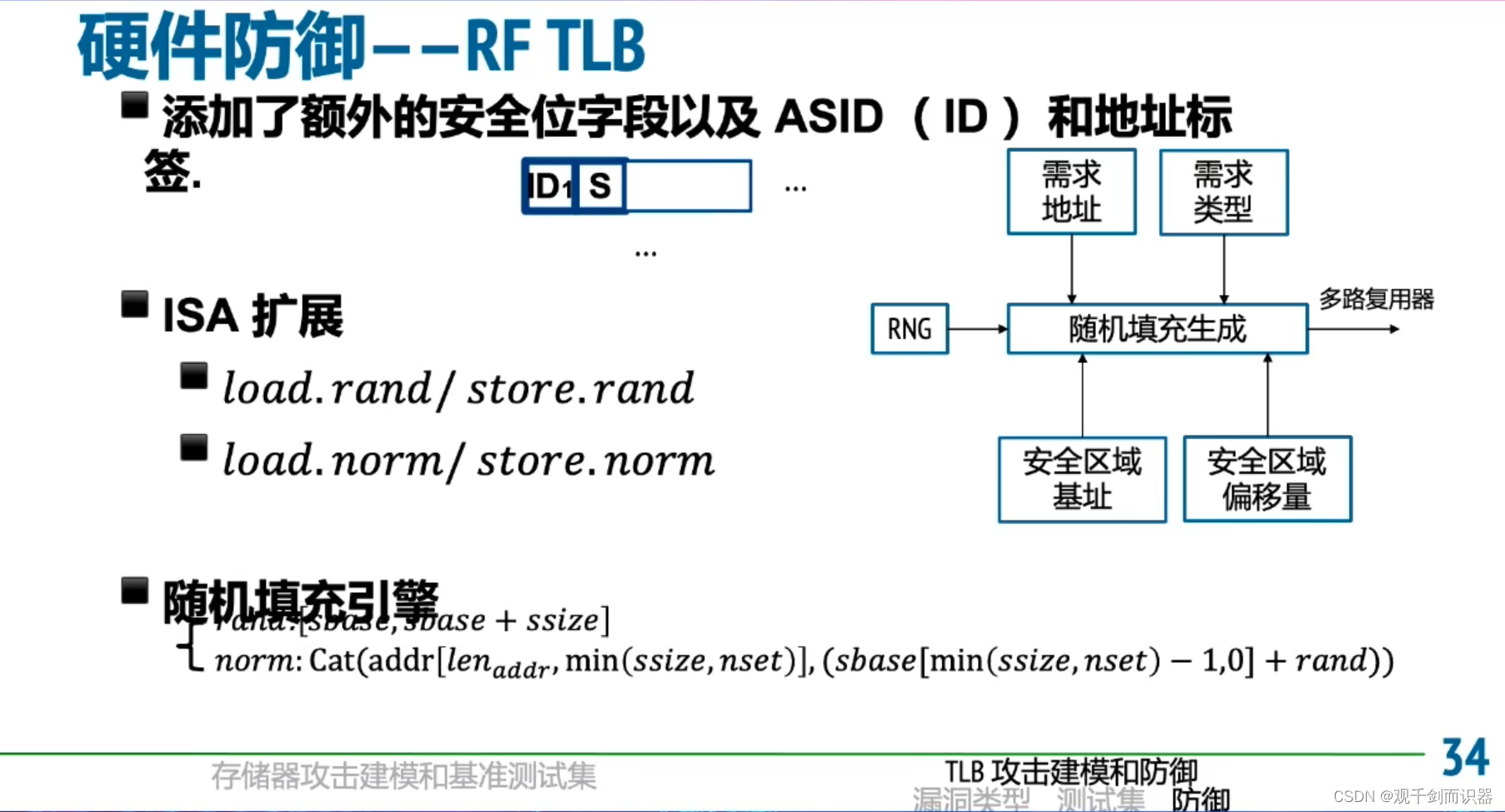

处理器微处理架构安全,邓舒文,清华大学电子工程系

b站视频传送门:处理器微处理架构安全,邓舒文,清华大学电子工程系,助理教授