项目描述

- 上位机将截图数据通过 XDMA 写入到 FPGA 侧的 DDR 内存区域 1 中

- 通过 axi_lite 接口给 axi_read_start 信号,通知 AXI_read 模块启动读取数据,然后通过 GTP TX 模块发送出去。

- 经过光纤回环,GTP RX 端接收到数据,送给 AXI_WRITE 模块,然后写入到 FPGA的内存的区域 2 中。

- 写完成后通过 AXI write end 的中断信号通知上位机读取区域 2 的数据。

结构框图

其中pc上位机与fpga之间通过pcie接口相连,axi_read模块读出的数据通过aurora8b10b模块实现并转串输出到光纤接口。

本次项目是在XDMA框架下的桌面采集和PCIE传输项目以及aurora8b10b ip的使用(framing接口下的数据回环测试)两个项目的基础上进行的。

本章内容:搭建适合pcie和sfp共用一个QUAD的框架

一、common与channel设置

本章重点:实现在a7板子上使用一个QUAD实现两种高速接口(pcie、sfp)框架的搭建。

需要先了解:

高速收发器的原理

分析:

本次项目中XDMA和aurora 都需要用到高速接口:

分别是pcie(xmda使用)和sfp(aurora使用),且涉及到两个refclk,这里需要注意一下refclk如何通过QPLL路由到不同的channel。

本项目中两个PCIE通道使用QPLL0(100MHZ),一个SFP通道使用QPLL1(125MHZ)。

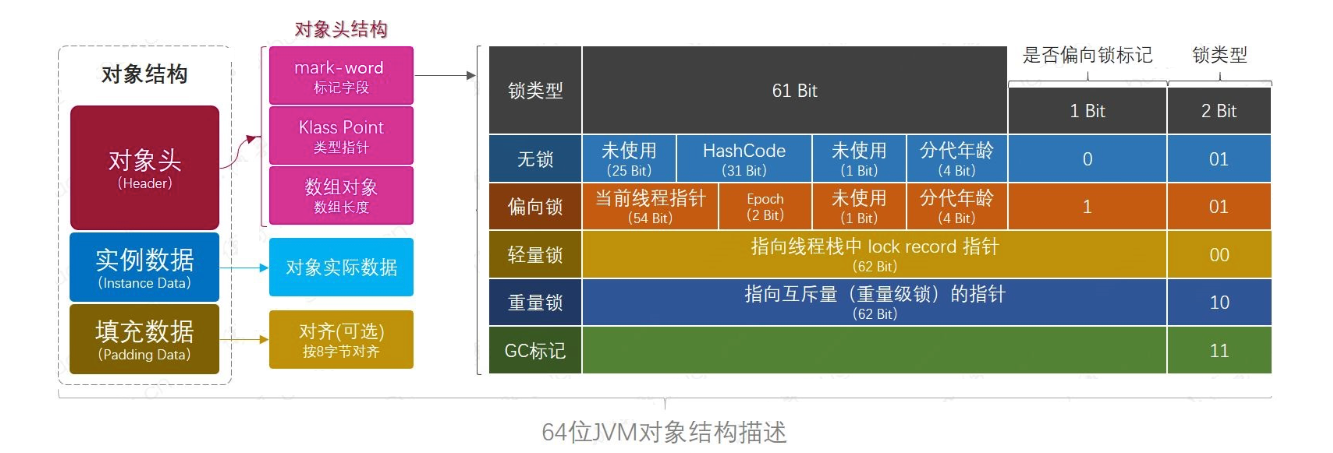

从图中可以看到:高速收发器的时钟从refclk路由到rx or tx接口需要经过两个部分的配置:

1.common 中: QPLL选择哪个refclk,以及提供给哪类高速接口使用(pcie or sfp)

2.channel 中:选择对应QPLL的哪一路(左端 or 右端)

所以重点在于这两个部分如何配置。

1.common的配置

1.1共享xdma的common逻辑:

将xdma中的common资源共享出来(如果不共享的话,common资源就只存在于xdma的ip核中,但是aurora的ip核也需要使用common资源,一个commom需要一个quad,a7开发板只有一个quad,因此如果遇到多个地方需要common资源时,需要将common从某个单独的ip中共享出来,共同使用。)

后续设计需要使用官方例程,在官方例程上改参数。

- 生成xdma ip 的example design,打开工程文件,找到imports文件夹,将下图中的四个文件复制到一个新的文件夹中(新建一个gtp_common文件夹放进去),后续修完成后,作为自定义的ip使用。

四个文件的关系如下,其中gt_common为顶层

1.2修改xdma的qpll_wrapper文件

分析:

- xdma共享出来的common需要给两个ip提供时钟(xdma、aurora)。

- 而一个Qpll只能驱动一种类型的高速接口(例如QPLL0驱动pcie的高速接口,就不能驱动sfp光纤的高速接口了),因此common需要输出QPLL0和QPLL1两路时钟,分别驱动两种不同高速接口。

- 两个高速接口依赖的refclk可以由电路原理图得知(refclk0驱动sfp,refclk1驱动pcie)。

- 每个ip使用common时,默认情况下首先使用的是QPLL0,所以原项目的xdma模块中是使用QPLLO驱动pcie的channel,而aurora8b10b模块(官方例程)也默认使用PLL0。(因为xdma中QPLL0驱动了pcie的两个channel,而aurora8b10b中QPLL0驱动了sfp的一个通道,因此直接在xdma的文件中更改QPLL1的设置更方便)

共享出来的common接口情况如下,需要拓展接口:

查看xdma的qpll_wrapper文件初始情况:

Q:如何修改xdma的qpll_wrapper文件,QPLL1参数设置的依据是什么?

A:aurora8b10b的commom_wrapper文件(相当于apll_wrapper文件)

对比xdma的qpll_wrapper文件前后修改情况:

其中PLL0REFCLKSEL 和 PLL1REFCLKSEL的参数设置依据:

1.3修改xdma的gt_common(顶层)文件

1.4 gt_common ip的封装示意图,参考官方例程完成与XDMA模块和AURORA模块的连线。

2. channel的配置

xdma的两个pcie的channel已经默认与QPLL0相连了,因此只需要配置aurora的channel,使其连接QPLL1即可。

由手册可知:

当RXSYSCLKSEL和TXSYSCLKSEL都为1时,由PLL1OUTCLK 和 PLL1OUTREFCLK驱动channel。

具体操作如下:

打开aurora的ip,找到gt文件:

修改参数如下:

总结两个高速接口的ref时钟配置情况: