Vector相较于SIMD的优势

这两种实现方案,都是为了实现数据级并行性(存在大量的数据可供程序同时计算);

SIMD(Single Instruction Multiple Data)

SIMD是将数据宽度和操作类型,都放在了指令中;

- SIMD技术最初通过将64位寄存器的数据拆分成多个8位、16位、32位的形式来实现byte、half word、word类型数据的并行计算;

- 在后续,为了进一步增加计算的并行度,SIMD技术开始通过增加寄存器位宽来满足应用对算力的需求;

- 因此,扩展SIMD的寄存器,意味着要同时扩展SIMD的指令集;

- 而这种改变SIMD寄存器的宽度和SIMD指令数量的翻倍,都让ISA走上了复杂的道路;

- 这一后果由处理器设计者、编译器编写者和汇编语言程序员共同承担;

VECTOR

RISC-V Vector 拥有其他架构矢量指令没有的两大优点:硬件维护方便与指令长度可变。

- 向量寄存器的大小由实现决定,而不是像SIMD中那样嵌入操作码中;

- 它将向量的长度和每个时钟周期可以进行的最大操作数分离,是向量体系结构的关键所在:

- 向量微架构可以灵活地设计数据并行硬件而不会影响到程序员,程序员可以不用重写代码就享受到长向量带来的好处。

- 对于某一个矢量操作,即使硬件中的寄存器长度变化,代码也不需要作更改;

- 相反的,在同一硬件中,即使指令长度作相应改变,代码也不需要更改。

- 这意味着任何 RISC-V 兼容处理器编写的代码在其余 RISC-V 处理器上依然适用,这对于用户来说,简易性直线上升。

- 上述的优点也就意味着,向量架构比SIMD 架构拥有更少的指令数量;

Vector register

register

- v0~v31, 32个vector寄存器,每个寄存器的宽度都是由VLEN决定的;

- Vector Context Status in mstatus/sstatus

- 放在mstatus[10:9], 用来指示相关状态;

- 当VS==off时,执行任何的vector指令,或者访问vector的CSR,都会产生illegal-inst excp;

- 当VS set to initial or clean时,只要执行vector指令,或者访问vector CSR, 会将VS状态改为dirty; 当然,具体的实现可以随意更改该状态,而不必等到有vector访问;

- 如果VS是dirty的,则mstatus.SD要设置成1;

- Vector Context Status in vsstatus

- When the hypervisor extension is present;

- Vector type register, vtype

- read-only XLEN-wide vector type CSR;

- can only be updated by vset{i}vl{i} instructions.

- vlmul(vector length multipler), vector register grouping, 指的是多个vector的寄存器,可以被分成多个group, 这样一个vector instr, 就可以在多个vector寄存器上处理;

- LMUL is set by the signed vlmul field in vtype (i.e., LMUL = 2**vlmul[2:0]),表示需要多少个寄存器参与运算;

- the requirement is to support LMUL ≥ SEW_MIN/ELEN

- SEW, selected element width, 参考下一节的描述;

- ELEN, 最大的SEW;

- 所以,从上面的公式来看,LMUL可以是整数,也可以是分数;

- 当LMUL< SEW_MIN/ELEN时,需要设置vill,表示指令异常;

- vsew,就是对应的element宽度;

- 例如,假如一个寄存器是128bits, 那么:

- 默认情况下,一个vector的寄存器,会被认为分成了VLEN/SEW elements

- vta & vma;

- vta, vector tail agnostic;

- vma, vector mask agnostic;

- 这两个bit用来控制vector instruction的tail element和inactive element的行为;

- undisturbed: 不受干扰; agnostic: 不可预知;

- 当一个element被标记成undisturbed时,则vector register group中响应的element将会保留原来的值不变;

- 当一个element被标记成agnostic时,destination element既可以保留原来的值,也可以overwrite by 1;

- 为什么需要agnostic?

-

在有些处理器中,会采用寄存器重命名的技术,比如超标量流水线处理器,在undisturbed策略下,必须从旧的物理目标向量寄存器中读取元素值,才能复制到新的物理目标寄存器中;也可以说,在新的物理寄存器进行重命名时,需要根据重命名映射表,查到原有的映射关系,然后把其中的元素值读出来,写到重命名后的对应元素。这对于不需要这些非活跃元素和尾部元素值的之后的运算既降低了性能也增加了功耗。因此undisturbed策略就显得很不可观,此时按照agnostic策略进行运算比较好。

-

-

vill;

-

此bit用来当vset指令想要往vtype中写入不支持的值时,vill字段置1;

-

当vill bit置位时,任何想要用vtype来做vector operation的指令,都会产生一个illegal-instruction excption;

-

当vill有效时,vtype其他字段全部清零;

-

-

vector length register

-

向量长度寄存器,只读,规定了一条向量指令需要操作的元素个数,为无符号数。

-

该寄存器只被vsetvli、vsetvl指令和fault-only-first向量加载(load)指令变量更改。

-

当vl=0或者vstart≥vl时,目的寄存器的所有元素都不被更改,也可以说指令不执行。

-

vl的宽度由最小元素宽度(SEW)和最大向量长度决定,其中SEW规定了指令执行元素的宽度,最小为8,最大向量长度为组成的最长的向量寄存器组,由VLMUL决定,最大为8。所以最多元素个数为

-

-

vlenb, vector byte length;

- vlenb为只读,恒为VLEN/8,表示以字节为单位的向量寄存器长度;

- 当有些指令需要以字节为单位使用向量寄存器时,用于减少额外的计算过程。

- vstart, vector start index;

- RW, 用来指定vector指令中的第一个元素的index;

- 通常,vstart只通过在vector指令执行过程中产生的trap中被写入,记录synchronous exception或者asynchronous interrupt时,当前已经执行到的element index, 恢复的时候可以正常恢复;

- 所有vector instruction保证目的寄存器vstart之前的元素不被更改,指令执行结束,vstart寄存器置零。

- vxrm, Vector Fixed-Point Rounding Mode Register;

- RW, 向量定点舍入模式;

-

vxrm共有四种模式:

a)round-to-nearest-up(rnu):就近舍入,当为中间值时,向上舍入(四舍五入)。

b)round-to-nearest-even(rne):就近舍入,当为中间值时,向偶数舍入。

c)round-down(rdn):向下舍入,直接取移位后的值。

d)round-to-odd(rod):向奇数舍入。 -

设源操作数为vs1,有d位要被截位,则舍入后的值为(vs1>>d)+r,其中r为不同舍入模式下的差值:

-

-

vxsat, Vector Fixed-Point Saturation Flag;

-

该bit指示是否有定点指令必须将输出值饱和以适应目标格式。位vxsat[XLEN-1:1]应写为零。vxsat位在vcsr中有镜像。

-

-

vcsr, Vector Control and Status Register

-

The vxrm and vxsat separate CSRs can also be accessed via elds in the vector control and status CSR, vcsr.

-

-

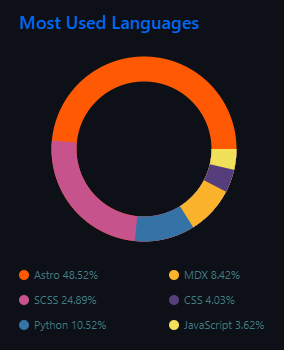

Vector中element的几个概念

- Prestart, Active, Inactive, Body, and Tail, 这几个都是针对element来说的;

- 假设VLEN=32,LMUL=2,SEW=16,那么这条指令需要操作4个元素。如果vstart设置为1,vl设置为2,那这些概念对应的分别是如图所示:

![[NeurIPS 2024] Self-Refine: Iterative Refinement with Self-Feedback](https://i-blog.csdnimg.cn/direct/f82aaf029cb840f49bd520e185499194.png#pic_center)