软件版本:VIVADO2021.1

操作系统:WIN10 64bit

硬件平台:适用 XILINX A7/K7/Z7/ZU/KU 系列 FPGA

实验平台:米联客-MLK-H3-CZ08-7100开发板

板卡获取平台:https://milianke.tmall.com/

登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑!

目录

1概述

2硬件电路分析

3图形化的Block Design

4测试结果

1概述

由于VIVADO图形化的编程方式中大量应用,所以我们大部分时候都需要对IP进行图形化的封装,前面两节课实验,我们已经完成了简单IP的封装。本实验利用前面图形化IP设计基于图形化的FPGA设计方案,实现“RGB转HDMI显示输出”这节课的内容

2硬件电路分析

硬件接口和子卡模块请阅读“附录 1”

配套工程的 FPGA PIN 脚定义路径为 soc_prj/uisrc/04_pin/ fpga_pin.xdc。

3图形化的Block Design

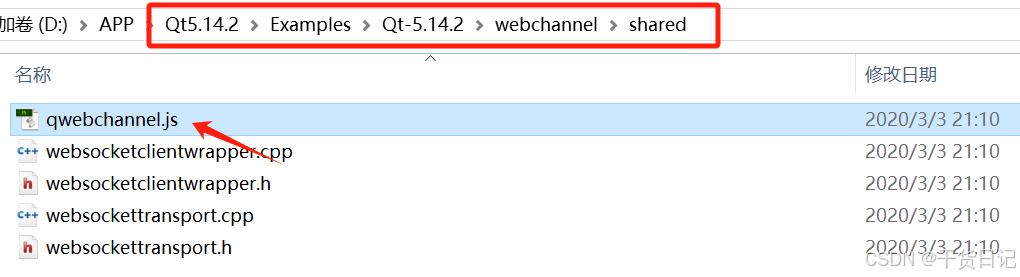

新建FPGA工程,并且添加IP的路径,添加IP路径的方法和前面的一样,添加成功后会有提示识别到的IP

创建一个BlockDesign

命名为system,这个名字也可以自己取,默认情况下米联客的blockDesign都为system

BlockDesign其实就是一个容器,这个容器里面我们放入IP并且通过把IP接口通过连线的方式相互关联,这样图形化的设计效率要高一些,也更加直观。

单击”+”号添加我们需要用到的IP

只要输出关键词就能找到相关的IP,双击IP就能添加进入BlockDesign

先把我们需要用到的IP都添加进来如下图

首先设clk_wiz_0的时钟设置,输入时钟频率可以根据实际板子的输入时钟频率而设定

设置HDMI输出IP需要的时钟

VTC的设置,默认就是720P的时序参数

HDMI输出IP的设置,选择artix7,实际上对于7代的FPGA都可以选择artix7,而对于ultrascal 选中ULTRASCAL或者ultrascal+的FPGA选择ULTRASCAL_PLUS

使用鼠标连线,最终结果如下,这张图就代表了FPGA的程序设计,本质还是我们之前写的FPGA代码

对于一些信号命名如果不符合我们习惯,可以单击信号,修改命名

当你需要把IO端口引出到外部,可以右击IP的端口,选中make External

单击已经引出的信号,还可以修改名字

如果有连接错误的线,还可以右击端口延长的部分,选择Disconnect Pin断开这个端口的连接

更多控制方法可以右击鼠标,根据弹出的菜单选择命令。具体的操作过程也可以通过视频教程学习。

右击system 选择Create HDL Wrapper,这个过程就是产生一个FPGA的顶层文件,调用system这个BlockDesign

以下是自动产生的文件

这时候也可以展开system看下源码(注意,这个源码是复制了我们03_ip路径下的源码,一般我们修改了ip源码,VIVADO会提示更新IP,重新复制03_ip路径下的原来过来)

添加FPGA约束文件,编译并且测试

4测试结果

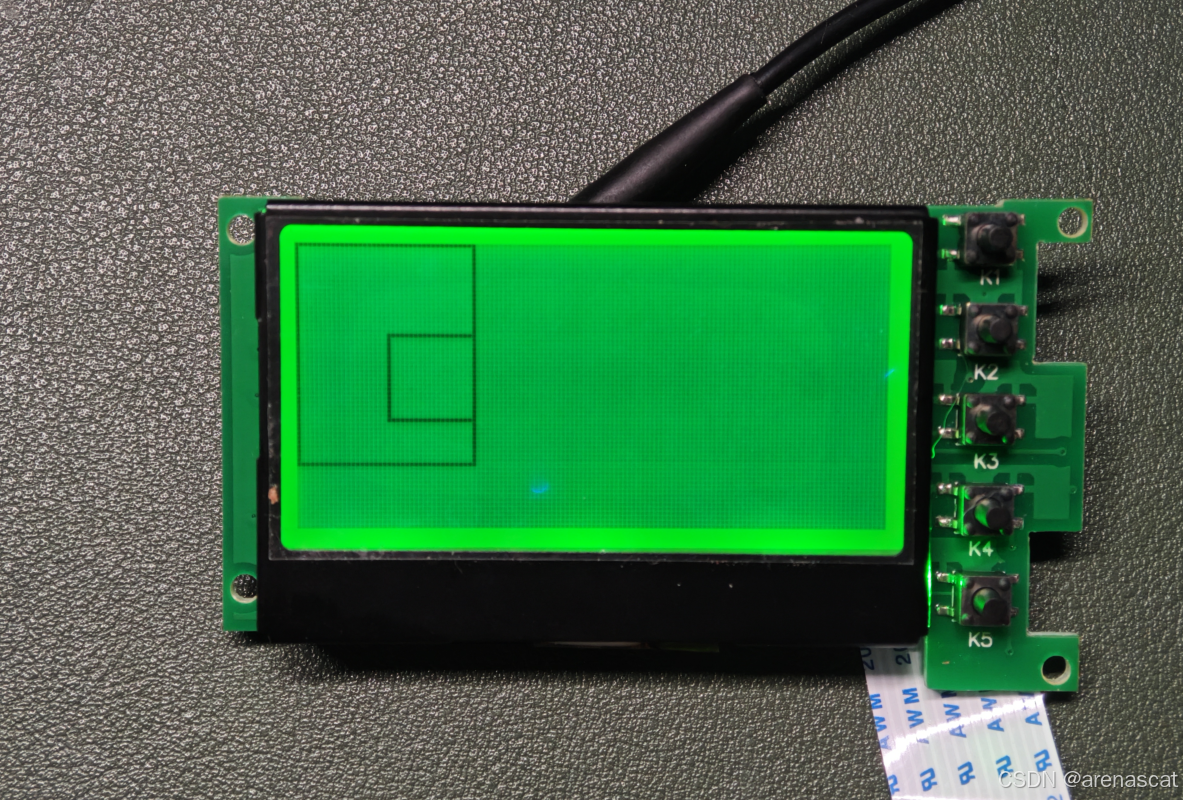

测试结果和前面的文章测试结果一致,参照第25课。