目录

目录

一、新建BD文档,添加ZYNQ处理器

1.BD文档:

2.在Vivado中,BD文件的生成过程通常包括以下步骤:

1)什么是Tcl Console:

3.PL部分是FPGA可编程逻辑部分,它提供了丰富的IO资源,可以用于实现各种硬件接口和功能。

1)什么是XGPIO的IP核

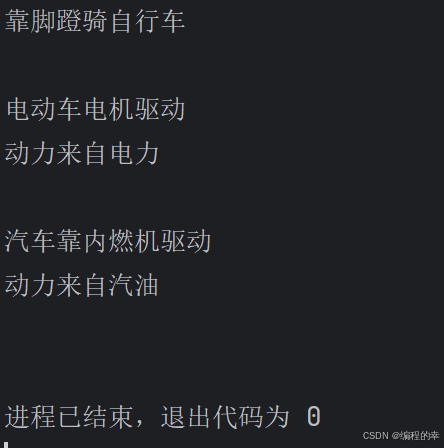

使用我们的PL的IO,通过XGPIO的IP核,来驱动我们Oled模块

使用zynq的PL 的IO模拟(IIC,SPI)时序,驱动OLED,IO方式是最基础的

一、新建BD文档,添加ZYNQ处理器

1.BD文档:

BD文档,全称Bill of Materials,是材料清单的意思,在FPGA设计中,它通常指的是Block Design文件。在Vivado设计工具中,Block Design文件(以.bd为后缀)是用来描述硬件系统结构和功能的文件格式。它包含了硬件系统中使用的各种IP核(Intellectual Property Cores)、连接关系以及配置参数等信息。

对于FPGA设计,特别是使用Xilinx的Vivado工具时,BD文档通常包含以下信息:

1. **IP核(IP Cores)**:这些是预设计的、可重用的硬件模块,如处理器、内存控制器、输入/输出接口等。在BD文件中,可以通过图形化界面将这些IP核拖放并连接起来。

2. **连接关系(Connections)**:描述了不同IP核之间的数据流和控制流连接。这些连接可以是简单的线连接,也可以是复杂的总线结构。

3. **配置参数(Configuration Parameters)**:每个IP核都可以有一系列的配置参数,这些参数定义了IP核的行为和功能。

4. **端口定义(Port Definitions)**:BD文件定义了系统顶层的输入输出端口,包括它们的名称、位宽、方向等。

5. **约束文件(Constraint Files)**:如.xdc文件,它包含了FPGA引脚的物理约束信息,用于指导布局和布线过程。

6. **设计源文件(Design Source Files)**:可能包括Verilog或VHDL文件,这些文件定义了自定义逻辑的设计。

7. **层次结构(Hierarchy)**:如果设计是层次化的,BD文件可以包含对子系统或子模块的引用。

8. **验证和仿真信息**:可能包括用于设计验证和仿真的测试平台和激励。

9. **版本控制信息**:在团队协作和版本控制的环境中,BD文件可能包含版本信息,以确保设计的一致性和可追溯性。

2.在Vivado中,BD文件的生成过程通常包括以下步骤:

- 创建新的Block Design。

- 添加和配置IP核。

- 连接模块。

- 配置和优化设计。

- 验证设计。

- 生成HDL Wrapper,这是将Block Design封装并生成相应的HDL代码的过程。

BD文件是FPGA设计中非常重要的组成部分,它不仅帮助设计者以图形化的方式快速搭建和验证复杂的数字电路设计,而且也是实现设计复用和模块化的关键。

点击 Creat Block Design->

1)什么是Tcl Console:

Tcl Console 是一个集成在Xilinx Vivado设计工具中的交互式命令行界面,它允许用户直接输入和执行Tcl(Tool Command Language)脚本命令。Tcl是一种脚本语言,它在EDA(Electronic Design Automation)工具中得到了广泛的应用,特别是在Vivado中,Tcl脚本可用于自动化设计流程、执行批处理操作以及自定义和扩展Vivado的功能。

在Vivado中,Tcl Console的主要功能包括但不限于以下几点:

1. **执行Tcl命令**:用户可以在Tcl Console中直接输入Tcl命令,如创建项目、添加文件、配置IP核等,来控制Vivado的各个方面。

2. **自动化设计流程**:通过编写和运行Tcl脚本,可以自动化复杂的设计任务,减少重复劳动,提高效率。

3. **调试和问题解决**:Tcl Console可以快速定位设计中的问题,减少设计迭代周期,帮助用户进行调试和问题解决。

4. **访问和操作项目文件**:用户可以使用Tcl命令来访问和操作项目文件,如读取、写入、修改文件等。

5. **控制Vivado的GUI元素**:通过Tcl脚本,用户可以控制Vivado的GUI元素,如打开或关闭视图、设置参数等。

使用Tcl Console的方法也很简单:

- 在Vivado中打开Tcl Console视图,通常在“Window”菜单下的“Show View”中选择“Tcl Console”。

- 在Tcl Console中输入Tcl命令,然后按回车键执行。

- 命令执行的结果会直接在Tcl Console中显示。

Tcl Console是Vivado中一个非常强大的工具,掌握它能够显著提升使用Vivado的效率和灵活性。

3.PL部分是FPGA可编程逻辑部分,它提供了丰富的IO资源,可以用于实现各种硬件接口和功能。

在ZYNQ开发板中使用PL的IO通常指的是与可编程逻辑部分(Programmable Logic,简称PL)的输入输出接口进行交互

使用PL的IO意味着你可以将PL部分的IO引脚配置为各种类型的接口,如GPIO、SPI、UART、I2C、Ethernet等,以满足你的应用需求。这些IO引脚可以用于与外部设备进行通信,如传感器、显示器、网络设备等。通过Vivado设计工具,你可以定义这些IO引脚的功能和属性,包括它们的电气标准(如3.3V或1.8V)、速率、协议等。

例如,如果你需要一个GPIO来控制一个LED灯,你可以在PL中定义一个IO引脚作为GPIO,并在FPGA逻辑中编写相应的代码来控制这个引脚的电平。同样,如果你需要与一个SPI设备通信,你可以在PL中定义一组IO引脚作为SPI接口,并实现SPI协议来与该设备进行数据交换。

在实际应用中,使用PL的IO可以提供高度的灵活性和可定制性,使得ZYNQ开发板能够适应各种不同的应用场景。通过编程PL的IO,开发者可以充分发挥FPGA的并行处理能力和高速性能,同时利用ARM处理器的控制和管理优势,实现复杂的系统设计和功能。

1)什么是XGPIO的IP核

XGPIO IP核是Xilinx提供的一种软核(Soft IP),它设计用于Xilinx FPGAs,提供AXI-Lite Master接口转GPIO的功能。AXI GPIO IP核允许开发者在FPGA的可编程逻辑(PL)部分创建通用输入/输出接口,这些接口可以通过AXI总线与处理器系统(PS)侧进行通信。这种设计允许PS侧通过AXI接口控制PL侧的IO引脚,从而扩展了PS侧可用的GPIO数量,解决了PS侧IO口不够用的问题。

AXI GPIO IP核的主要特点包括:

1. 通过AXI总线与PS侧互联,实现GPIO功能。

2. 支持单通道或双通道操作,每个通道的位宽可以单独设置。

3. 可以动态配置为输入或输出接口,通过三态缓冲器控制。

4. 支持中断功能,允许PL侧对PS侧产生中断信号。

5. 位宽可配置,根据需要可以设置为1到32位。

在应用中,AXI GPIO IP核可以通过Xilinx的Vivado设计工具进行配置和使用。配置时,可以在IP核参数中设置GPIO的方向、默认值、三态行为等。在软件开发中,可以使用Xilinx提供的API进行GPIO的读写操作,如`XGpio_Initialize`、`XGpio_SetDataDirection`、`XGpio_DiscreteRead`和`XGpio_DiscreteWrite`等函数。

AXI GPIO IP核的使用场景包括:

- 控制LED灯、按键、触摸屏等外部设备。

- 实现简单的数据采集和控制任务。

- 作为更复杂系统设计的构建块。

总的来说,AXI GPIO IP核为ZYNQ SoC的PS和PL之间提供了一种灵活的通信方式,使得开发者可以更加方便地控制FPGA的IO引脚,实现各种硬件接口功能。