通过前文介绍了RGMII接口时序我们可以知道,RGMII接口是在时钟信号的上升沿和下降沿均进行数据的传输,而FPGA则在时钟的单沿传输数据,因此我们需要编写代码将RGMII接口转换为GMII接口。

由于前面的介绍我们知道RTL8211默认工作在延时状态,并且可以通过控制上拉或者下拉来改变延时与否,如下图所示。

发送的时序图如下所示:

可以看到当PHY芯片工作在延时模式的时候,会将发送端的时钟进行2ns的延时作为接收端的数据接收时钟与控制时钟,这也是最常用的工作模式。RTL8211FD默认就是工作在延时状态,因此不再需要MDIO接口对寄存器进行配置。

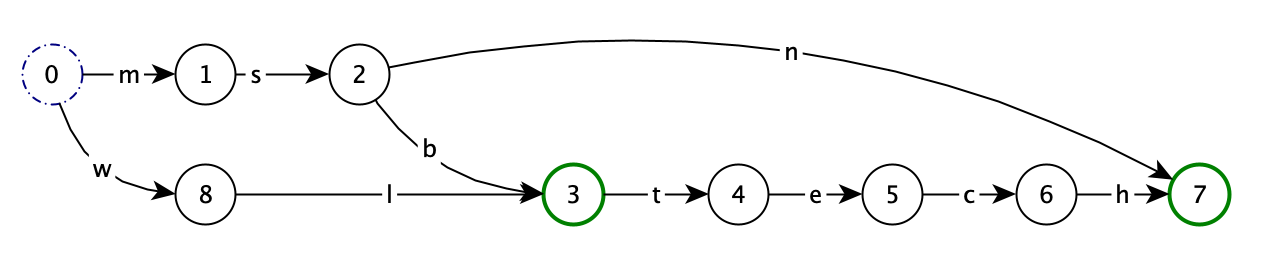

实现RGMII与GMII需要用到两个原语分别为ODDR和IDDR,接下来我们先简单了解一下两个原语的用法。

- LOGIC

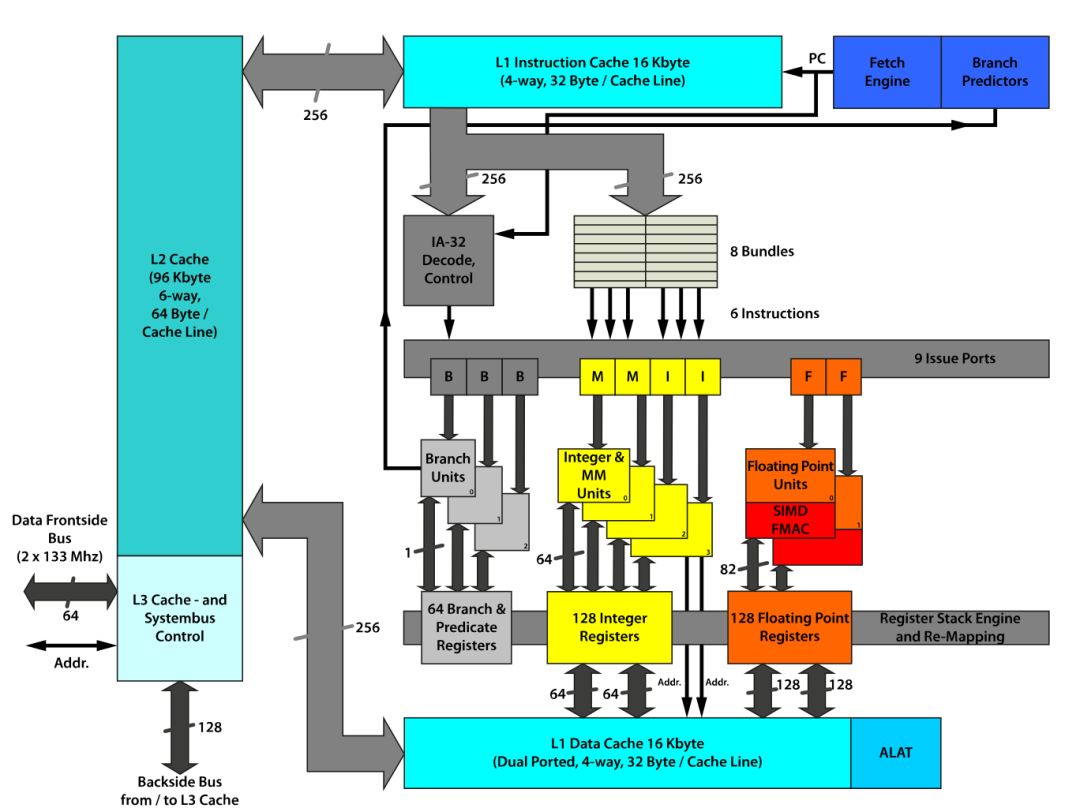

ODDR位于OLOGIC中,可以把单沿传输的数据转换为双沿传输的数据, 在讲解ODDR功能之前,需要先了解OLOGIC的结构及功能。OLOGIC块位于IOB的内侧,FPGA内部信号想要输出到管脚,都必须经过OLOGIC。OLOGIC资源的类型为OLOGICE2(HP I/O Bank)和OLOGICE3(HR I/O Bank),两者在功能和结构上是相同的,所以本文统称为OLOGIC,其结构如下图所示。

如果输出的信号不使用OLOGIC中的ODDR功能,那么此时信号从上图中红线路径进行传输,从组合逻辑电路输出到IOB模块。如果要使用OLOGIC模块中的D触发器功能,那么信号从D1进入OLOGIC模块,沿绿色信号线进行传输。如果要使用OLOGIC的ODDR功能,把单沿传输的信号转换为双沿传输的信号,此时需要两个输入信号D1、D2沿蓝色路径进行传输。

ILOGICE位于IOB旁边,ILOGICE块包含同步元件,用于在数据通过IOB进入FPGA时捕获数据。7系列芯片中ILOGICE可能是ILOGICE2(HP I/O bank)或ILOGICE3(HR I/O bank)。

当需要使用IDDR这些转换功能时,通过绿色的信号传输到下面器件的输入端D,这个器件可以配置为锁存器(latch)、触发器(FF)、双沿转单沿器件(DDR),而CE1是时钟使能信号,高电平有效,不连接时默认为高电平。

当不使用IDDR功能时,在使用IDDR原语后,只需要添加(IOB == “TRUE”)原语,就可以使用ILOGICE中的触发器(FF)的功能。 这个触发器相比FPGA内部触发器更靠近FPGA管脚,使得建立时间余量更大,更有利于时序。

Q1和Q2是输出端口,S/R是复位、置位端口,在调用原语是可以对同步、异步触发进行设置。此框图中S/R的是一根线,但IDDR的原语将S和R分开为两个端口,使用时不能让S、R同时有效。

1.ODDR

ODDR的框图如下所示:

| 端口名 | 含义 |

| C | 时钟输入信号。 |

| CE | 时钟使能信号,高电平有效。 |

| D1、D2 | ODDR输入信号。 |

| S/R | 置位/复位引脚,高电平有效。 |

| Q | ODDR输出信号。 |

ODDR原语的参数如下图所示:

| 参数名 | 含义 | 取值 |

| DDR_CLK_EDGE | ODDR工作模式 | OPPOSITE_EDGE (默认), SAME_EDGE |

| INIT | 设置Q端口的初始值 | 0(默认),1 |

| SRTYPE | 设置复位/置位相对于时钟的类型 | ASYNC, SYNC(默认) |

ODDR两种工作模式的时序图前面都已经提到过这里就不再赘述。

ODDR原语例化模版如下:

ODDR #(

.DDR_CLK_EDGE ("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT (1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE ("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q (Q), // 1-bit DDR output

.C (C), // 1-bit clock input

.CE (CE), // 1-bit clock enable input

.D1 (D1), // 1-bit data input (positive edge)

.D2 (D2), // 1-bit data input (negative edge)

.R (R ), // 1-bit reset

.S (S ) // 1-bit set

);

其实该原语的使用与理解都不难,只需要记住它的功能是将TXC同一个时钟周期内的两个SDR信号分别通过上升沿和下降沿输出为DDR信号。

2.IDDR

IDDR其实可以看做ODDR的逆过程,FPGA在接收DDR信号时可以利用IDDR原语将其转化为SDR信号,以便FPGA内部进行处理。

IDDR框图如下所示:

| 端口名 | 含义 |

| Q1、Q2 | IDDR输出寄存器 |

| C | 时钟输入引脚 |

| CE | 必须为高电平才能将新数据加载到DDR触发器中,低电平时,时钟转换被忽略,新数据不会加载到DDR触发器中。 |

| D | IDDR寄存器从IOB输入 |

| S/R | 同步/异步设置/复位引脚,高电平有效。 |

模版如下:

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

3.GMII转RGMII

具体实现代码如下图所示

`timescale 1ns / 1psmodule gmii2rgmii(input gmii_txclk , //GMII发送时钟input gmii_tx_en , //GMII发送使能input gmii_tx_er , //GMII发送错误input [7:0] gmii_tx_data , //GMII发送数据output rgmii_txclk , //RGMII发送时钟output rgmii_tx_ctl , //RGMII发送控制output [3:0] rgmii_tx_data //RGMII发送数据

);//时钟转换ODDR #(.DDR_CLK_EDGE ("SAME_EDGE" ), // "OPPOSITE_EDGE" or "SAME_EDGE" .INIT (1'b0 ), // Initial value of Q: 1'b0 or 1'b1.SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC" ) ODDR_inst_2 (.Q (rgmii_txclk ), // 1-bit DDR output.C (gmii_txclk ), // 1-bit clock input.CE (1'b1 ), // 1-bit clock enable input.D1 (1'b1 ), // 1-bit data input (positive edge).D2 (1'b0 ), // 1-bit data input (negative edge).R (1'b0 ), // 1-bit reset.S (1'b0 ) // 1-bit set);//数据转换genvar i;generatefor (i=0; i < 4; i=i+1)begin: rgmii_txd_oODDR #(.DDR_CLK_EDGE ("SAME_EDGE" ), // "OPPOSITE_EDGE" or "SAME_EDGE" .INIT (1'b0 ), // Initial value of Q: 1'b0 or 1'b1.SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC" ) ODDR_inst_0 (.Q (rgmii_tx_data[i] ), // 1-bit DDR output.C (gmii_txclk ), // 1-bit clock input.CE (1'b1 ), // 1-bit clock enable input.D1 (gmii_tx_data[i] ), // 1-bit data input (positive edge).D2 (gmii_tx_data[i+4]), // 1-bit data input (negative edge).R (1'b0 ), // 1-bit reset.S (1'b0 ) // 1-bit set);endendgenerate//控制信号转换ODDR #(.DDR_CLK_EDGE ("SAME_EDGE" ), // "OPPOSITE_EDGE" or "SAME_EDGE" .INIT (1'b0 ), // Initial value of Q: 1'b0 or 1'b1.SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC" ) ODDR_inst_1 (.Q (rgmii_tx_ctl ), // 1-bit DDR output.C (gmii_txclk ), // 1-bit clock input.CE (1'b1 ), // 1-bit clock enable input.D1 (gmii_tx_en ), // 1-bit data input (positive edge).D2 (gmii_tx_er^gmii_tx_en), // 1-bit data input (negative edge).R (1'b0 ), // 1-bit reset.S (1'b0 ) // 1-bit set);endmodule

`timescale 1ns / 1psmodule gmii2rgmii_tb();reg gmii_txclk ;reg gmii_tx_en ;reg gmii_tx_er ;reg [7:0] gmii_tx_data ;wire rgmii_txclk ;wire rgmii_tx_ctl ;wire [3:0] rgmii_tx_data ;initial gmii_txclk = 1'b1;always#5 gmii_txclk = ~gmii_txclk;initial begingmii_tx_en = 0;gmii_tx_er = 0;gmii_tx_data = 8'd0;#201;repeat(100)begin@(posedge gmii_txclk)gmii_tx_data = {$random} % 256; gmii_tx_en = 1'b1;gmii_tx_er = 1'b0; end#100;$stop;endgmii2rgmii u_gmii2rgmii(.gmii_txclk (gmii_txclk ),.gmii_tx_en (gmii_tx_en ),.gmii_tx_er (gmii_tx_er ),.gmii_tx_data (gmii_tx_data ),.rgmii_txclk (rgmii_txclk ),.rgmii_tx_ctl (rgmii_tx_ctl ),.rgmii_tx_data (rgmii_tx_data));endmodule仿真结果如下:

-

4.RGMII转GMII

具体代码如下所示:

`timescale 1ns / 1psmodule rgmii2gmii(input rgmii_rxclk , //RGMII接收时钟input rgmii_rx_ctl , //RGMII接收控制input [3:0] rgmii_rx_data , //RGMII接收数据output gmii_rxclk , //GMII接收时钟output gmii_rx_dv , //GMII接收有效output [7:0] gmii_rx_data //GMII接收数据

);wire [4:0] din ; //控制信号与数据进行拼接wire [9 : 0] gmii_data ; //转换完成后的信号assign din = {rgmii_rx_ctl,rgmii_rx_data} ;assign gmii_rxclk = rgmii_rxclk ;genvar i;generatefor (i=0; i < 5; i=i+1)begin: rgmii_rxd_iIDDR #(.DDR_CLK_EDGE ("SAME_EDGE_PIPELINED" ), // "OPPOSITE_EDGE", "SAME_EDGE" // or "SAME_EDGE_PIPELINED" .INIT_Q1 (1'b0 ), // Initial value of Q1: 1'b0 or 1'b1.INIT_Q2 (1'b0 ), // Initial value of Q2: 1'b0 or 1'b1.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC" ) IDDR_inst (.Q1 (gmii_data[i] ), // 1-bit output for positive edge of clock.Q2 (gmii_data[i+5] ), // 1-bit output for negative edge of clock.C (rgmii_rxclk ), // 1-bit clock input.CE (1'b1 ), // 1-bit clock enable input.D (din[i] ), // 1-bit DDR data input.R (1'b0 ), // 1-bit reset.S (1'b0 ) // 1-bit set);end endgenerateassign gmii_rx_data = {gmii_data[8:5],gmii_data[3:0]};assign gmii_rx_dv = gmii_data[4] & gmii_data[9];//endmodule

`timescale 1ns / 1psmodule rgmii2gmii_tb();reg rgmii_rxclk ;reg rgmii_rx_ctl ;reg [3:0] rgmii_rx_data;reg rgmii_rxclk_r;wire gmii_rxclk ;wire gmii_rx_dv ;wire [7:0] gmii_rx_data ;initial begin#2; rgmii_rxclk = 1'b1;forever #4 rgmii_rxclk = ~rgmii_rxclk;endinitial rgmii_rxclk_r = 1'b1;always#4 rgmii_rxclk_r = ~rgmii_rxclk_r;initial beginrgmii_rx_ctl = 1'b0;rgmii_rx_data = 4'd0;#202;repeat(100)begin@(posedge rgmii_rxclk_r) rgmii_rx_ctl = 1'b1;rgmii_rx_data = {$random} % 16;#4;rgmii_rx_data = {$random} % 16;end#100;$stop;endrgmii2gmii u_rgmii2rgmii(.rgmii_rxclk (rgmii_rxclk ),.rgmii_rx_ctl (rgmii_rx_ctl ),.rgmii_rx_data (rgmii_rx_data),.gmii_rxclk (gmii_rxclk ),.gmii_rx_dv (gmii_rx_dv ),.gmii_rx_data (gmii_rx_data ));endmodule仿真结果如下:

需要注意的是仿真是需要让时钟在上升沿和下降沿对齐数据的中心,不然后出现如下图所示的情况。

参考:xilinx原语详解及仿真之ODDR_oddr原语使用说明-CSDN博客