作者介绍

李婷婷,女,银川科技学院计算机与人工智能学院,2022级计算机与科学技术9班本科生,单片机原理及应用课程第五组。

指导老师:王兴泽

电子邮箱:365349930@qq.com

前言

本篇文章是参考《单片机原理及应用(c语言版)第2版》杨居义·编著教材编写的笔记

由李婷婷、杨兰兰、王倩、马瑞、乔崇浩同学共同完成此篇章,其中马瑞、乔崇浩同学负责80C51的并行输入输出端口结构与操作内容的总结,李婷婷、王倩同学负责80C51的时钟电路与时序内容的总结,杨兰兰同学负责80C51的复位电路和复位后的状态内容总结。

模块二、单片机的结构原理与项目实践

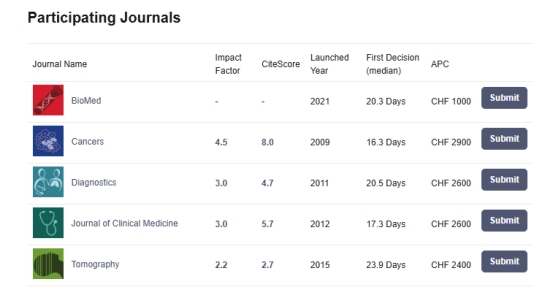

项目7:单片机的端口与项目实践

1、80C51的并行输入输出端口结构与操作

80C51 单片机有4个8位并行I/O端口,分别称为P0、P1、P2和P3,每个端口都各有8条I/O线,每条I/O线都能独立地用作输入或输出。每个口都包含一个锁存器、一个输出驱动器和输入缓冲器。实际上,它们已被归入专用寄存器之列,并且具有字节寻址和位寻址功能。

1)P0口

P0口某一位的结构图如图2-9所示。电路由一个输出锁存器(D触发器)、两个三态输入缓冲器(1和2)、一个转换开关MUX、一个输出驱动电路(T1和T2)、一个与门及一个反向器组成。

图2-9 P0口某位的结构

(1)P0用作通用I/O口。

①当系统不扩展片外ROM和不扩展片外RAM时,P0用作通用I/O口。

②CPU控制电平“0”封锁与门,使上拉场效应管T1处于截止状态。因此,输出驱动级工作在需外接电阻的漏极开路方式。

③同时使MUX开关与下面的触点接通,使锁存器的Q端与T2栅极接通。

(2)P0用作地址/数据总线。当系统需要扩展片外ROM或扩展片外RAM时,P0口就作为地址/数据总线用。

CPU及内部控制信号为1,使转换开关MUX打向上面的触点,使反相器的输出端和T2管栅极接通。若地址/数据线为1,则T1导通,T2截止,P0输出为1;反之,T1截止,T2导通,P0输出为0。当数据从P0输入时,读引脚使三态缓冲器2打开,端口上的数据经缓冲器2送到内部总线。

P0为地址/数据总线使用时是一个真正的双向口。

2)P1口

P1口某一位的结构图如图2-10所示。由图可见,电路由一个输出锁存器(D触发器)、两个三态输入缓冲器(1和2)、一个输出驱动电路(T和上拉电阻)组成。

当P1口作为通用I/O口使用,由于在其输出端接有上拉电阻,故可以直接输出而无须接上拉电阻。当P1口作为输入口时,必须先向锁存器写1,使场效应管T截止。

图2-10 P1口某位的结构

3)P2口

P2口某一位的结构图如图2-11所示。由图可见,电路由一个输出锁存器(D触发器)、两个三态输入缓冲器(1和2)、一个转换开关MUX、一个反向器、一个输出驱动电路(T和上拉电阻)组成。

图2-11 P2口某位的结构

(1)P2口用作通用I/O口。当系统不在片外扩展程序存储器ROM,只扩展256B的片外RAM时,仅用到了地址线的低8位,P2口仍可以作为通用I/O口使用。图2-11中的控制信号C决定转换开关MUX的位置:当C=0时,MUX拨向下方,P0口为通用I/O口。

P2口在作为通用I/O口时,属于准双向口。

(2)P2口用作地址总线。当系统需要在片外扩展程序存储器ROM或扩展RAM的容量超过256B时,单片机内硬件自动使控制信号C=1,MUX开关接向地址线,这时P2.X引脚的状态正好与地址线的信息相同。

在实际应用中,P2口通常作为高8位地址总线使用。

4)P3口

P3口某一位的结构图如图2-12所示。由图可见,电路由一个输出锁存器(D触发器)、3个三态输入缓冲器(1、2和3)、一个与非门和一个输出驱动电路(T和上拉电阻)组成。

(1)P3口用作第一功能(通用I/O口)。P3口用作通用I/O口时,第二输出功能信号W=1,P3口的每一位都可定义为输入或输出,其工作原理同P1口类似。P3口作为I/O通用,属于准双向口。

(2)P3口用作第二功能。当CPU不对P3口进行字节或位寻址时,内部硬件自动将口锁存器的Q端置1。这时,P3口作为第二功能使用。在真正的应用电路中,P3口的第二功能显得更为重要。

图2-12 P3口某位的结构

5)P口带负载能力及注意事项

(1)P口带负载能力。

① P0、P1、P2、P3口的电平与CMOS和TTL电平兼容。

② PO口的每一位能驱动8个LSTTL负载。在作为通用I/O口使用时,输出驱动电路是开漏的,所以驱动集电极开路(OC门)电路或漏级开路电路需外接上拉电阻。当作为地址/数据总线使用时(T1可以提供上拉电平),口线不是开漏的,无须外接上拉电阻。

③ P1~P3口的每一位能驱动4个LSTTL负载。它们的输出驱动电路有上拉电阻,所以可以方便地由集电极开路(OC门)电路或漏级开路电路所驱动,而无须外接上拉电阻。

④ 对于 80C51 单片机(CHMOS),端口只能提供几毫安的输出电流,故当作输出口去驱动一个普通晶体管的基极时,应在端口与晶体管基极间串联一个电阻,以限制高电平输出时的电流。

(2)使用P0~P3口的注意事项。

如果 80C51单片机片内程序存储器ROM够用,不需要扩展片外存储器和I/O接口,80C51的4个口均可作I/O口使用。

4个口在作为输入口使用时,均应先对其写1,以避免误读。

P0口作为I/O口使用时应外接10kΩ的上拉电阻,其他口则可不必外接。

P2口的某几根线作为地址使用时,剩下的线不能作为I/O口线使用。

P3 口的某些口线作为第二功能时,剩下的口线可以单独作为I/O口线使用。

2.80C51的时钟电路与时序

1)时钟电路

单片机时钟电路是单片机系统中的一个重要组成部分,它用于提供单片机的基本时钟信号,以驱动其内部的计时和操作。

时钟信号对于单片机来说非常重要,它决定了单片机的整体性能和工作稳定性。时钟信号用作时序控制和数据同步,它将微处理器中的各种操作同步到适当的时机。

在单片机中,时钟信号通常由一个时钟发生器电路产生,这个电路可以是一个晶体振荡器陶瓷振荡器或者其他形式的时钟源。这些时钟源以一定的频率振荡产生稳定的时钟信号,并通过时钟电路输入到单片机的时钟输入引脚。

单片机的时钟电路可以分为内部时钟和外部时钟两种类型:

① 内部时钟:某些单片机具有内部时钟发生器,它在芯片内部产生时钟信号。内部时钟通常由片内振荡电路产生,通过设置寄存器或控制位来调整频率。

② 外部时钟:其他单片机需要外部时钟源,例如晶振。外部时钟源通常由外部电路(如晶体振荡器)提供,通过电路连接到单片机的时钟输入引脚。

单片机内部时钟电路的工作原理:

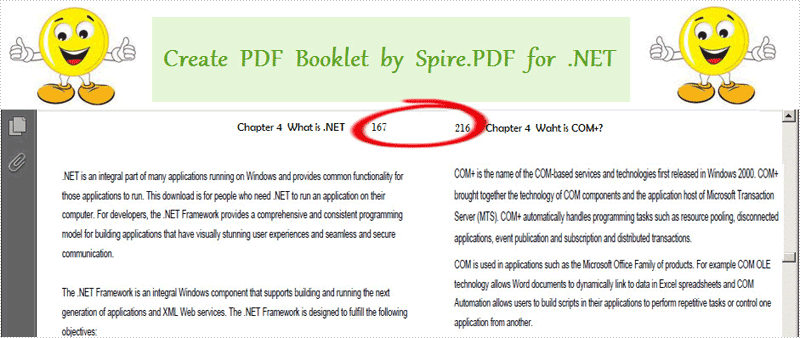

时钟电路就是一个振荡器,给单片机提供一个节拍,单片机执行各种操作必须在这个节拍的控制下才能进行。因此单片机没有时钟电路是不会正常工作的。时钟电路本身是不会控制什么东西,而是你通过程序让单片机根据时钟来做相应的工作。在MCS—51单片机片内有一个高增益的反相放大器,反相放大器的输入端为XTAL1,输出端为XTAL2,由该放大器构成的振荡电路和时钟电路一起构成了单片机的时钟方式。根据硬件电路的不同,单片机的时钟连接方式可分为内部时钟方式和外部时钟方式,如图2-13和2-14所示

图2-13内部方式

图2-14外部方式

2)时序

电路中的时序是指信号或操作在时间上的先后顺序和持续时间。时序在数字电路中至关重要,因为它确保了数据在正确的时间被捕获、处理和传输。

时序电路是一种具有记忆功能的电路,它由基本的逻辑门电路加上反馈逻辑回路或器件组合而成。与组合电路不同,时序电路的输出不仅取决于当前的输入值,还取决于过去的输入或内部状态。这种特性使得时序电路能够处理和存储信息,常见于触发器、锁存器、计数器等电路中。

时序电路与组合电路的主要区别在于其逻辑功能。组合电路的输出仅取决于当前输入,而与时序电路不同,时序电路的输出还受到过去输入或内部状态的影响。这种区别使得时序电路能够处理和存储信息,而组合电路则不能。

80C51 的时序就是80C51在执行指令时所需控制信号的时间顺序。80C51单片机的时序定时单位从小到大依次为节拍、状态周期、机器周期和指令周期。

① 节拍。把晶振周期(振荡周期)定义为节拍(用P表示)。晶振脉冲经过二分频后,就是单片机的时钟周期,时钟周期也称为状态(用S表示)。

这样,一个状态就包含两个节拍,前半周期对应的节拍叫节拍1(P1),后半周期对应的节拍叫节拍2(P2)。

② 状态周期。状态周期(或状态S)是晶振周期的两倍,它分为P1节拍和P2节拍。

③ 机器周期。80C51采用定时控制方式,因此它有固定的机器周期。这里规定一个机器周期的宽度为6个状态,并依次表示为S1~S6。由于一个状态又包括两个节拍,因此,一个机器周期总共有12个节拍,分别记作S1P1,S1P2,···,S6P1,S6P2。由于一个机器周期共有12个晶振周期,因此机器周期就是晶振脉冲的十二分频。当晶振脉冲频率为12MHz时,一个机器周期为1μs;当晶振脉冲频率为6MHz时,一个机器周期为2μs。

④ 指令周期。指令周期是最大的时序定时单位,执行一条指令所需要的时间就称为指令周期。它一般由若干机器周期组成。不同的指令所需要的机器周期数也不相同。通常,包含一个机器周期的指令称为单周期指令,包含两个机器周期的指令称为双周期指令。

图2-15 80C51的典型时序

由图2-15可见,ALE引脚上出现的信号是周期性的,在每个机器周期内出现两次高电平。第一次出现在S1P2和S2P1期间,第二次出现在S4P2和S5P1期间。ALE信号每出现一次,CPU就进行一次取指操作,但由于不同指令的字节数和机器周期数不同,因此取指后半周期对令操作也随指令不同而有小的差异。

按照指令字节数和机器周期数,80C51的111条指令可分为6类,分别是单字节单周期指令、单字节双周期指令、单字节四周期指令,双字节单周期指令,双字节双周期指令、三字节双周期指令。

3.80C51的复位电路

80C51单片机复位的目的是使CPU和系统中的其他功能部件都处在一个确定的初始状态,并从这个状态开始工作,例如复位后PC=0000H,使单片机从第一个单元取指令。

80C51单片机复位的条件是:必须使RST端(9脚)加上持续两个机器周期(即24个晶振周期)的高电平。例如,若时钟频率为12MHz,每机器周期为1us,则只需2us以上时间的高电平,在RST引脚出现高电平后的第二个机器周期执行复位。单片机常见的复位电路如图2-16(a)和2-16(b)所示。

图2-16 复位电路

图2-16(a)所示为上电自动复位电路,它是利用电容充电来实现的。在接电瞬间,RST端的电位与Vcc相同,随着充电电流的减少,RST的电位逐渐下降。只要保证RST为高电平的时间大于两个机器周期,便能正常复位。

图2-16(b)所示为按键手动复位电路。该电路除具有上电复位功能外,若要复位,只需按图2-16(b)中的RESET键,此时电源+5V经电阻R1、R2分压,在RESET端产生一个复位高电平。电路中通常选择:C=10uF,R=10kΩ,R1=200Ω。

4.80C51单片机复位后的状态

80C51单片机的复位功能是把PC初始化为0000H,使CPU从0000H单元开始执行程序;复位操作同时使SFR寄存器进入初始化,但片内RAM的数据是不变的。几个主要特殊功能寄存器复位状态如表2-7所示。

表2-7 主要特殊功能寄存器复位状态

记住一些特殊功能寄存器复位后的主要状态对熟悉单片机操作,减短应用程序中的初始化部分是十分必要的。对个别特殊功能寄存器作如下说明:

PC=0000H,表明单片机复位后程序从0000H地址单元开始执行。

PSW=00H,表明选寄存器0组为工作寄存器组。

SP=07H,表明堆栈指针指向片内RAM的07H单元,当80C51单片机复位后,堆栈第一个数据被写人08H单元中。但08H~1FH单元分别属于工作存器1~3组,如程序要用到这些区,最好把SP值改为1FH或更大的值。一般在片内RAM的30H~7FH单元中开辟堆栈。

P0~P3口用作输入口时,必须先写入1。单片机在复位后,已使P0~P3口每一端线为1,为这些端线用作输入口做好了准备。

![[含文档+PPT+源码等]精品基于django实现的原生Andriod天气信息的着装搭配系统](https://img-blog.csdnimg.cn/img_convert/642fc3f20ff15794357a8da997a1d4c8.jpeg)

![【实战篇】用SkyWalking排查线上[xxl-job xxl-rpc remoting error]问题](https://i-blog.csdnimg.cn/direct/25dfdd0058c144cba6648fcfbca407cf.png)