GIC-V2 中断控制器架构

参考文档:《ARM®Generic Interrupt Controller Architecture version 2.0》

GIC:Generic Interrupt Controller(GIC)

本文省略中断虚拟化相关章节。

1、Introduction(简介)

中断状态:

The following states apply at each interface between the GIC and a connected processor:

and is waiting to be serviced by a target processor.

- Inactive:An interrupt that is not active or pending.

- Pending:An interrupt from a source to the GIC that is recognized as asserted in hardware, or generated by software,

- Active:An interrupt from a source to the GIC that has been acknowledged(确认) by a processor, and is being serviced but has not completed.

- Active and pending:A processor is servicing the interrupt and the GIC has a pending interrupt from the same source.

中断类型:

A device that implements this GIC architecture can manage the following types of interrupt:

Peripheral interrupt:This is an interrupt asserted(有效的) by a signal to the GIC. The GIC architecture defines the

following types of peripheral interrupt:

- Private Peripheral Interrupt (PPI) :This is a peripheral interrupt that is specific to a single processor.

- Shared Peripheral Interrupt (SPI) :This is a peripheral interrupt that the Distributor can route to any of a specified combination of processors.

Each peripheral interrupt is either:

Edge-triggered:This is an interrupt that is asserted on detection of a rising edge of an interrupt signal and then,

regardless of the state of the signal, remains asserted until it is cleared by the conditions defined by this specification.

Level-sensitive: This is an interrupt that is asserted whenever the interrupt signal level is active, and deasserted whenever the level is not active.

- Software-generated interrupt (SGI):This is an interrupt generated by software writing to a GICD_SGIR register in the GIC.

The system uses SGIs for interprocessor communication(核间通讯).

An SGI has edge-triggered properties. The software triggering of the interrupt is equivalent to the edge transition of the interrupt request signal.

When an SGI occurs in a multiprocessor implementation, the CPUID field in the Interrupt Acknowledge Register, GICC_IAR,

or the Aliased Interrupt Acknowledge Register, GICC_AIAR, identifies the processor that requested the interrupt.

中断处理模型

In a multiprocessor implementation, there are two models for handling interrupts:

- 1-N model:Only one processor handles this interrupt. The system must implement a mechanism to determine

which processor handles an interrupt that is programmed to target more than one processor.

- N-N model:All processors receive the interrupt independently(独立的). When a processor acknowledges the interrupt,

the interrupt pending state is cleared only for that processor. The interrupt remains pending for the other processors.

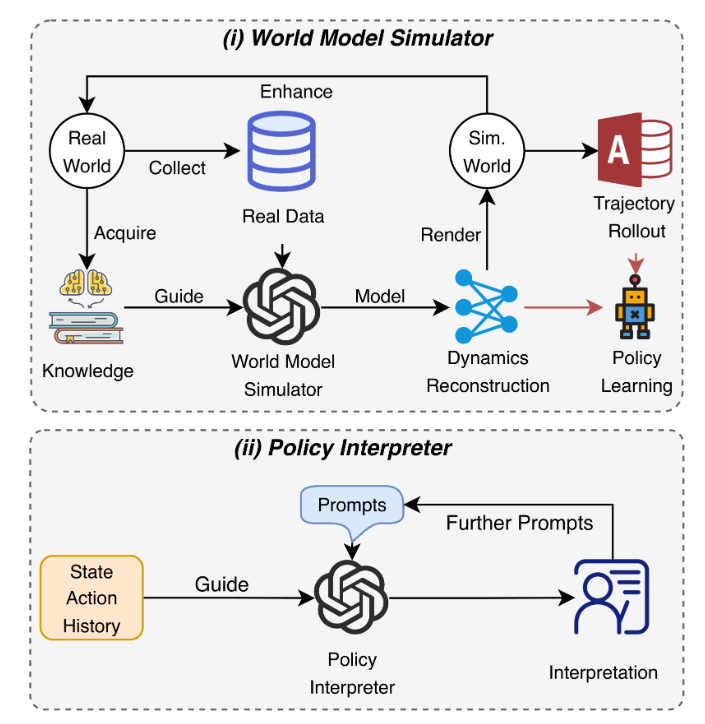

2、GIC Partitioning(GIC组成)

This chapter describes the architectural partitioning of the major GIC interfaces and components, and introduces the

functionality of the major GIC components, the Distributor and the CPU interfaces 。

The GIC architecture splits(拆分) logically into a Distributor block and one or more CPU interface blocks.

The GIC Virtualization Extensions add one or more virtual CPU interfaces to the GIC 。

GIC架构上拆分为两部分:Distributor block和one or more CPU interface blocks

Distributor(分发器)

The Distributor block performs interrupt prioritization(中断优先级排序) and distribution(分发) to the CPU interface blocks that connect to the processors in the system.

The Distributor block registers are identified by the GICD_ prefix.

CPU interfaces(CPU接口)

Each CPU interface block performs priority masking(优先级屏蔽) and preemption handling(抢占处理) for a connected processor in the system.

CPU interface block registers are identified by the GICC_ prefix.

When describing a GIC that includes the GIC Virtualization Extensions, a CPU interface is sometimes called a physical CPU interface,

to avoid possible confusion with a virtual CPU interface.

2.1、The Distributor

The Distributor centralizes(集中) all interrupt sources, determines the priority of each interrupt, and for each CPU

interface forwards the interrupt with the highest priority to the interface, for priority masking and preemption handling.

The Distributor provides a programming interface for:

- Globally enabling the forwarding of interrupts to the CPU interfaces.

- Enabling or disabling each interrupt.

- Setting the priority level of each interrupt.

- Setting the target processor list of each interrupt.

- Setting each peripheral interrupt to be level-sensitive or edge-triggered.

- Setting each interrupt as either Group 0 or Group 1.

- Forwarding an SGI to one or more target processors.

In addition, the Distributor provides:

- visibility of the state of each interrupt

- a mechanism for software to set or clear the pending state of a peripheral interrupt.

Interrupts from sources are identified using ID numbers(通过ID号来识别中断源). Each CPU interface can see up to 1020 interrupts.

The banking of SPIs and PPIs increases the total number of interrupts supported by the Distributor.

The GIC assigns interrupt ID numbers ID0-ID1019 as follows:

• Interrupt numbers ID32-ID1019 are used for SPIs.

• Interrupt numbers ID0-ID31 are used for interrupts that are private to a CPU interface. These interrupts are banked in the Distributor(这些中断存储在分发器中).

A banked interrupt is one where the Distributor can have multiple interrupts with the same ID.

A banked interrupt is identified uniquely by its ID number and its associated CPU interface number.

Of the banked interrupt IDs:

— ID0-ID15 are used for SGIs

— ID16-ID31 are used for PPIs

In a multiprocessor system:

— A PPI is forwarded to a particular CPU interface, and is private to that interface.

In prioritizing interrupts for a CPU interface the Distributor does not consider PPIs that relate to other interfaces.

(在对CPU接口的中断进行优先级排序时,分发服务器不考虑与其他接口相关的ppi)

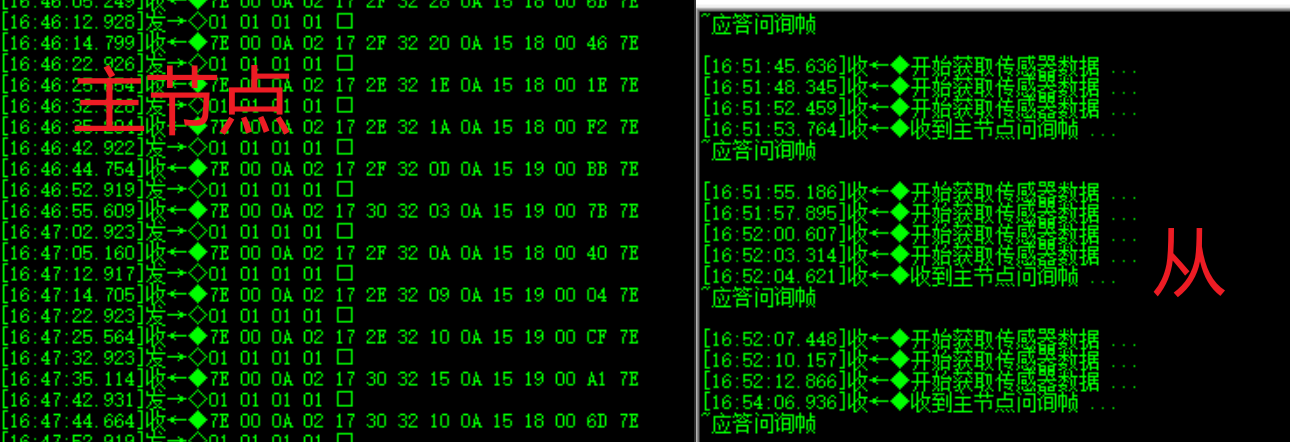

— Each connected processor issues an SGI by writing to the GICD_SGIR in the Distributor.

Each write can generate SGIs with the same ID that target multiple processors.

In the Distributor, an SGI is identified uniquely by the combination of its interrupt number, ID0-ID15,

the target processor ID(目标处理器ID), CPUID0-CPUID7, and the processor source ID(源处理器ID), CPUID0-CPUID7, of the

processor that issued the SGI. When the CPU interface communicates the interrupt ID to a targeted

processor, it also provides the processor source ID, so that the targeted processor can uniquely identify the SGI.

SGI banking means the GIC can handle multiple SGIs simultaneously, without resource conflicts.

The Distributor ignores any write to the GICD_SGIR that is not from a processor that is connected to

one of the CPU interfaces. How the Distributor determines the processor source ID of a processor

writing to the GICD_SGIR is IMPLEMENTATION SPECIFIC.

In a uniprocessor system, there is no distinction(差别) between shared and private interrupts, because all interrupts are visible to the processor.

In this case the processor source ID value is 0。

- Interrupt numbers ID1020-ID1023 are reserved for special purposes.

System software sets the priority of each interrupt. This priority is independent(独立的) of the interrupt ID number.

In any system that implements the ARM Security Extensions, to support a consistent model for message passing

between processors, ARM strongly recommends that all processors reserve:

• ID0-ID7 for Non-secure interrupts

• ID8-ID15 for Secure interrupts.

2.2、CPU interfaces

Each CPU interface block provides the interface for a processor that is connected to the GIC.

Each CPU interface provides a programming interface for:

• enabling the signaling of interrupt requests to the processor

• acknowledging(确认) an interrupt

• indicating completion of the processing of an interrupt(指示中断处理完成)

• setting an interrupt priority mask(中断优先级掩码) for the processor

• defining the preemption policy for the processor

• determining the highest priority pending interrupt for the processor.

When enabled, a CPU interface takes the highest priority pending interrupt for its connected processor and

determines whether the interrupt has sufficient priority(足够的优先级) for it to signal the interrupt request to the processor.

To determine whether to signal the interrupt request to the processor, the CPU interface considers the interrupt priority

mask and the preemption settings for the processor. At any time, the connected processor can read the priority of its

highest priority active interrupt from its GICC_HPPIR, a CPU interface register.

The mechanism for signaling an interrupt to the processor is IMPLEMENTATION DEFINED.

On ARM processor implementations, the traditional mechanism for signaling an interrupt request is by asserting nIRQ or nFIQ.

The processor acknowledges(确认) the interrupt request by reading the CPU interface Interrupt Acknowledge Register.

This read returns one of:

• The ID number of the highest priority pending interrupt, if that interrupt is of sufficient priority(足够的优先级) for it to be

signaled to the processor. This is the normal response to an interrupt acknowledge.

• Exceptionally(极端情况下), an ID number that indicates a spurious(虚假的) interrupt.

When the processor acknowledges the interrupt at the CPU interface, the Distributor changes the status of the

interrupt from pending to either active, or active and pending. At this point the CPU interface can signal another

interrupt to the processor, to preempt(抢占) interrupts that are active on the processor. If there is no pending interrupt with

sufficient priority for signaling to the processor, the interface deasserts(放弃) the interrupt request signal to the processor.

When the interrupt handler on the processor has completed the processing of an interrupt, it writes to the CPU

interface to indicate interrupt completion. There are two stages to interrupt completion:

• priority drop(优先级下降), meaning the priority of the processed interrupt can no longer prevent the signaling of another interrupt to the processor

• interrupt deactivation(非激活), meaning the Distributor removes the active state of the interrupt.

In a GICv1 implementation, these two stages always happen together, when the processor writes to the CPU interface End of Interrupt register.

In a GICv2 implementation, the GICC_CTLR.EOImode bit determines whether:

• the two stages happen together, when the processor writes to the CPU interface End of Interrupt register

• the two stages are separated, so that:

— priority drop happens when the processor writes to the CPU interface End of Interrupt register

— interrupt deactivation happens later, when the processor writes to the CPU interface Deactivate Interrupt register.

priority drop和 interrupt deactivation 后面章节有详细描述。

interrupt signal bypass, and GICv2 bypass disable

In all GIC implementations, a CPU interface optionally includes interrupt signal bypass, so that, when the signaling

of an interrupt by the interface is disabled, a system legacy interrupt signal is passed to the interrupt request input

on the processor, bypassing(绕过) the GIC functionality.

Power management, GIC v2

The GICv2 architecture supports wakeup events in implementations that require power management.

As shown in Figure 2-4 on page 2-29, the GICv2 interrupt bypass logic described in GICv2 interrupt bypass, with

bypass disable on page 2-28 includes signals that can be used as wakeup signals to a system power controller. These

signals are available even when both interrupt signaling by the GIC, and interrupt bypass, are disabled.

In addition, the GICC_APRn registers provide support for preserving(保留) and restoring state in power-management

applications. However, to ensure that Non-secure accesses do not interfere with Secure operation, Secure and

Non-secure copies of these registers are provided.

3、Interrupt Handling and prioritization(中断处理和优先级)

3.1 、About interrupt handling and prioritization

The GIC architecture supports uniprocessor and multiprocessor systems:

• in a uniprocessor system the GIC has a single processor interface, the CPU interface

• in a multiprocessor system the GIC has a CPU interface for each connected processor.

3.1.1、Handling different interrupt types in a multiprocessor system

A GIC supports peripheral interrupts and software-generated interrupts.

In a multiprocessor implementation the GIC handles:

• software generated interrupts (SGIs) using the GIC N-N model

• peripheral (hardware) interrupts using the GIC 1-N model.

3.1.2、Identifying the supported interrupts(识别支持的中断)

The GIC architecture defines different ID values for the different types of interrupt.

However, there is no requirement for the GIC to implement a continuous block of interrupt IDs for any interrupt type.

To correctly handle interrupts, software must know what interrupt IDs are supported by the GIC.

Software can use the GICD_ISENABLERns to discover this information. If the processor implements the ARM Security Extensions,

Secure software determines the interrupts that are visible to Non-secure software. The Non-secure software must

know which interrupts it can see, and might use this discovery process to find this information.

GICD_ISENABLER0 provides the Set-enable bits for both:

• SGIs, using interrupt IDs 15-0, corresponding to register bits [15:0]

• PPIs, using interrupt IDs 31-16, corresponding to register bits [31:16].

The remaining GICD_ISENABLERns, from GICD_ISENABLER1, provide the Set-enable bits for the SPIs,starting at interrupt ID 32.

If an interrupt is:

• not supported, the Set-enable bit corresponding to its interrupt ID is RAZ/WI

• supported and permanently(永久地) enabled, the Set-enable bit corresponding to its interrupt ID is RAO/WI.

Software discovers the interrupts that are supported by:

1. Reading the GICD_TYPER. The GICD_TYPER.ITLinesNumber field identifies the number of implemented

GICD_ISENABLERns, and therefore the maximum number of SPIs that might be supported.

2. Writing to the GICD_CTLR to disable forwarding of interrupts from the distributor to the CPU interfaces.

3. For each implemented GICD_ISENABLERn, starting with GICD_ISENABLER0:

• Writing 0xFFFFFFFF to the GICD_ISENABLERn.

• Reading the value of the GICD_ISENABLERn. Bits that read as 1 correspond to supported interrupt IDs.

Software uses the GICD_ICENABLERns to discover the interrupts that are permanently enabled. For each

implemented GICD_ICENABLERn, starting with GICD_ICENABLER0, software:

1. Writes 0xFFFFFFFF to the GICD_ICENABLERn. This disables all interrupts that can be disabled.

2. Reads the value of the GICD_ICENABLERn. Bits that read as 1 correspond to interrupts that are permanently enabled.

3. Writes 1 to any GICD_ISENABLERn bits corresponding to interrupts that must be re-enabled.

The GIC implements the same number of GICD_ISENABLERns and GICD_ICENABLERns.

When software has completed its discovery, it typically writes to the GICD_CTLR to re-enable forwarding of

interrupts from the Distributor to the CPU interfaces.

If the GIC implements the GIC Security Extensions, software can use Secure accesses to discover all the supported

interrupt IDs, see The effect of interrupt grouping on interrupt handling on page 3-48 for more information.

Software using Non-secure accesses can discover and control only the interrupts that are configured as Non-secure.

If Secure software changes the security configuration of any interrupts after Non-secure software has discovered its

supported interrupts, it must communicate the effect of those changes to the Non-secure software.

In a GIC that provides interrupt grouping, software can:

• write to the GICD_IGROUPRn registers, to configure interrupts as Group 0 or Group 1

• control the forwarding of Group 0 and Group 1 interrupts independently, using the GICD_CTLR.EnableGrp0 and GICD_CTLR.EnableGrp1 bits.

3.2、General handling of interrupts(中断处理)

The Distributor maintains a state machine for each supported interrupt on each CPU interface.

Interrupt handling state machine and its state transitions. The possible states of an interrupt are:

• inactive

• pending

• active

• active and pending.

This section gives an overview of the handling of interrupts in a GIC implementation that does not include

the GIC Security Extensions. It does not give a full description of handling grouped interrupts.

Interrupt grouping, and the GIC Security Extensions, extend the basic model of GIC operation described in this

section.

This basic model of interrupt handling also applies to the handling of virtual interrupts in an implementation

that includes the GIC Virtualization Extensions.

When the GIC recognizes(识别) an interrupt request, it marks its state as pending. Regenerating(再生成) a pending interrupt does not affect the state of the interrupt.

The GIC interrupt handling sequence is:(GIC中断处理流程)

1. The GIC determines the interrupts that are enabled.

2. For each pending interrupt, the GIC determines the targeted processor or processors.

3. For each CPU interface, the Distributor forwards the highest priority pending interrupt that targets that interface.

4. Each CPU interface determines whether to signal an interrupt request to its processor, and if required, does so.

5. The processor acknowledges(确认) the interrupt, and the GIC returns the interrupt ID and updates the interrupt state.

6. After processing the interrupt, the processor signals End of Interrupt (EOI) to the GIC.

In more detail, these steps are as follows:

1. The GIC determines whether each interrupt is enabled. An interrupt that is not enabled has no effect on the GIC.

2. For each enabled interrupt that is pending, the Distributor determines the targeted processor or processors.

3. For each processor, the Distributor determines the highest priority pending interrupt, based on the priority

information it holds for each interrupt, and forwards the interrupt to the targeted CPU interfaces.

4. If the distributor is forwarding an interrupt request to a CPU interface, the CPU interface determines whether

the interrupt has Sufficient priority(足够的优先级) to be signaled to the processor. If the interrupt has sufficient priority, the

GIC signals an interrupt request to the processor.

5. When a processor takes the interrupt exception, it reads the GICC_IAR of its CPU interface to acknowledge the interrupt.

This read returns an Interrupt ID, and for an SGI, the source processor ID, that the processor

uses to select the correct interrupt handler. When it recognizes this read, the GIC changes the state of the

interrupt as follows:

• if the pending state of the interrupt persists(持续) when the interrupt becomes active, or if the interrupt is

generated again, from pending to active and pending.

• otherwise, from pending to active

• A level-sensitive(电平) peripheral interrupt persists when it is acknowledged by the processor, because the

interrupt signal to the GIC remains asserted until the Interrupt Service Routine (ISR) running on the

processor accesses the peripheral asserting the signal.

• In a multiprocessor implementation, the GIC handles:

— PPIs and SGIs using the GIC N-N model, where the acknowledgement of an interrupt by one

processor has no effect on the state of the interrupt on other CPU interfaces

— SPIs using the GIC 1-N model, where the acknowledgement of an interrupt by one processor

removes the pending status of the interrupt on any other targeted processors

• In GICv2, when using a software model with the GICC_CTLR.AckCtl bit set to 0, separate registers

are used to manage Group 0 and Group 1 interrupts, as follows:

— GICC_IAR, GICC_EOIR, and GICC_HPPIR for Group 0 interrupts

— GICC_AIAR, GICC_AEOIR, and GICC_AHPPIR for Group 1 interrupts.

ARM deprecates(反对) the use of GICC_CTLR.AckCtl, and strongly recommends using a software model

where GICC_CTLR.AckCtl is set to 0。

6. When the processor has completed handling the interrupt, it must signal this completion to the GIC.

As described in Priority drop and interrupt deactivation, this:

• always requires a valid write to an end of interrupt register (EOIR)

• might also require a subsequent write to the deactivate interrupt register, GICC_DIR.

For each CPU interface, the GIC architecture requires the order of the valid writes to an EOIR to be the

reverse(相反) of the order of the reads from the GICC_IAR or GICC_AIAR, so that each valid EOIR write refers

to the most recent interrupt acknowledge.

If, after the EOIR write, there is no pending interrupt of Sufficient priority, the CPU interface deasserts(放弃) the

interrupt exception request to the processor.

A CPU interface never signals to the connected processor any interrupt that is active and pending.

It only signals interrupts that are pending and have sufficient priority:

• For PPIs and SGIs, the active status of particular interrupt ID is banked between CPU interfaces. This

means that if a particular interrupt ID is active or active and pending on a CPU interface, then no

interrupt with that same ID is signaled on that CPU interface.

• For SPIs, the active status of an interrupt is common to all CPU interfaces. This means that if an

interrupt is active or active and pending on one CPU interface then it is not signaled on any CPU interface.

3.2.1、Priority drop and interrupt deactivation

When a processor completes the processing of an interrupt, it must signal this completion to the GIC.

Interrupt completion requires the following changes to the GIC state:

Priority drop (优先级下降)

Priority drop is the drop in the Running priority that occurs on a valid write to an EOIR, either the GICC_EOIR or the GICC_AEOIR.

A valid write is a write that is not UNPREDICTABLE, is not ignored, and is not writing an interrupt ID value greater than 1019.

On priority drop, the running priority is reduced from the priority of the interrupt referenced by the EOIR write to either:

• the priority of the highest-priority active interrupt for which there has been no EOIR write

• the Idle priority, if there is no active interrupt for which there has been no EOIR write.

See Preemption on page 3-45 for more information about running priority.

Interrupt deactivation(中断失活)

Interrupt deactivation is the change of the state of an interrupt, either:

• from active and pending, to pending

• from active, to idle.

On a GICv1 implementation, and on a GICv2 implementation when GICC_CTLR.EOImode is set to 0,

a valid EOIR write also deactivates the interrupt it references.

On a GICv2 implementation, setting GICC_CTLR.EOImode to 1 separates the priority drop and interrupt eactivation operations,

and interrupt handling software must:

1. Perform a valid EOIR write, to cause priority drop on the GIC CPU interface.

2. Subsequently, write to the GICC_DIR, to deactivate the interrupt.

The GIC architecture specification requires that valid EOIR writes are ordered, so that:

• a valid GICC_EOIR write corresponds to the most recently acknowledged interrupt

• a valid GICC_AEOIR write corresponds to the most recently acknowledged Group 1 interrupt.

• whether a GICC_EOIR write affects Group 0 or Group 1 interrupts depends on both:

— the value of the GICC_CTLR. AckCtl bit

— if the GIC implements the GIC Security Extensions, whether the write is Secure or Non-secure.

In a GICv2 implementation that includes the Security Extensions:

• GICC_AEOIR is an alias of the Non-secure copy of GICC_EOIR

• GICC_AIAR is an alias of the Non-secure copy of GICC_IAR

• GICC_AIAR and GICC_AEOIR are Secure registers, meaning they are accessible only by Secure accesses.

There is no ordering requirement for GICC_DIR writes. However, the effect is UNPREDICTABLE if software writes

to GICC_DIR when:

• GICC_CTLR.EOImode is set to 0

• GICC_CTLR.EOImode is set to 1 and there has not been a corresponding write to GICC_EOIR or GICC_AEOIR.

When virtualizing physical interrupts, ARM recommends that, for each CPU interface that corresponds to a processor running virtual machines:

• GICC_CTLR.EOImode bit is set to 1

• if the GIC implements the GIC Security Extensions, the GICC_CTLR.EOImodeNS bit is set to 1

See Completion of virtualized physical interrupts on page 5-161 for more information.

3.2.2、Interrupt controls in the GIC(GIC中断控制)

The following sections describe the interrupt controls in the GIC:

• Interrupt enables

• Setting and clearing pending state of an interrupt on page 3-40

• Finding the active or pending state of an interrupt on page 3-40

• Generating an SGI on page 3-40.

Interrupt enables

For peripheral interrupts, a processor:

• enables an interrupt by writing to the appropriate GICD_ISENABLERn bit

• disables an interrupt by writing to the appropriate GICD_ICENABLERn bit.

Whether SGIs are permanently enabled, or can be enabled and disabled by writes to the GICD_ISENABLERn and

GICD_ICENABLERn, is IMPLEMENTATION DEFINED.

Writes to the GICD_ISENABLERns and GICD_ICENABLERns control whether the Distributor forwards specific interrupts to the CPU interfaces.

Disabling an interrupt by writing to the appropriate GICD_ICENABLERn does not prevent that interrupt from changing state, for example becoming pending

Setting and clearing pending state of an interrupt

For peripheral interrupts, a processor can:

• set the pending state by writing to the appropriate GICD_ISPENDRn bit

• clear the pending state by writing to the appropriate GICD_ICPENDRn bit.

For a level-sensitive interrupt:

• If the hardware signal of an interrupt is asserted when a processor writes to the corresponding

GICD_ICPENDRn bit then the write to the register has no effect on the pending state of the interrupt.

• If a processor writes a 1 to an GICD_ISPENDRn bit then the corresponding interrupt becomes pending

regardless of the state of the hardware signal of that interrupt, and remains pending regardless of the assertion or deassertion of the signal.

For more information about the control of the pending state of a level-sensitive interrupt see Control of the pending

status of level-sensitive interrupts on page 4-100.

For SGIs, the GIC ignores writes to the corresponding GICD_ISPENDRn and GICD_ICPENDRn bits.

A processor cannot change the state of a software-generated interrupt by writing to these registers.

Typically, an SGI is made pending by writing to the GICD_SGIR.

In GICv2, the pending state of SGIs can also be modified directly using the GICD_SPENDSGIRn and GICD_CPENDSGIRn bits.

Finding the active or pending state of an interrupt

A processor can find:

• the pending state of an interrupt by reading the corresponding GICD_ISPENDRn or GICD_ICPENDRn bit

• the active state of an interrupt by reading the corresponding GICD_ISACTIVERn or GICD_ICACTIVERn bit.

The corresponding register bit is 1 if the interrupt is pending or active.

If an interrupt is pending and active the corresponding bit is 1 in both registers.

When preserving(保存) or restoring GIC state, a processor must take account of the pending and active state of all interrupts.

For more information see Preserving and restoring GIC state on page 4-155.

For an SGI, the corresponding GICD_ISPENDRn and GICD_ICPENDRn bits RAO if there is a pending interrupt

from at least one generating processor that targets the processor reading the GICD_ISPENDRn or GICD_ICPENDRn.

In GICv2, the processor that issues the SGI can also be determined by reading the corresponding GICD_SPENDSGIRn or GICD_CPENDSGIRn bits.

Generating an SGI

A processor generates an SGI by writing to an GICD_SGIR.

An SGI can target multiple processors, and the GICD_SGIR write specifies the target processor list.

The GICD_SGIR includes optimization for:

• interrupting only the processor that writes to the GICD_SGIR

• interrupting all processors other than the one that writes to the GICD_SGIR.

SGIs from different processors use the same interrupt IDs. Therefore, any target processor can receive SGIs with

the same interrupt ID from different processors. However, the pending states of any two SGIs are independent if any of the following are different:

• interrupt ID

• source processor

• target processor.

Only one interrupt with a specific interrupt ID can be active on a CPU interface at any time.

This means that a CPU interface cannot have two SGIs with the same interrupt ID active at the same time, even if different processors have

signaled SGIs with the same interrupt ID to that processor.

On the CPU interface of the target processor, reading the GICC_IAR for an SGI returns both the interrupt ID and

the CPU ID of the processor that generated the interrupt, the source processor for the interrupt.

The combination of interrupt ID and source CPU ID uniquely identifies the interrupt to the target processor.

In a multiprocessor implementation, the interrupt priority of each SGI interrupt ID is defined independently for each

target processor, see Interrupt Priority Registers, GICD_IPRIORITYRn on page 4-104. For each CPU interface, all

SGIs with a particular interrupt ID that are pending on that interface have the same priority and must be handled

serially. The order in which the CPU interface serializes these SGIs is IMPLEMENTATION SPECIFIC.

3.3、Interrupt prioritization(中断优先级)

This section describes interrupt prioritization in the GIC architecture. It includes the following subsections:

• Preemption on page 3-45

• Priority masking on page 3-45

• Priority grouping on page 3-45

• Interrupt generation on page 3-47.

Software configures interrupt prioritization in the GIC by assigning a priority value to each interrupt source.

Priority values are 8-bit unsigned binary. A GIC supports a minimum of 16 and a maximum of 256 priority levels.

If the GIC implements fewer than 256 priority levels, low-order bits of the priority fields are RAZ/WI.

This means that the number of implemented priority field bits is IMPLEMENTATION DEFINED in the range 4-8, as Table 3-1 shows.

In the GIC prioritization scheme, lower numbers have higher priority, that is, the lower the assigned priority value

the higher the priority of the interrupt. Priority field value 0 always indicates the highest possible interrupt priority,

and the lowest priority value depends on the number of implemented priority levels, as Table 3-1 shows.

The GICD_IPRIORITYRn registers hold the priority value for each supported interrupt. An implementation might

reserve an interrupt for a particular purpose and assign a fixed priority to that interrupt, meaning the priority value

for that interrupt is read-only. For other interrupts, software writes to the GICD_IPRIORITYRn registers to set the

interrupt priorities. It is IMPLEMENTATION DEFINED whether a write to GICD_IPRIORITYRn changes the priority of any active interrupt.

To determine the number of priority bits implemented, software can write 0xFF to a writable GICD_IPRIORITYRn priority field, and read back the value stored.

ARM recommends that, before checking the priority range in this way:

• for a peripheral interrupt, software first disables the interrupt

• for an SGI, software first checks that the interrupt is inactive.

If, on a particular CPU interface, multiple pending interrupts have the same priority, and have Sufficient priority for

the interface to signal them to the processor, it is IMPLEMENTATION SPECIFIC how the interface selects which interrupt to signal.

When an interrupt is active on a CPU interface, the GIC might signal a higher-priority interrupt on that CPU interface, see Preemption on page 3-45.

3.3.1、Preemption

A CPU interface supports signaling of higher priority pending interrupts to a target processor before an active interrupt completes.

CPU接口支持在活动中断完成之前向目标处理器发送高优先级待处理中断的信号

A pending interrupt is only signaled if both:

• Its priority is higher than the priority mask for that CPU interface, see Priority masking.

• Its group priority is higher than that of the Running priority on the CPU interface, see Priority grouping and Running Priority Register, GICC_RPR on page 4-142.

Preemption occurs at the time when the processor acknowledges the new interrupt, and starts to service it in

preference to the previously active interrupt or the currently running process. When this occurs, the initial active

interrupt is said to have been preempted. Starting to service an interrupt while another interrupt is still active is

sometimes described as interrupt nesting.

• For a processor that complies with the ARM architecture:

— The value of the I or F bit in the CPSR determines whether the processor responds to the signaled interrupt by starting the interrupt acknowledge procedure.

CPSR中I或F位的值决定处理器是否通过启动中断确认过程来响应信号中断

— When processing a preempting interrupt, the processor must save and later restore the context of the previously active ISR.

For more information, see the ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

• Priority drop means the priority of an interrupt no longer affects the Running priority on the CPU interface,

and therefore does not prevent interrupt preemption. In GICv1 implementations, priority drop happens only

when an interrupt is deactivated, but in GICv2 implementations, priority drop and interrupt deactivation can

be separated. For more information see Priority drop and interrupt deactivation on page 3-38.

3.3.2、Priority masking

The GICC_PMR for a CPU interface defines a priority threshold for the target processor.

The GIC only signals pending interrupts with a higher priority than this threshold value to the target processor.

A value of zero, the register reset value, masks all interrupts from being signaled to the associated processor.

The GIC does not use priority grouping when comparing the priority of a pending interrupt with the priority threshold.

The GIC always masks an interrupt that has the largest supported priority field value.

This provides an additional means of preventing an interrupt being signaled to any processor(这提供了一种额外的方法来防止中断被发送到任何处理器).

Writing 255 to the GICC_PMR always sets it to the largest supported priority field value.

Table 3-1 on page 3-44 shows how the largest supported field value varies with the number of implemented priority bits.

3.3.3、Priority grouping

Priority grouping uses the Binary Point Register, GICC_BPR, to split a priority value into two fields, the group priority and the subpriority(组优先级和子优先级).

When determining preemption, all interrupts with the same group priority are considered to have equal priority, regardless of the subpriority.

This means that there can only be one interrupt active at each group priority.

The active group priority is also known as the Preemption level. For more information, see Active Priorities Registers, GICC_APRn on page 4-149.

The GIC uses the group priority field to determine whether a pending interrupt has sufficient priority to preempt an active interrupt, as follows:

• For a pending interrupt to preempt an active interrupt, its group priority must be higher than the group priority

of the active interrupt. That is, the value of the group priority field for the new interrupt must be less than the

value of the group priority field of the Running priority.

• If there are no active interrupts on the CPU interface, the highest priority pending interrupt can be signaled

to a processor, regardless of the group priority.

In each case, the pending interrupt priority is compared with the priority mask, and the interrupt is signaled only if it is not masked.

在每种情况下,pending的中断优先级与优先级掩码进行比较,并且只有当中断未被掩码时才会发出信号。

For more information, see Priority masking on page 3-45.

The binary point field in the GICC_BPR controls the split of the priority bits into the two parts.

This 3-bit field specifies how many of the least significant bits of the 8-bit interrupt priority field are excluded from the group priority field, as Table 3-2 shows

这个3位字段(GICC_BPR bit[2:0])指定了8位中断优先级字段中有多少个最低有效位被排除在组优先级字段之外

The minimum binary point value supported is IMPLEMENTATION DEFINED in the range 0-3.

GICv1 implementations with the GIC Security Extensions and GICv2 implementations have two binary point registers.

The copy of the binary point register used to calculate priority grouping depends on whether the interrupt

is a Group 0 interrupt or a Group 1 interrupt, as defined by the GICD_IGROUPRn registers, and also on the value of the GICC_CTLR.CBPR bit.

Table 3-2 shows which binary point register is used for different GIC implementations.

3.3.4、Interrupt generation

The pseudocode in Exception generation pseudocode on page 3-64 describes the generation of interrupts by the GIC.

3.4、The effect of interrupt grouping on interrupt handling

This section describes the effect of interrupt grouping and the GIC Security Extensions on interrupt handling.

A GICv1 implementation that includes the GIC Security Extensions,

or any GICv2 implementation, provides two interrupt output signals for IRQ and FIQ exception requests(任何GICv2实现,为IRQ和FIQ异常请求提供两个中断输出信号):

• The CPU interface always uses the IRQ exception request for Group 1 interrupts

• Software can configure the CPU interface to use either IRQ or FIQ exception requests for Group 0 interrupts.

At power-on, or after a reset, any GIC implementation is configured to use only a single interrupt output signal, as

described in GIC power on or reset configuration on page 3-51

3.4.1、GIC interrupt grouping support

The GICD_IGROUPRn registers configure each interrupt as Group 0 or Group 1.

In a CPU interface, in a GICv2 implementation, the GICC_* alias registers can provide independent control of Group 0 and Group 1 registers, as Table 3-4 shows.

4、Programmers'Model(GIC中断控制器内存寄存器)

This chapter describes the Distributor and CPU interface registers.

4.1、About the programmers’ model

The programmers’ model provides the software interface to the GIC. This chapter describes the programmers’

model for the GIC Distributor and CPU interfaces, that operates using a memory-mapped register interface.

4.1.1 GIC register names

All of the GIC registers have names that provide a short mnemonic(助记的) for the function of the register. In these names:

• the first three letters are GIC, indicating a GIC register

• the fourth letter is one of:

— D, indicating a Distributor register

— C, indicating a CPU interface register

— H, indicating a virtual interface control register, typically accessed by a hypervisor

— V, indicating a virtual CPU interface register.

• the remaining letters are a mnemonic for the register, for example the GIC Distributor Control Register is called GICD_CTLR.

All GIC registers are 32-bits wide. Reserved register addresses are RAZ/WI.