1.1 并联输出电路设计注意事项

直接对两个功率运算放大器的输出进行硬接线并不是一种好的电气做法。如果两个运算放大器的输出直接连接在一起,则可能会导致不均匀的电流共享。这是因为其中的每个运算放大器都尝试强制施加略微不同的 Vout 电压,该电压取决于其各自的 Vos 电平。这种电流不平衡可能导致功率耗散不均和器件发热不均。尽管运算放大器之间产生的 Vout 差可能很小,但从电气角度看,这相当于将两个阻抗很低的电压源直接连接。运算放大器输出阻抗 (Zcl) 非常低,由于每个运算放大器运行时具有高环路增益,因此通常为毫欧姆。如果每个运算放大器具有不同的闭环增益设置,则 Zcl 在这两种情况下会有所不同,领导者-跟随者配置就是如此。当输出之间的连接电阻几乎为零时,电流可能会非常高,并影响基本电路功能。增加的输出镇流电阻能在很大程度上减小流经两个输出之间的电流。OPA593 领导者-跟随者并联输出电路如图 1-3 所示。直流电压和电流电平由 5V 直流输入产生,产生的输出电压 Vout 为 +50V。负载电流 I4 为 0.45A。通过增加电源可获得更高的输出电压,V+ 和 V– 引脚上的电压高达 85V。此配置中的两个 OPA593 运算放大器的输出电流高达 0.5A。

与任何电子元件一样,由于功率和热限制,必须考虑 OPA593 运算放大器和负载的功率耗散。每个 OPA593 消耗 1.25W,而本特定示例中,111Ω 负载电阻器消耗 22.5W。两个 OPA593 功率耗散变得非常高,如果电源电压和输出电压之间的差值较大且持续时间过长,它们将进入热关断状态。请记住,所示电路的预期应用具有快速 ATE 测试序列,其中驻留时间仅为几毫秒。快速 ATE 测试序列中的平均功率耗散远低于在持续高功率耗散条件下运行时的平均功率耗散。

并联 高电压、高电流 放大器实现 2 倍输出电流模块±2A

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.rhkb.cn/news/458739.html

如若内容造成侵权/违法违规/事实不符,请联系长河编程网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

vulnhub(16):sickos(两种打点方式)

端口 ip:192.168.72.154

nmap -Pn -p- 192.168.72.154 --min-rate 10000PORT STATE SERVICE

22 open ssh

3128 open http-proxy

8080 closed http-proxy web渗透方式一:web后台 正常访问80端口,是不开放的,我们需要配置…

高速定向广播声光预警系统赋能高速安全管控

近年来,高速重大交通事故屡见不鲜,安全管控一直是高速运营的重中之重。如何利用现代化技术和信息化手段,创新、智能、高效的压降交通事故的发生概率,优化交通安全管控质量,是近年来交管部门的主要工作,也是…

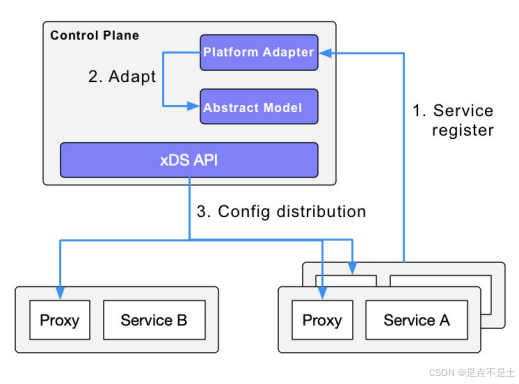

云原生Istio基础

一.Service Mesh 架构

Service Mesh(服务网格)是一种用于处理服务到服务通信的专用基础设施层。它的主要目的是将微服务之间复杂的通信和治理逻辑从微服务代码中分离出来,放到一个独立的层中进行管理。传统的微服务架构中&#x…

浅析Android View绘制过程中的Surface

前言

在《浅析Android中View的测量布局流程》中我们对VSYNC信号到达App进程之后开启的View布局过程进行了分析,经过对整个App界面的View树进行遍历完成了测量和布局,确定了View的大小以及在屏幕中所处的位置。但是,如果想让用户在屏幕上看到…

【十六进制数转十进制数 】

【十六进制数转十进制数 】 C语言版本C 版本Java版本Python版本 💐The Begin💐点点关注,收藏不迷路💐 从键盘接收一个十六进制数,编程实现将其转换成十进制数。

输入

输入一个十六进制数

输出

输出一个十进制数

样…

GitHub 上的优质 Linux 开源项目,真滴硬核!

作为一名互联网人,提起 Linux 大家都不陌生,尤其是日常跟 Linux 操作系统打交道最多的,最熟悉不过了。互联网上关于 Linux 相关的教程和资料也非常的多,但是当你从中筛选出真正对自己有帮助的资料是需要花费很大精力与时间的。

G…

JVM基础(内存结构)

文章目录 内存结构JAVA堆方法区 (Method Area)运行时常量池(Runtime Constant Pool) 虚拟机栈 (Java Virtual Machine Stack)本地方法摘栈(Native Method Stacks)程序计数器…

交易的人生就是对未来不断的挑战!

在这个充满不确定性的市场中,我们每个人都渴望找到一条通往成功的路径。在Eagle Trader交易员中,有一位资深交易者,他不仅对交易有着不同寻常的执着和热爱,而且他的真诚见解和独到的交易哲学,可能会触动你的心弦。他的…

尚硅谷-react教程-求和案例-@redux-devtools/extension 开发者工具使用-笔记

## 7.求和案例_react-redux开发者工具的使用(1).npm install redux-devtools/extension(2).store中进行配置import { composeWithDevTools } from redux-devtools/extension;export default createStore(allReducer,composeWithDevTools(applyMiddleware(thunk)))

src/redux/s…

OpenCV系列教程六:信用卡数字识别、人脸检测、车牌/答题卡识别、OCR

文章目录 一、信用卡数字识别1.1 模板匹配1.2 匹配多个对象1.3 处理数字模板1.4 预处理卡片信息,得到4组数字块。1.5 遍历数字块,将卡片中每个数字与模板数字进行匹配 二、人脸检测2.1人脸检测算法原理2.2 OpenCV中的人脸检测流程 三、车牌识别3.1 安装t…

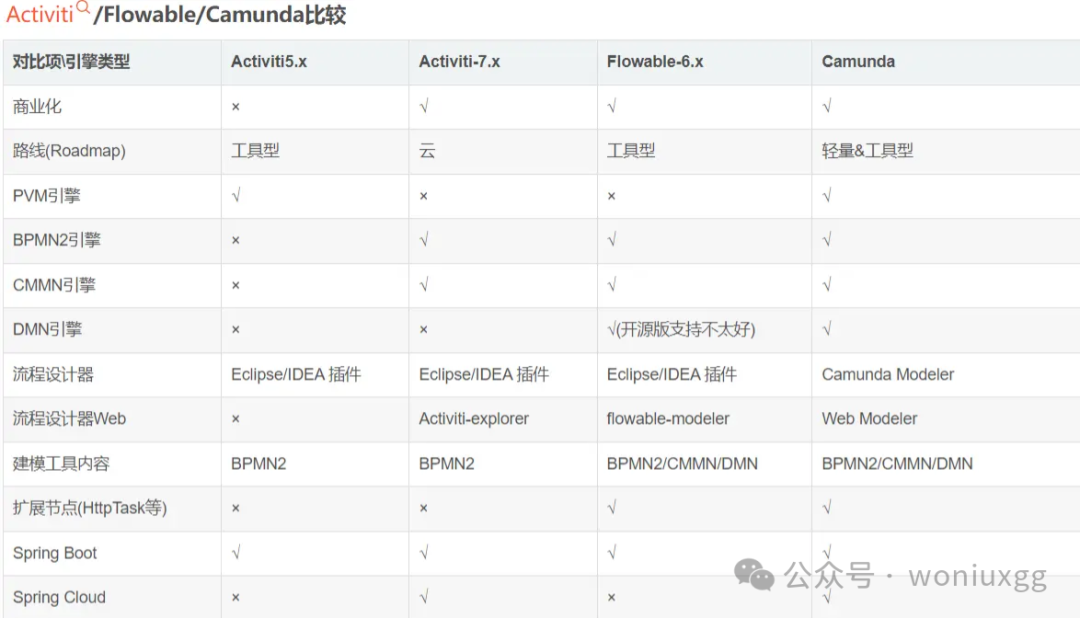

一行代码,实现请假审批流程(Java版)

首先画一个流程图 测试流程图 activiti 项目基础配置 activiti 工作流引擎数据库设计 工作流引擎API 介绍 什么是BPMN流程图 工作流引擎同类对比 继续学习方向 总结 工作流审批功能是办公OA系统核心能力,如果让你设计一个工作流审批系统,你会吗…

SDK5(note中)

在原有SDK5(note上)里的代码上添加了 timer的消息

LRESULT OnCreate(HWND hwnd, UINT uMsg, WPARAM wParam, LPARAM lParam) {OutputDebugString(_T("[11syy]WM_CREATE\n"));//创建一个计时器SetTimer(hwnd, 1, 1000, nullptr);return TRUE;

}LRESULT OnClese(HWND …

全星魅 北斗三号船载终端的优势和领域利用

QM43BS型北斗三号船载终端:开启航海通信与定位新时代 在当今这个信息化高速发展的时代,航海领域对于通信与定位技术的需求愈发迫切。深圳市全民北斗科技有限公司,作为北斗技术应用领域的佼佼者,针对数传通信和位置服务应用&#x…

Python 实现深度学习模型预测控制--预测模型构建

链接:深度学习模型预测控制

链接:WangXiaoMingo/TensorDL-MPC: DL-MPC(deep learning model predictive control) is a software toolkit developed based on the Python and TensorFlow frameworks, designed to enhance the performance of tradition…

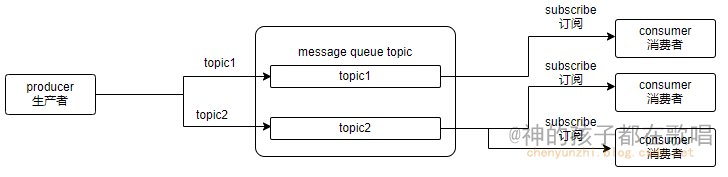

你了解kafka消息队列么?

消息队列概述 一. 消息队列组件二. 消息队列通信模式2.1 点对点模式2.2 发布/订阅模式 三. 消息队列的优缺点3.1 消息队列的优点3.2 消息队列的缺点 四. 总结 前言 这是我在这个网站整理的笔记,有错误的地方请指出,关注我,接下来还会持续更新。 作者&…

Android Junit 单元测试 | 依赖配置和编译报错解决

问题

为什么在依赖中添加了testImplement在build APK的时候还是会报错?是因为没有识别到test文件夹是test源代码路径吗? 最常见的配置有: implementation - 所有源代码集(包括test源代码集)中都有该依赖库.testImplementation - 依赖关系仅在test源代码…

理解磁盘结构---CHS---LAB---文件系统

1,初步了解磁盘

机械磁盘是计算机中唯的一个机械设备,

特点是慢,容量大,价格便宜。 磁盘上面的光面,由数不清的小磁铁构成,我们知道磁铁是有n/s极的,这刚好与二进制的&…

selenium脚本编写及八大元素定位方法

selenium脚本编写

上篇文章介绍了selenium环境搭建,搭建好之后就可以开始写代码了

基础脚本,打开一个网址 from selenium import webdriver driver webdriver.Chrome()#打开chrome浏览器 driver.get(https://www.baidu.com) #打开百度

打开本地HTML文件

上篇…

利用Kubernetes原生特性实现简单的灰度发布和蓝绿发布

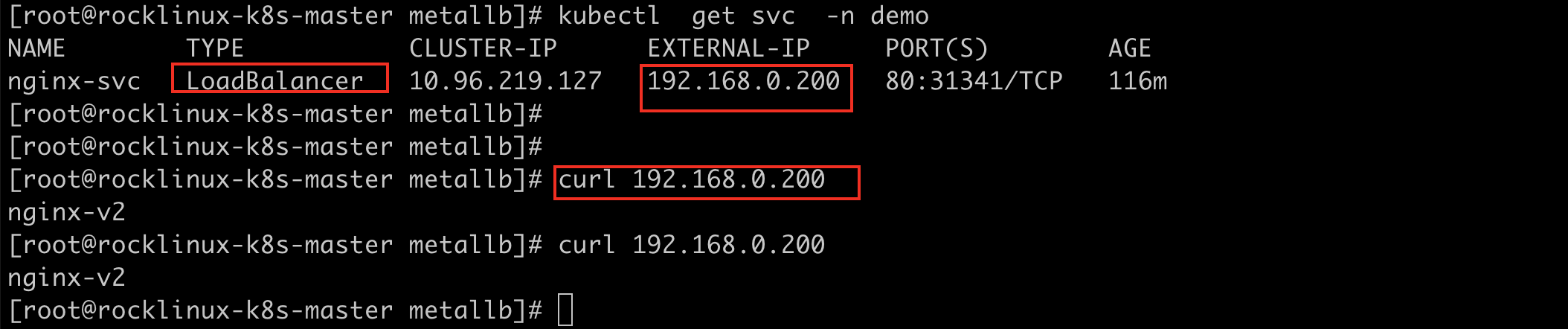

部分借鉴地址: https://support.huaweicloud.com/intl/zh-cn/bestpractice-cce/cce_bestpractice_10002.html 1.原理介绍 用户通常使用无状态负载 Deployment、有状态负载 StatefulSet等Kubernetes对象来部署业务,每个工作负载管理一组Pod。以Deployment为例&#x…

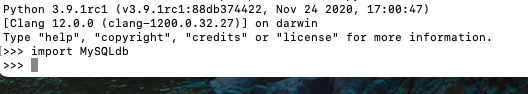

Macos m系列芯片环境下安装python3以及mysqlclient流程以及遇到的一系列问题

最近升级了生产力,换了m3的mbp,迁移项目的时候遇到的一系列python mysqlclient的环境问题,这里总结记录一下。

设备:Macbook Pro m3系统:macos Sonoma 14.6最终成功的python版本:Python3.9.1最终系统环境下…

推荐文章

- 「Python大数据」词频数据渲染词云图导出HTML

- 麻瓜+AI混合工作流试验 5:原创一个方法论,以及AI对中年人的积极一面

- 影视剪辑如何月入1万+?大神教你影视剪辑实操全流程!【覃小龙课堂】

- # linux从入门到精通-从基础学起,逐步提升,探索linux奥秘(九)--网络设置与文件上传下载

- # Redis 入门到精通(八)-- 服务器配置-redis.conf配置与高级数据类型

- #systemverilog# “类”翱翔在systemverilog的天空(Ⅱ)关于理解new() 和 super.new() 函数

- (1) 初识QT5

- (C语言)球球大作战

- (Git)git clone报错——SSL certificate problem: self signed certificate

- (Vite-Vue-Admin)Vue3+vite+element-plus项目功能和问题总结

- (二)MySQL安装与部署(redhat9)

- (二)Ubuntu22.04+Stable-Diffusion-webui AI绘画 中英双语插件安装