Cadence学习

- Cadence内容涵盖

- Cadence主要功能

- Cadence功能模块

- Allegro Design Entry CIS 和 OrCAD Capture CIS 的区别

- Cadence 公司简介

- Allegro Design Entry CIS

- OrCAD Capture CIS

- OrCAD中part和database part区别

- OrCAD中不同页面的连接关系应该怎么处理

- (1)放置Off-Page Connector的操作方法。

- (2)放置Port的操作方法

- OrCAD中Net Alias与Off-Page Connector有什么区别

- OrCAD中总线应该如何命名

- 总线与信号分支线之间应该如何进行连接

- OrCAD为什么有总线的概念(总线如果想要跨页,要使用分页连接符)

- OrCAD中使用Bus总线有哪些注意事项

- OrCAD中ROOM属性的概念

- OrCAD使用注意事项

Cadence内容涵盖

原理图元件库开发、原理图绘制、原理图编辑及后处理、PCB零件库开发、PCB布局、约束设计、PCB布局、PCB布线、铺铜、光绘文件的输出。

Cadence主要功能

电路原理图设计、PCB设计、电路仿真。

Cadence功能模块

- OrCAD Capture CIS:原理图设计工具。

- Design Entry CIS:原理图设计工具。支持多种网表格式输出。

- Design Entry HDL:原理图输入工具。提供原理图输入和分析环境。

- Layout Plus:原OrCA D公司PCB设计工具。很少使用。

- Layout Plus SmartRoute Calibrate:原OrCAD公司Layout Plus的布线工具。

- Library Explorer:数字设计库管理软件,可调用建立的元件符号和模型。

- Model Integrity:器件IBIS及SPICE模型的编辑验证工具。

- Online Documentation:在线帮助文档。

- PCB Editor:印制电路板设计工具。PCB设计中最主要的设计工具。

- PCB Librairan:Allegro库开发管理工具。

- PCB Router:Allegro布线工具。

- PCB SI:Allegro仿真工具。

- Physical Viewer:Allegro的浏览器模块。

- Project Manager:Design Entry HDL的项目管理工具。

- SigXplorer:网络拓扑结构提取、编辑和仿真模块。

- PCB Editor Utilities:小工具箱。

一般使用Design Entry HDL或Design Entry CIS设计电路原理图;使用PCB Editor进行电路板约束设置、布局与布线;使用PCB Router自动布线;使用PCB SI和SigXplorer进行电路仿真;使用Model Integrity管理器件IBIS及SPICE模型。

Allegro Design Entry CIS 和 OrCAD Capture CIS 的区别

Cadence 公司简介

Cadence 公司不像 Alitum 只做电子设计自动化(EDA)设计软件,它旗下有两个产品链,一个是 IC 产品也就是半导体知识产权(IP),一个是电子设计自动化(EDA)软件。而我们说所的原理图和PCB绘制,其实是属于电子设计自动化(EDA)软件下的PCB设计工具范畴的。

其中PCB设计工具又分成PO系列和PS系列,PO中低端系列,也就是OrCAD系列,PS是高端系列,有的人称其为Allegro系列,其实并不准确。

其实OrCAD这个产品线是Cadence收购来的,Allegro才是嫡系。

Allegro Design Entry CIS

Cadence 公司在收购OrCAD之前,它的原理图工具叫Concept HDL,PCB工具就是Allegro,也就是Allegro的PCB Editor,另外还有SI工具(做信号完整性分析的)。

后来收购了以后,为了整合产品线,Cadence以前的Concept HDL,名称改为Design Entry CIS,又同时把Orcad的原理图仿真工具 PSpice AD 和 PSpice AA 整合成一个产品包,并改名为AMS Simulator 。而这些部分就是上面所说的高端产品线(PS)部分。但是该部分依然包含有Capture CIS设计工具。

Concept HDL 更好主要是可定制,但可定制就意味着上手难些,Concept HDL 掌握后用起来很方便,但通用性很差,难以转换使其它软件可用,包括连AutoCAD也不支持。

如果用Concept HDL 做原理图,Allegro 做PCB,原配做搭档,肯定是最好的两个EAD。但是很不好的是 Concept HDL 做原理图想用好就不是那么容易的事情。Concept HDL很难学,上手比较慢,资料少,而且和别的软件很难交互,设置啊什么的都比较复杂,特别是制作一个原理图器件,就特别麻烦,必须和封装对应好,还得提取到封装里的pin号,对应好了才能用,图纸也不如OrCAD美观。但是它很严谨,而且是原配软件,与Allegro交互的时候也麻烦很少。

Concept HDL 软件的通用平台多。

支持的平台有:SOLARIS、Linux/UNIX、BSD 、Windows

OrCAD Capture CIS

原先OrCAD旗下有三个工具,原理图工具Caputre CIS,原理图仿真工具PSpice AD和PSpice AA,还有一款PCB布局布线工具Orcad 的Layout(Plus)。

Cadence收购了OrCAD之后,就完全将Orcad的Capture CIS和Pspice与自身的产品做了无缝整合而摒弃了Orcad以前的Layout(Plus)。目前Cadence的Allegro已经完全作为PCB布线工具整合到OrCAD系列中。

Capture (CIS)是原先的OrCAD原理图工具。 它的PCB工具是Layout。Cadence 买入Orcad之后,把 OrCAD Capture (CIS) 作为一件除了Concept HDL以外的原理图工具(但是它们的原理图库是不可以共用,Allegro的Part Developer提供了这两种库的互转),而它的PCB工具则直接变为Allegro。

Capture(CIS)是应用最广泛的EDA软件(全世界使用率的NO.1),操作性虽差了点,但没有Concept难以转换的缺陷,其它功能并不比Concept少,尤其是可以转换到Mentor,PADS或者是AD。所以它的兼容性要好过Concept HDL。自然而然用Capture(CIS)+ Allegro也不是什么难事。

CIS只支持 Windows

OrCAD中part和database part区别

part是软件自带或者自己封装的元器件,database part是公司内部服务器或者自己搭建的元器件库中的元器件,没有本质区别。

OrCAD中不同页面的连接关系应该怎么处理

对于不同页面的连接关系,我们需要使用添加分页连接符的方式来进行连接。分页连接符有两种,一种是Off-Page Connector,一种是Port,都可以实现不同页面的连接,操作方式如下:

(1)放置Off-Page Connector的操作方法。

第一步,单击菜单命令“Place”→“Off-Page Connector”或“Place”→“Hierarchical Port”,如下图所示,在弹出的界面中进行参数设置。

第二步,在“Off-Page Connector”的设置界面中,分页符的库系统是自带的,在“Libraries”中可以添加自己创建的库,一般情况下用系统自带的即可,一共有两个Symbol,分左右两个方向,根据实际连线情况进行选择,“Name”选项中输入所要连接的网络名即可。

(2)放置Port的操作方法

放置Port的设置情况与Off-Page Connector是类似的,如下图中选择一个Port的类型,然后根据连线方向选择左/右连接符,“Name”选项中输入所要连接的网络名即可。

OrCAD中Net Alias与Off-Page Connector有什么区别

Net Alias与Off-Page Connector都是用于连接网络的标号,它们之间的区别如下:

- Net Alias与Off-Page Connector都可以用于同一页面内的网络连接。

- Off-Page Connector可以用于不同页面之间的网络连接,而Net Alias不能实现此功能。

- 二者是包含关系,Off-Page Connector包含Net Alias的功能,一般情况下,平坦式的原理图中都是同页面内的网络使用Net Alias或者连线的方式进行连接,不同页面内的网络使用Off-Page Connector进行连接。

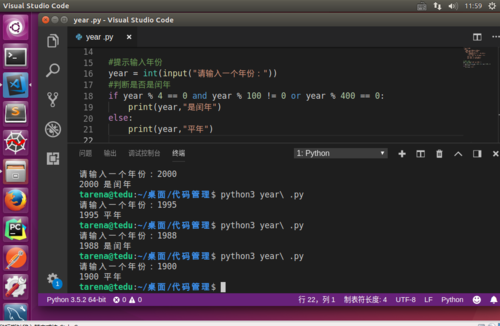

OrCAD中总线应该如何命名

在前面的问答中,我们已经创建好了总线,创建好总线以后,我们需要在总线上放置总线的名称,也就是网络标号,按照网络一一对应。总线的命名方式如下:

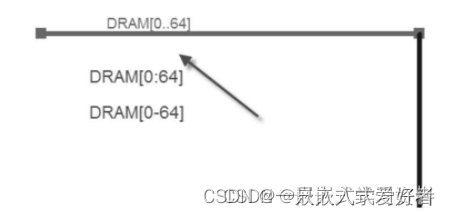

- Busname[0:64],其中,Busname是总线名称,0到64是总线中包含的分支数目。

- Busname[0…64],其中,Busname是总线名称,0到64是总线中包含的分支数目。

- Busname[0-64],其中,Busname是总线名称,0到64是总线中包含的分支数目。

在命名总线时,放置的是网络标号Net Alias,单击菜单命令“Place”→“Net Alias”或者按快捷键“N”进行放置,如图3-27所示,放置时有以下三个方面注意事项:

- 一是总线名称与中括号之间不能出现空格,不然无法进行连接。

- 二是总线名称不能以数据结尾,例如Busname0、Busname1这类的名称是不允许的,系统不能识别。

- 三是总线上放置好网络标号以后,双击总线,可以查看属性,是有Name属性的,如下图所示。

总线与信号分支线之间应该如何进行连接

- 第一步,放置总线入口“Bus Entry”,单击菜单命令“Place”→“Bus Entry”或者按快捷键“E”来进行放置。

- 第二步,“Bus Entry”会悬挂在鼠标上,按快捷“R”可以进行旋转,选择好正确的方向,然后放置到总线上,与总线进行连接。

- 第三步,在放置“Bus Entry”时,放置好一个以后,按快捷键“F4”可以进行快速放置,也可按住“Ctrl”键,用鼠标拖动来进行快速放置。

- 第四步,放置好“Bus Entry”以后,需要做的就是将每一个信号的分支连线与总线入口连接上,使用Wire连线的方式先将一根信号线连上总线入口,然后在Wire连线上放置上网络标号,网络标号命名方式要与总线保持一致。

- 第五步,放置好一根以后,可以直接按快捷键“F4”进行快速放置,或者是按住“Ctrl”键,鼠标选中Wire线进行拖动,连接其他信号线,Wire连线上的网络标号也会按照命名方式进行递增,这样就能快速地将总线与分支连线连接好。

OrCAD为什么有总线的概念(总线如果想要跨页,要使用分页连接符)

有时候,灵活往往意味着不规范,容易出错。比如在Altium Designer中,默认情况下net是全局变量,不同页中的相同net是连在一起的,那么再使用分页连接符又有什么必要呢。反观OrCAD,有分页连接符,就强制用户使用分页连接符在不同页之间连接(电源类全局变量除外),这样看到一个net,如果没有和分页连接符相连,很容易知道这个net只在该原理图页中出现,容易看出net结构。不然的话,还得担心其他页也有这个net,不方便了解电路结构。

OrCAD中使用Bus总线有哪些注意事项

在OrCAD中使用Bus总线的时候,有以下几个注意事项:

- 总线不是强制使用的,不使用总线也是可以的,使用总线构架会使原理图更加清晰,分析原理图更加透彻。

- 总线与信号分支线之间的连线只能通过网络标号Net Alias来进行电气连接,否则是连接不上的。

- 如果不使用总线入口Bus Entry来进行连接,直接将信号分支线连接到总线上也会显示连接点,但是这样信号线与总线并没有真正连接上,一定要通过Bus Entry的方式来连接总线与信号分支线。

- 总线的命名方式一定要按照前面问答中所要求的那样,三种命名方式任选一种,然后使信号分支线的网络标号的命名方式与总线的保持一致,如总线的命名方式为DQ[0:64],那么分支信号线则为DQ0、DQ1、DQ2……依次递增。

- 若两段总线形成T形连接,则自动放置连接点,电气上是互连的。两段十字形的总线默认没有连接点,要形成电气互连,必须手动放置连接点。

OrCAD中ROOM属性的概念

将一个或一些元件定义在一个ROOM的好处是,在进行PCB布局时可以按ROOM定义摆放元件,从而大大提高摆放效率。

OrCAD使用注意事项

- 多部分元器件中,对于homogeneous类型元器件,元器件每个部分一样,对于heterogeneous类型元器件,元器件每个部分不一样。

- crtl+insert 复制,shift+insert 粘贴

- off-page connector分页符,连接不同页原理图信号

- 快捷键不分大小写

- bus entry表示bus的分支连接线,总线也需要跨页连接符

- reference表示位号,tol为精度属性

- room属性用于pcb布局按room定义摆放元件

- 显示不全需要安装补丁

- 双击元器件属性,new property新建新属性,pivot表示横向显示

- ORCAD通过封装名称来匹配pcb footprint封装,原理图库和pcb库分来的,原理图库中新建元器件时可以先view package