1.实验目的及要求

1.1实验目的

1)了解双端口静态随机存储器IDT7132的工作特性及使用方法。

2)了解半导体存储器怎样存储和读出数据。

3)了解双端口存储器怎样并行读写,并分析冲突产生的情况。

1.2实验要求

1)做好实验预习,掌握IDT7132双端口存储器的功能特性和使用方法。

2)完成实验任务,根据实验结果填写实验二数据表。

3)写出实验报告,分析实验结果并简述心得体会。

2.实验步骤

1)按电路图要求,将有关控制信号和二进制开关对应接好。

| 存储器 | SBUS | ARINC | LAR | MEMW | MBUS | PCINC | LPC | ABUS |

| 电平开关 | K0 | K1 | K2 | K3 | K4 | K5 | K6 | GND |

2)接通电源,设置操作模式:DP和SW为“1110”,含义为单步,存储器实验。将编程开关拨到“正常”位置,控制转换开关拨到“独立”位置。按CLR按钮,使TEC-8实验系统处于初始状态。

3)将10H写入AR:为输入数据,需把数据开关拨至10H,打开SBUS;为把数据写入AR中,需打开LAR;然后按下QD即可。

4)将85H写入地址为10H的单元:为输入数据,需把数据开关拨至85H,打开SBUS;为把数据写入存储器中指定单元,需打开MEMW。下一次数据要输入地址为11H的单元,为了为下一次输入数据准备地址,需打开ARINC,使AR+1;最后按下QD即可。接下来的存入数据方法类似。

5)将10H写入PC,与将10H写入AR类似。

6)从IR指示灯读出数据:因为控制信号LIR默认为1,故按下QD即可读出。但为了连续读出,需打开PCINC让PC+1。

3.实验内容

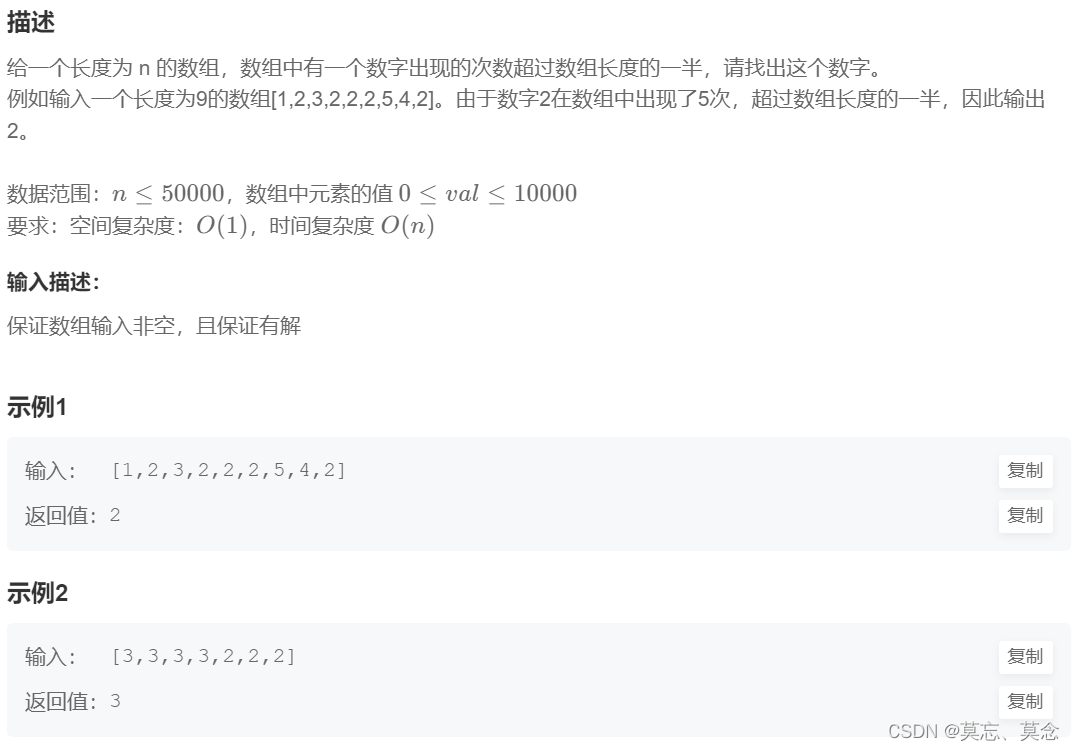

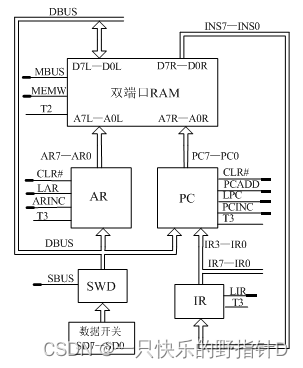

1)双端口RAM可以同时进行读、写或是双端口同时读。

2)实验系统中,左端口配置成读、写端口,用于程序的初始装入操作、从存储器取数操作、将总线DBUS上的数写入存储器操作。(当MBUS信号为1时,AR7~AR0指定单元的数据送数据总线DBUS)

3)实验系统中,右端口配置成只读方式,从PC7~PC0指定的单元读出指令INS7~INS0,送往指令寄存器IR。指令寄存器IR保存要执行的指令代码,但在本实验中仅作显示存储器指定地址读数所用,故读出结果应被看成数据而非指令。当信号LIR为1时,在T3的上升沿,将从RAM右端口读出的指令写入IR,本实验中LIR默认为1。

4)地址寄存器AR向RAM左端口提供地址AR7~AR0。当复位信号CLR#为0时,AR复位为00H;当信号LAR为1时,在T3上升沿,将总线DBUS上的信息写入AR;当控制信号MEMW为1时,在T2时刻将总线上数据或指令写入AR7~AR0指定的存储单元;当信号ARINC为1时,在T3上升沿完成AR加1。

5)程序计数器PC向RAM右端口提供地址PC7~PC0。当复位信号CLR#为0时,PC复位为00H;当信号LPC为1时,在T3上升沿,将总线DBUS上的信息写入PC;当信号PCINC为1时,在T3上升沿完成PC加1。

6)数据开关SD7~SD0用于设置RAM的地址和数据。当信号SBUS为1时,数据开关值送往数据总线DBUS。

本实验线路与信号原理图如下:

本实验用到的信号归纳如下:

| 名称 | 功能说明 |

| D7~D0 | 数据总线DBUS上的数。 |

| PCINC | =1时,在T3的上升沿PC加1。 |

| AR7~AR0 | 双端口RAM左端口存储器地址。 |

| ARINC | =1时,在T3的上升沿,AR加1。 |

| PC7~PC0 | 双端口RAM右端口存储器地址。 |

| SBUS | =1时,数据开关SD7~SD0的数送数据总线DBUS。 |

| MBUS | =1时,将双端口RAM的左端口数据送到数据总线DBUS。 |

| INS7~INS0 | 从双端口RAM右端口读出的指令,本实验中作为数据使用。 |

| LAR | =1时,在T3的上升沿,将数据总线DBUS上的D7~D0写入地址寄存器AR。 |

| LPC | 当它为1时,在T3的上升沿,将数据总线DBUS上的D7~D0写入程序计数器PC。 |

| MEMW | =1时,在T2为1期间将数据总线DBUS上的D7~D0写入双端口RAM,写入的存储器单元由AR7~AR0指定。 |

| LIR | =1时(默认),在T3的上升沿将从双端口RAM的右端口读出的指令INS7~INS0写入指令寄存器IR。读出的存储器单元由PC7~PC0指定。 |

4.实验结果

1)控制转换开关拨到独立位置;

2)编程开关拨到正常位置;

3)操作模式:1110;

4)控制信号开关接线。

| 存储器 | SBUS | ARINC | LAR | MEMW | MBUS | PCINC | LPC | ABUS |

| 电平开关 | K0 | K1 | K2 | K3 | K4 | K5 | K6 | GND |

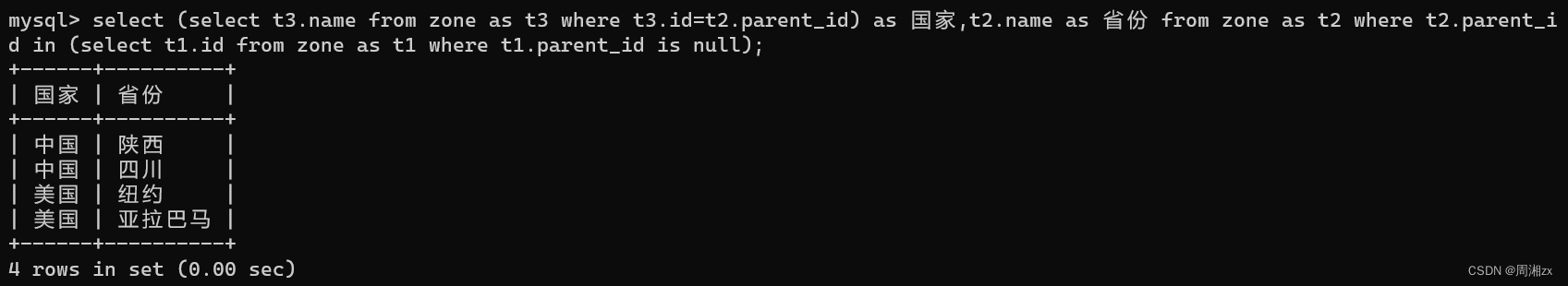

向存储器的10H~12H的单元依次写入85H、60H、38H,再读出验证。

| 序号 | SBUS | ARINC | LAR | MEMW | MBUS | PCINC | LPC | SD | QD | AR7~ AR0 | PC7~ PC0 | IR7~0 INS7~0 | 功能 |

| K0 | K 1 | K2 | K 3 | K 4 | K 5 | K6 | |||||||

| 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 10 | √ | 10 | × | × | 置AR =10 |

| 2 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 85 | √ | 11 | × | × | 写第1个数85 |

| 3 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 60 | √ | 12 | × | × | 写第2个数60 |

| 4 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 38 | √ | 13 | × | × | 写第3个数38 |

| 读出存储器10H开始的三个单元内容 | |||||||||||||

| 5 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 10 | √ | × | 10 | 85 | 重置PC PC=10,INS=IR=85 |

| 6 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | ╳ | √ | × | 11 | 60 | PC=11,INS=IR =60 |

| 7 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | ╳ | √ | × | 12 | 38 | PC=12,INS=IR =38 |

| 8 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | ╳ | √ | × | 13 | × | 13H单元为随机数 |

实验报告: 【免费】计算机组成原理实验-双端口存储器原理资源-CSDN文库

![[HDLBits] Exams/2012 q1g](https://hdlbits.01xz.net/mw/thumb.php?f=Exams_2012q1g.png&width=195)