| FMCJ450-基于ADRV9009的双收双发射频FMC子卡 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ADRV9009子卡 设计原理图:FMCJ450-基于ADRV9009的双收双发射频FMC子卡 便携测试设备

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.rhkb.cn/news/111411.html

如若内容造成侵权/违法违规/事实不符,请联系长河编程网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

基于亚马逊云科技无服务器服务快速搭建电商平台——部署篇

受疫情影响消费者习惯发生改变,刺激了全球电商行业的快速发展。除了依托第三方电商平台将产品销售给消费者之外,企业通过品牌官网或者自有电商平台销售商品也是近几年电商领域快速发展的商业模式。独立站电商模式可以进行多方面、全渠道的互联网市场拓展…

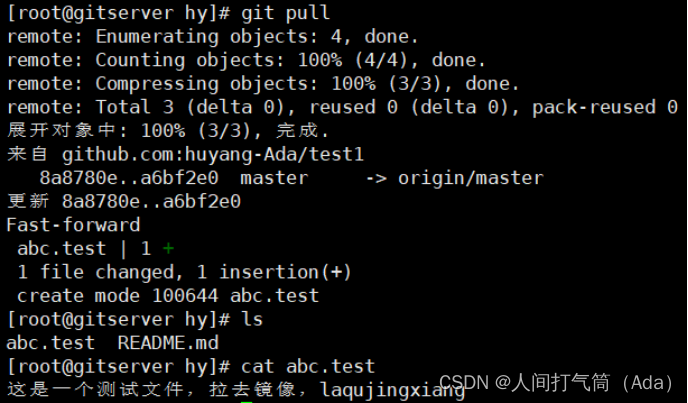

Git分布式版本控制系统与github

第四阶段提升

时 间:2023年8月29日

参加人:全班人员

内 容:

Git分布式版本控制系统与github 目录

一、案例概述

二、版本控制系统

(一) 本地版本控制

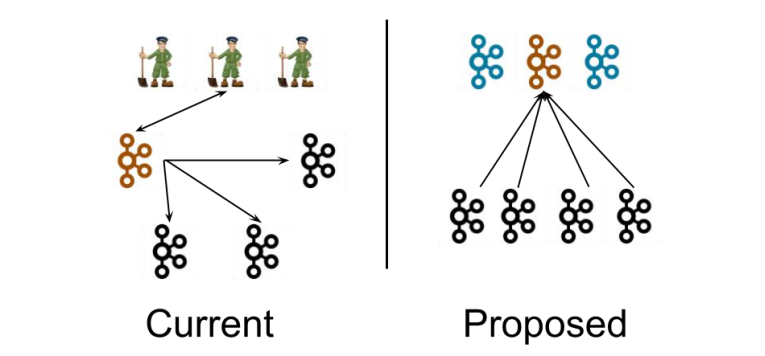

(二)集中化的版本控制系统

&…

DP读书:鲲鹏处理器 架构与编程(十三)操作系统内核与云基础软件

操作系统内核与云基础软件 鲲鹏软件构成硬件特定软件 鲲鹏软件构成硬件特定软件1. Boot Loader2. SBSA 与 SBBR3. UEFI4. ACPI 操作系统内核Linux系统调用Linux进程调度Linux内存管理Linux虚拟文件系统Linux网络子系统Linux进程间通信Linux可加载内核模块Linux设备驱动程序Linu…

Vue 项目性能优化 — 实践指南

前言

Vue 框架通过数据双向绑定和虚拟 DOM 技术,帮我们处理了前端开发中最脏最累的 DOM 操作部分, 我们不再需要去考虑如何操作 DOM 以及如何最高效地操作 DOM;但 Vue 项目中仍然存在项目首屏优化、Webpack 编译配置优化等问题,所…

自然语言处理(四):全局向量的词嵌入(GloVe)

全局向量的词嵌入(GloVe)

全局向量的词嵌入(Global Vectors for Word Representation),通常简称为GloVe,是一种用于将词语映射到连续向量空间的词嵌入方法。它旨在捕捉词语之间的语义关系和语法关系&#…

Python小知识 - Python中的多线程

Python中的多线程 线程是进程中的一个执行单元,是轻量级的进程。一个进程可以创建多个线程,线程之间共享进程的资源,比如内存、文件句柄等。 在Python中,使用threading模块实现线程。 下面的代码创建了两个线程,一个输…

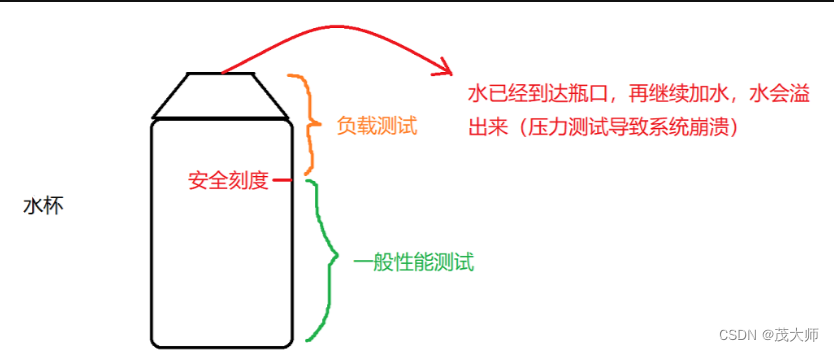

2023.8.29 关于性能测试

目录 什么是性能测试?

性能测试常见术语及其性能测试衡量指标

并发

用户数

响应时间

事务

点击率

吞吐量

思考时间

资源利用率 性能测试分类

基准性能测试

负载性能测试

压力性能测试

可靠性性能测试

性能测试执行流程 什么是性能测试? 性…

实用的面试经验分享:程序员们谈论他们的面试历程

🌷🍁 博主猫头虎 带您 Go to New World.✨🍁 🦄 博客首页——猫头虎的博客🎐 🐳《面试题大全专栏》 文章图文并茂🦕生动形象🦖简单易学!欢迎大家来踩踩~🌺 &a…

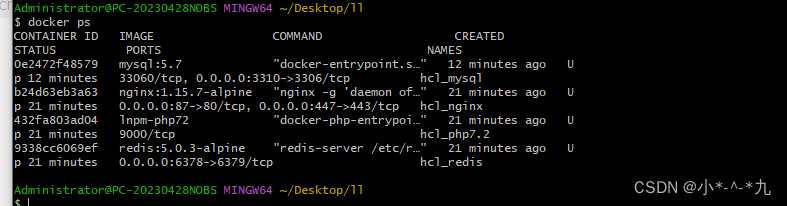

docker 学习-- 04 实践2 (lnpmr环境)

docker 学习 系列文章目录

docker 学习-- 01 基础知识

docker 学习-- 02 常用命令

docker 学习-- 03 环境安装

docker 学习-- 04 实践 1(宝塔)

docker 学习-- 04 实践 2 (lnpmr环境) 文章目录 docker 学习 系列文章目录1. 配…

财务数据分析?奥威BI数据可视化工具很擅长

BI数据可视化工具通常是可以用户各行各业,用于不同主题的数据可视化分析,但面对财务数据分析这块难啃的骨头,能够好好地完成的,还真不多。接下来要介绍的这款BI数据可视化工具不仅拥有内存行列计算模型这样的智能财务指标计算功能…

flutter 上传图片并裁剪

1.首先在pubspec.yaml文件中新增依赖pub.dev

image_picker: ^0.8.75 image_cropper: ^4.0.1

2.在Android的AndroidManifest.xml文件里面添加权限

<activityandroid:name"com.yalantis.ucrop.UCropActivity"android:screenOrientation"portrait"andro…

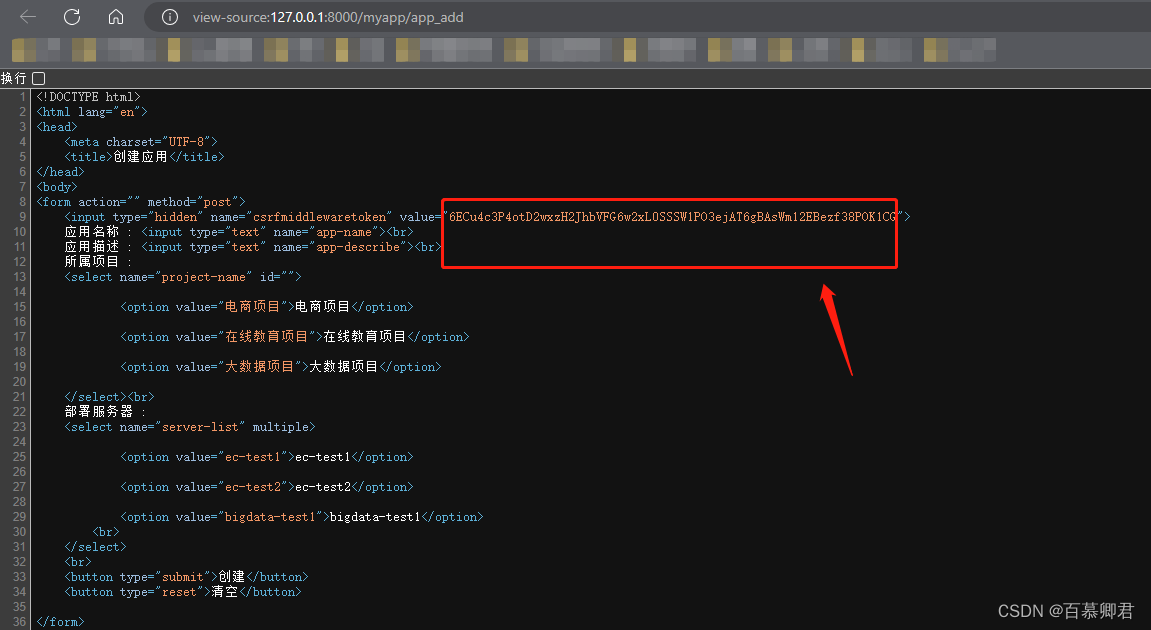

Django基础7——用户认证系统、Session管理、CSRF安全防护机制

文章目录 一、用户认证系统二、案例:登陆认证2.1 平台登入2.2 平台登出2.3 login_required装饰器 三、Django Session管理3.1 Django使用Session3.1.1 Cookie用法3.1.2 Session用法 3.2 案例:用户登录认证 四、Django CSRF安全防护机制 一、用户认证系统…

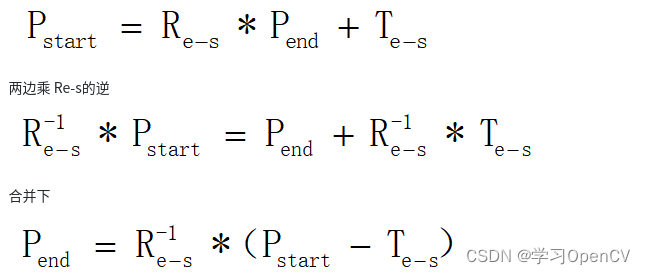

3d激光slam建图与定位(2)_aloam代码阅读

1.常用的几种loam算法 aloam 纯激光 lego_loam 纯激光 去除了地面 lio_sam imu激光紧耦合 lvi_sam 激光视觉 2.代码思路 2.1.特征点提取scanRegistration.cpp,这个文件的目的是为了根据曲率提取4种特征点和对当前点云进行预处理 输入是雷达点云话题 输出是 4种特征点…

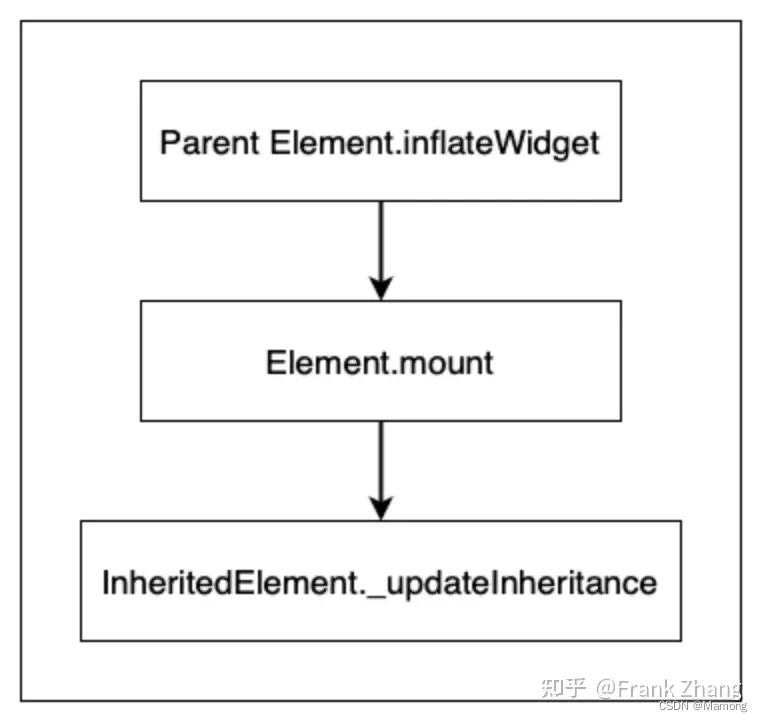

透过源码理解Flutter InheritedWidget

InheritedWidget的核心是保存值和保存使用这个值的widget,通过对比值的变化,来决定是否要通知那些使用了这个值的widget更新自身。

1 updateShouldNotify和notifyClients

InheritedWidget通过updateShouldNotify函数控制依赖其的子组件是否在Inherited…

vue cli构建的项目出现 Uncaught runtime errors

使用 vue/cli 脚手架构建的项目,在 npm run dev 运行后,页面出现 Uncaught runtime errors 报错遮罩层,如下图所示。 报错原因

这种错误通常是运行时出的问题,可能是网络错误,可能是变量未定义等等。 这种错误默认在开…

七、Kafka-Kraft 模式

目录 7.1 Kafka-Kraft 架构7.2 Kafka-Kraft 集群部署 7.1 Kafka-Kraft 架构 左图为 Kafka 现有架构,元数据在 zookeeper 中,运行时动态选举 controller,由controller 进行 Kafka 集群管理

右图为 kraft 模式架构(实验性ÿ…

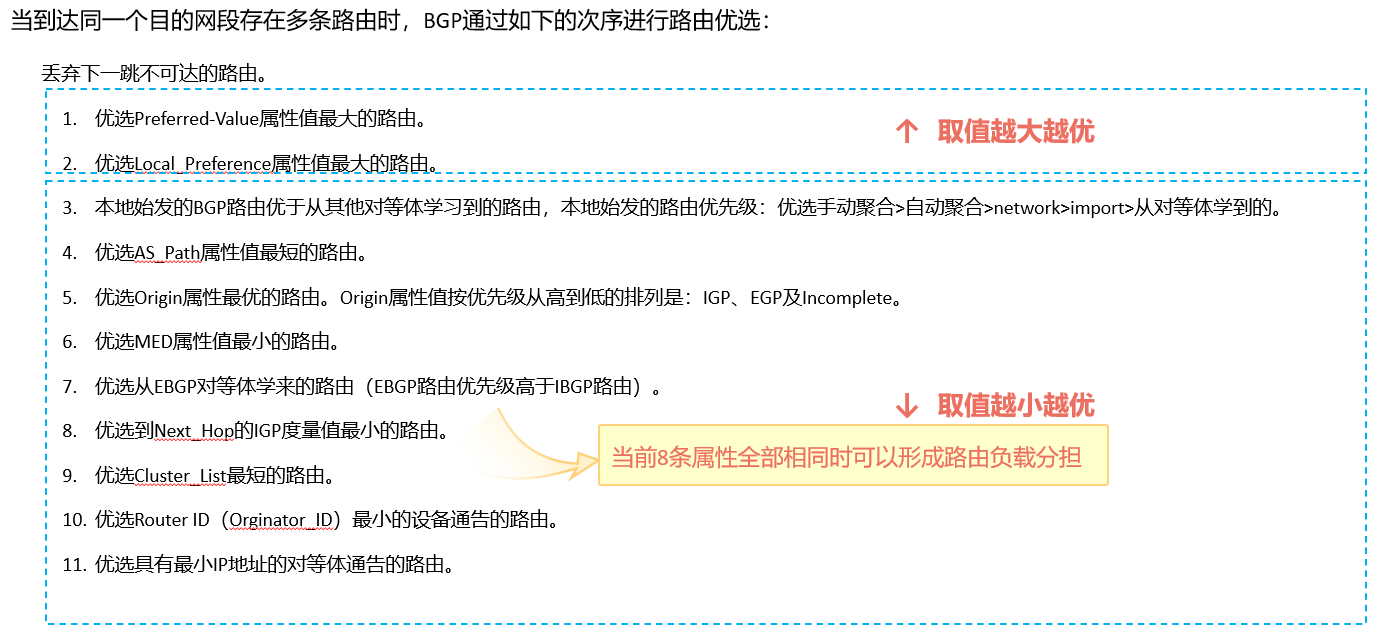

华为数通方向HCIP-DataCom H12-821题库(单选题:161-180)

第161题

以下关于 URPF(Unicast Reverse Path Forwarding) 的描述, 正确的是哪一项

A、部署了严格模式的 URPF,也能够可以同时部署允许匹配缺省路由模式

B、如果部署松散模式的 URPF,默认情况下不需要匹配明细路由

C、如果部署松散模式的…

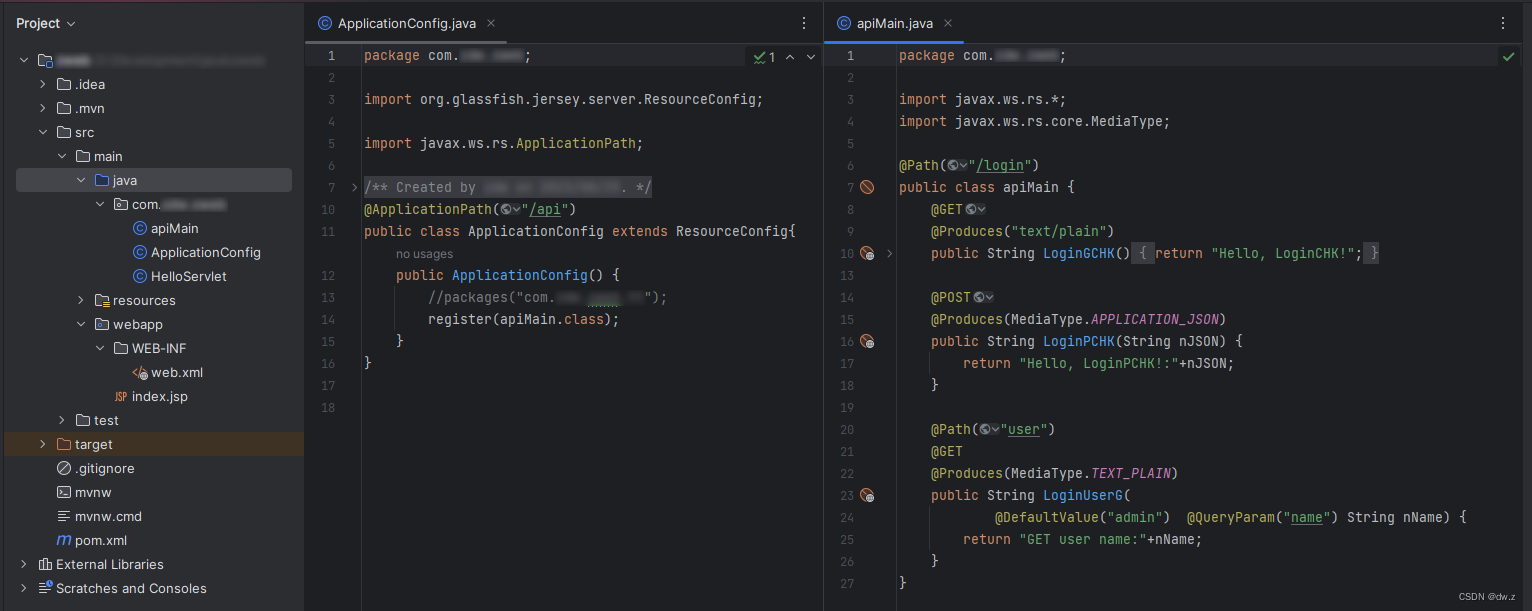

Java IDEA Web 项目 1、创建

环境: IEDA 版本:2023.2 JDK:1.8 Tomcat:apache-tomcat-9.0.58 maven:尚未研究 自行完成 IDEA、JDK、Tomcat等安装配置。

创建项目:

IDEA -> New Project

选择 Jakarta EE Template:选择…

RT-Thread在STM32硬件I2C的踩坑记录

RT-Thread在STM32硬件I2C的踩坑记录 0.前言一、软硬件I2C区别二、RT Thread中的I2C驱动三、尝试适配硬件I2C四、i2c-bit-ops操作函数替换五、Attention Please!六、总结 参考文章: 1.将硬件I2C巧妙地将“嫁接”到RTT原生的模拟I2C驱动框架 2.基于STM32F4平台的硬件I…

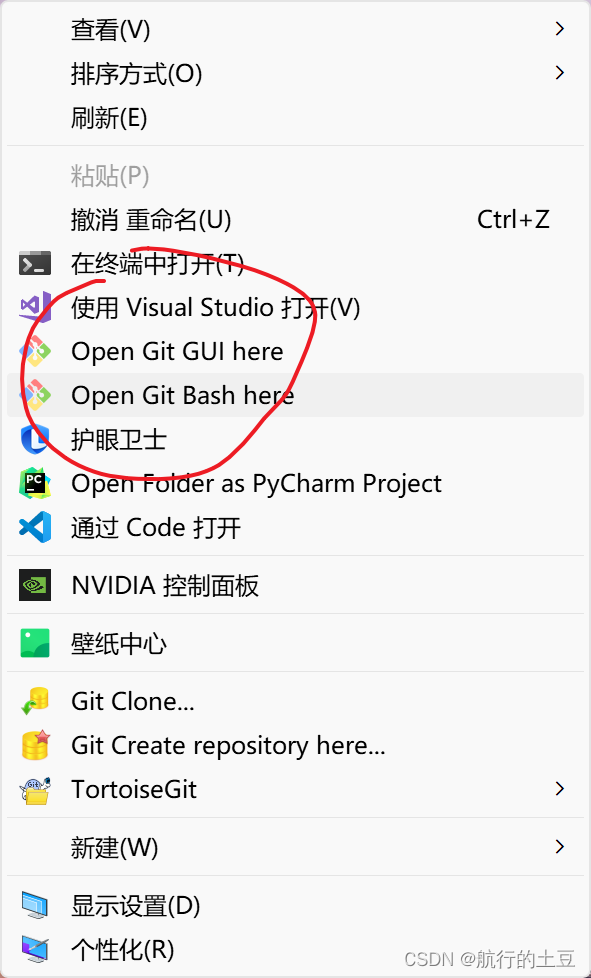

Git小白入门——了解分布式版本管理和安装

Git是什么?

Git是目前世界上最先进的分布式版本控制系统(没有之一) 什么是版本控制系统?

程序员开发过程中,对于每次开发对各种文件的修改、增加、删除,达到预期阶段的一个快照就叫做一个版本。 如果有一…

最新文章

- 真实可以赚钱提现的游戏/江苏搜索引擎优化

- 网站建设亿码酷专注/手机如何制作网站

- 网站开发工具的功能包括HTML或/网盘搜索引擎入口

- 福州企业公司网站建设/google关键词查询工具

- ngix安装wordpress的伪静态/网络seo软件

- 建论坛网站需要多少空间/品牌营销的概念

- 黑马Java面试教程_P8_并发编程

- 混合开发环境---使用编程AI辅助开发Qt

- ubuntu22.04 nginx配置下载目录,亲测成功

- 【从零开始入门unity游戏开发之——C#篇21】C#面向对象的封装——`this`扩展方法、运算符重载、内部类、`partial` 定义分部类

- android EditText密码自动填充适配

- ubuntu22.04.5本地apt源部署

推荐文章

- # Go学习-Day9

- #渗透测试#漏洞挖掘#红蓝攻防#护网#sql注入介绍03-SQL注入联合查询注入(Union-Based SQL Injection)

- (1)Jupyter Notebook 下载及安装

- (2)STM32单片机上位机

- (9)数据分析-相关性分析

- (k8s)Kubernetes本地存储接入

- (八)、基于 LangChain 实现大模型应用程序开发 | 基于知识库的个性化问答 (检索 Retrieval)

- (二)Apache log4net™ 手册 - 配置

- (二)激光线扫描-相机标定

- (二)结构型模式:7、享元模式(Flyweight Pattern)(C++实例)

- (高阶) Redis 7 第17讲 分布式锁 实战篇

- (简单成功)Mac:命令设置别名