ARM属于RISC体系,许多指令单周期指令,是32位读取/存储架构,对内存访问是32位,Load and store的架构,只有寄存器对内存,不能内存对内存存储,CPU通过寄存器对内存进行读写操作。

ARM的寻址空间是线性地址空间,典型的32位地址下,空间大小为232 = 4G.

注:X86 寻址是段+偏移量

1.数据类型

字节类型(Byte):数据宽度为8bits

半字节类型(Halfword):数据宽度为16bits,存取时一般要求为2字节对齐。

字数据类型(Word):数据宽度为32bits,存取时一般要求4字节对齐

2.数据对齐

在V6架构之前,数据访问都必须针对要访问的大小把访问的地址进行对齐,没有对齐的地址将会导致出现“数据中止”异常(在数据存取或指令预取时都可能出现)。

没有对齐的地址数据可以通过多个对齐地址数据以为/掩码操作来实现。

ARM V6架构添加了新的硬件来支持未对齐的数据访问。

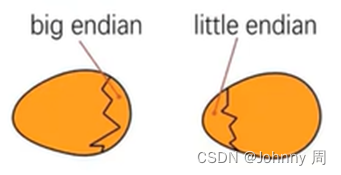

3.数据存储的大小端问题

大小端问题时指数据在计算机内存中的字节顺序问题,它决定了寄存器的内容和内存内容的格式关联。

ARM寄存器时字宽,就是4字节。而内存寻址是按照字节顺序的。

采用大端方式符合人类的正常思维,小端方式有利于计算机处理,无优劣之分。

ARM支持大端(Big-endian)和小端(Little-endian)的内存数据方式,可以通过硬件的方式设置端模式,也可以通过软件的方式来设置(V6版本以上)

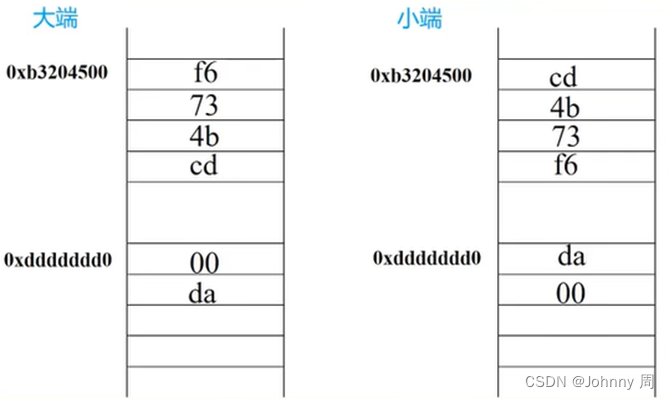

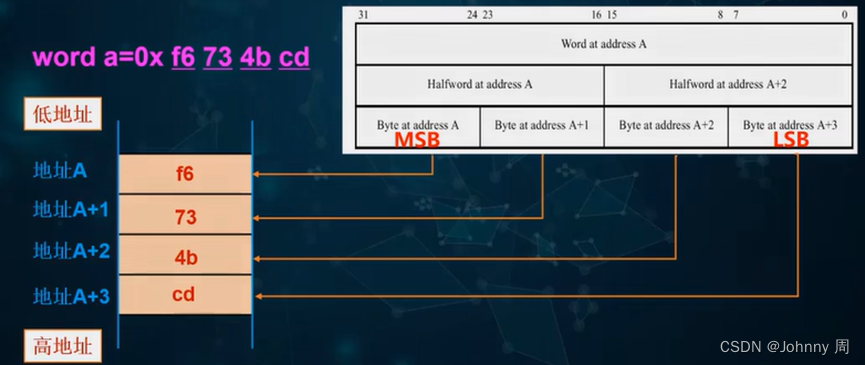

大端格式(Big-endian)

最低地址是该数据的地址(A)

最高有效字节(MSB, Most Signifcant Byte) 放内存低地址(A)

最低有效字节(LSB,Least Significant Byte)放内存高地址(A+3)

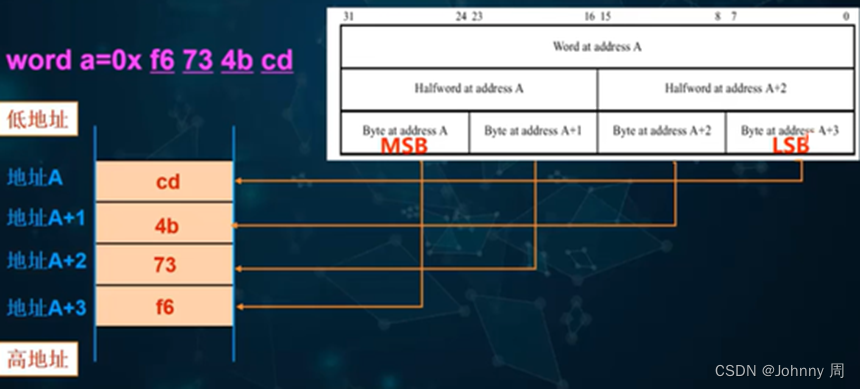

小端格式(Little-endian)

最低地址是该数据的地址(A)

最高有效字节(MSB, Most Signifcant Byte) 放内存高地址(A+3)

最低有效字节(LSB,Least Significant Byte)放内存低地址(A)

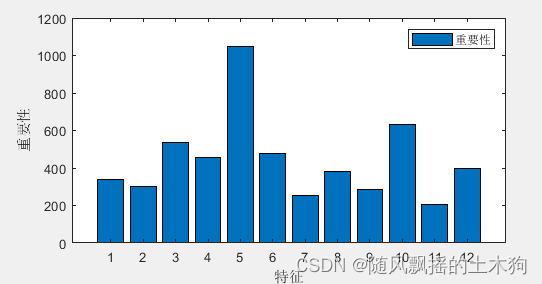

大小端具体实例

变量A:Word A = 0x f6 73 4b cd,在内存中的起始地址为0xb3 20 45 00

变量B:half word B= 218,在内存中的起始地址为0x dd dd dd d0