AD9371 系列快速入口

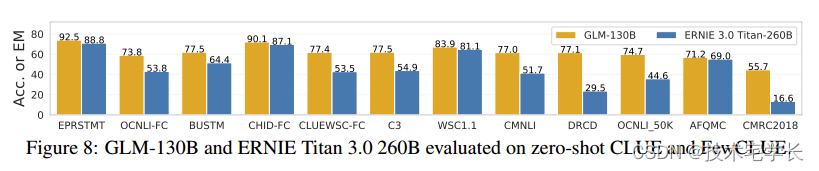

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成(一)

JESD204B相关IP端口信号 : AD9371 官方例程HDL JESD204B相关IP端口信号

裸机程序配置 AD9528、AD9371、FPGA IP 和主函数梳理: AD9371 官方例程裸机SW 和 HDL配置概述(一)

裸机程序配置 AD9528、AD9371、FPGA IP 和主函数梳理: AD9371 官方例程裸机SW 和 HDL配置概述(二)

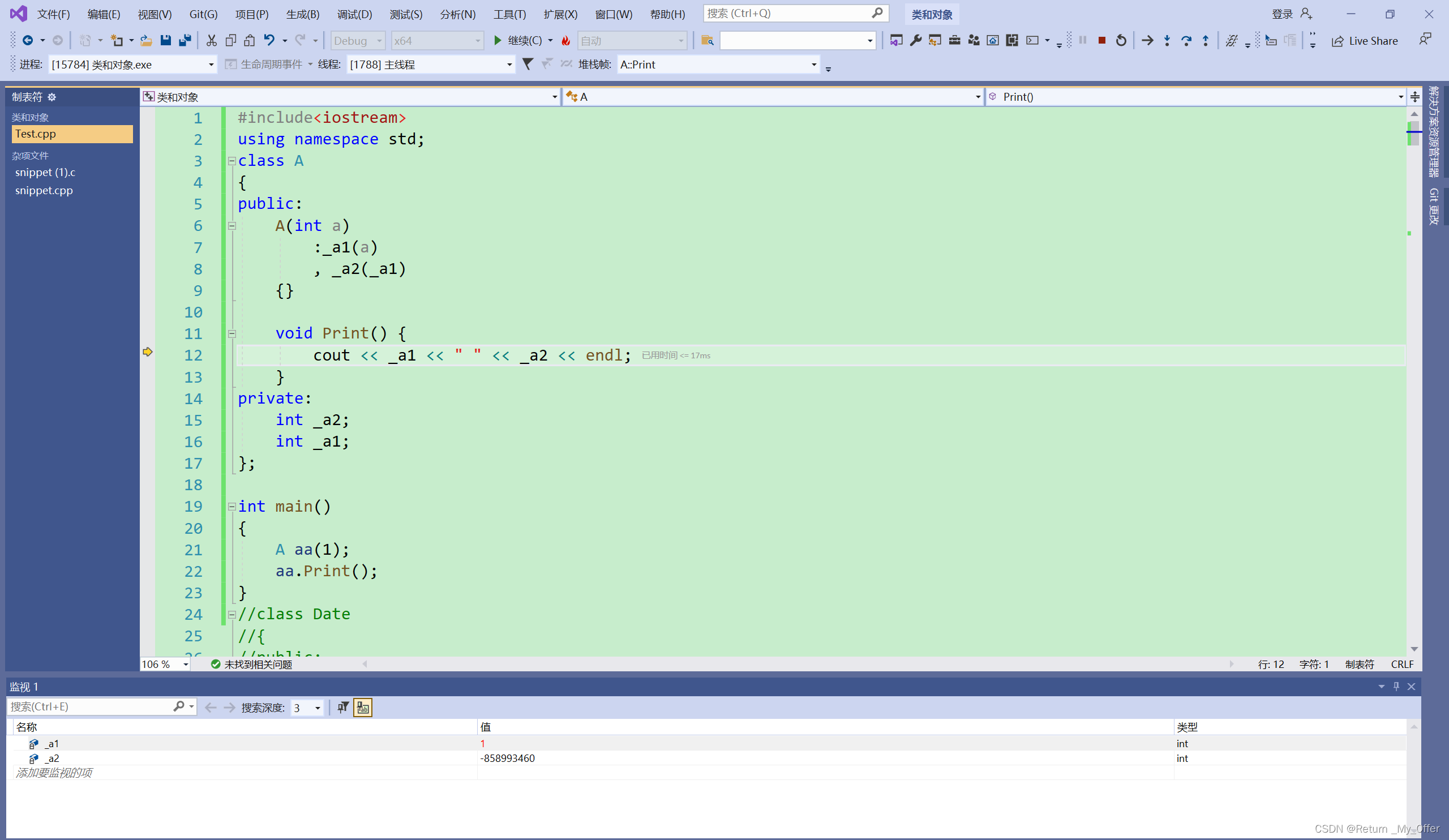

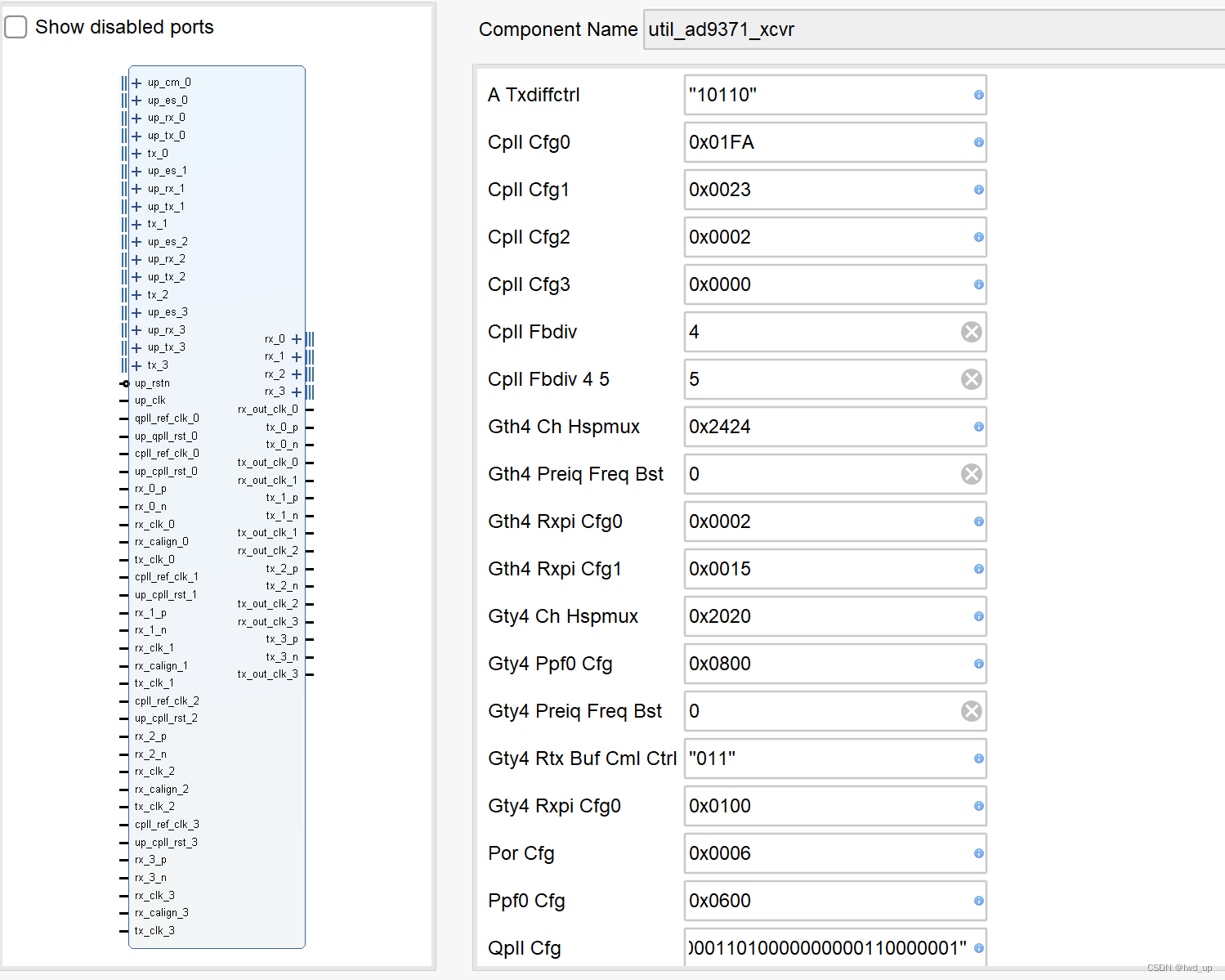

继续上一讲 AD9371 官方例程裸机SW 和 HDL配置概述(二)内容,重点讲解 util_ad9371_xcvr IP 和 axi_ad9371_tx_clkgen 配置

大部分参数不需要修改, 重要的参数如 TX_OUT_DIV 、QPLL_FBDIV、TX_CLK25_DIV等 ,后续可以通过DRP 重配置,而 num of Lane 等参数 需要正确配置,以例化正确数量的通道

主函数见下一节

文章目录

- util_ad9371_xcvr

- axi_ad9371_tx_clkgen

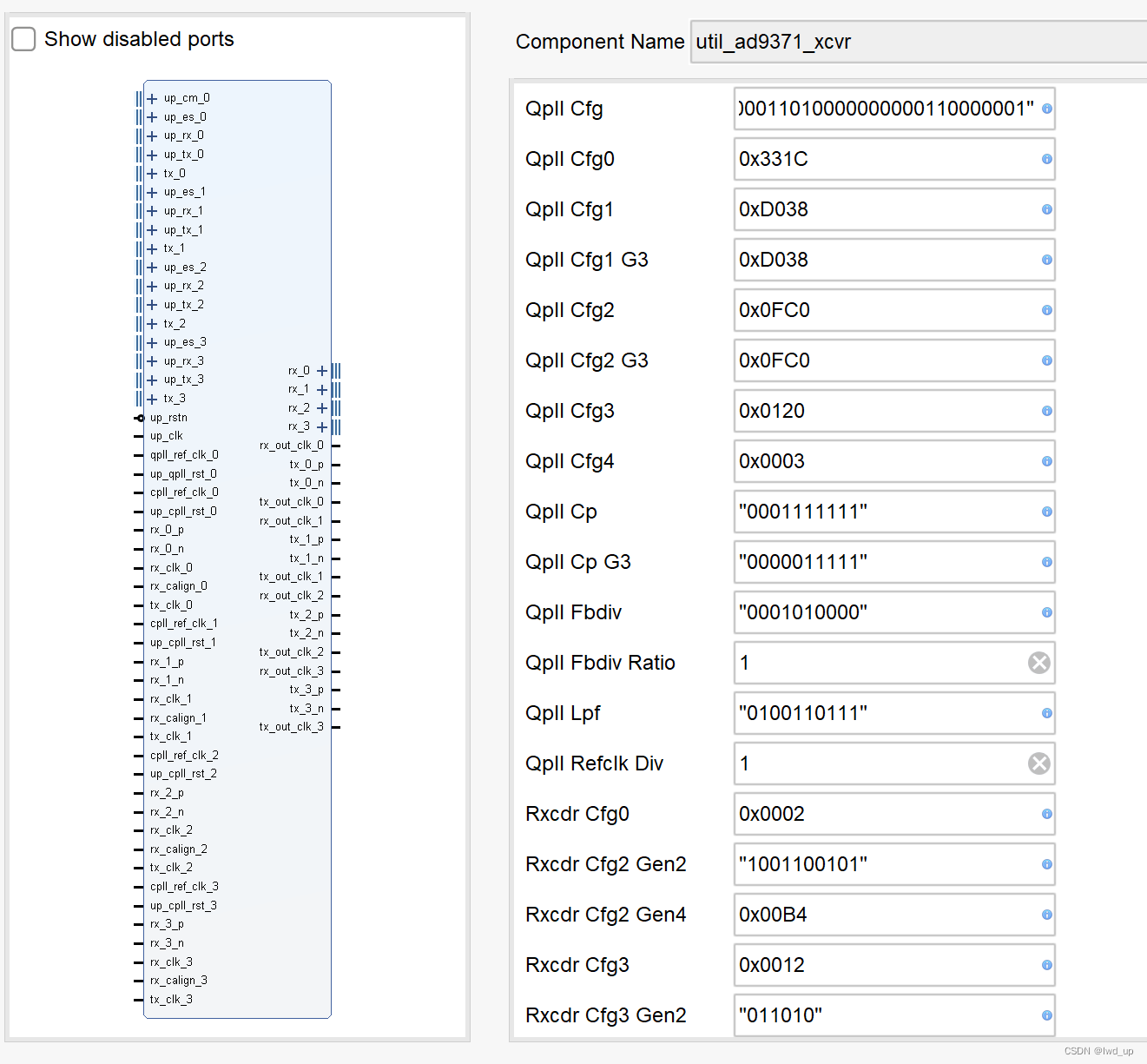

util_ad9371_xcvr

TX

TX_NUM_OF_LANES = 4, TX使用的 LANE 通道 ,便于确定后续COMMON 和 Channel 例化数目

TX_OUT_DIV = 2, 初始化 TXOUT_DIV 值,RATE 绑定到 000,D初始为 2 分频,后续通过DRP修改TXOUT_DIV

TX_CLK25_DIV = 5, 生成25MHz的分频系数,5: 100 MHz ≤ TXPLLREFCLK_DIV1 ≤ 125 MHz

TX_LANE_INVERT = 0, 0不反转, 端口TXPOLARITY用于反转输出数据的极性

TX_PI_BIASSET = 1, 配置 TX phase interpolator

TXPI CFG = 0x0054, 配置 TX phase interpolator,仅 UltraScale+ FPGAs

A_TXDIFFCTRL = 5’b10110, 0-31,配置A_TXDIFFCTRL

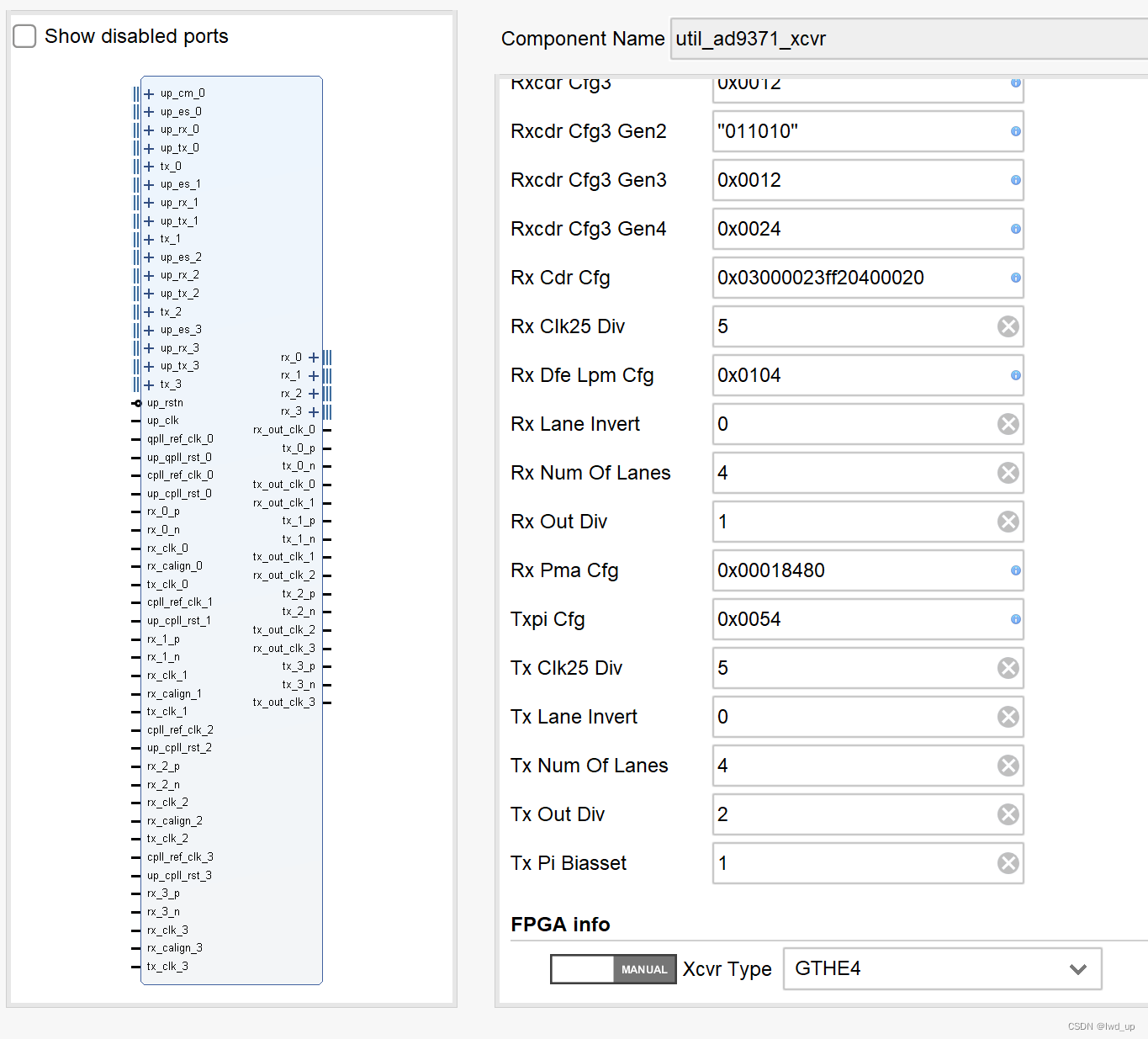

RX

RX_NUM_OF_LANES = 4, RX 和 RX_OS使用的 LANE 通道

RX_OUT_DIV = 1, 同TX

RX_CLK25_DIV = 5 , 同TX

RX_LANE_INVERT = 0, 同TX

RX_DFE_LPM_CFG = 16’h0104, 配置GTX 使用

RX_PMA_CFG = 0x00018480, 配置GTX 使用 配置 PMA_RSV

RX_CDR_CFG = 0x03000023ff20400020, 配置 GTX 使用

RXCDR_CFG0 = 0x0002, 配置 CDR ,使用向导软件 推荐值

RXCDR_CFG2_GEN2 = “1001100101”, 配置 CDR ,使用向导软件 推荐值

RXCDR_CFG2_GEN4 = 0x00B4, 配置 CDR ,使用向导软件 推荐值

RXCDR_CFG3 = 0x0012, 配置 CDR ,使用向导软件 推荐值

RXCDR_CFG3_GEN2 = “011010”, 配置 CDR ,使用向导软件 推荐值

RXCDR_CFG3_GEN3 = 0x0012, 配置 CDR ,使用向导软件 推荐值

RXCDR_CFG3_GEN4 = 0x0024, 配置 CDR ,使用向导软件 推荐值

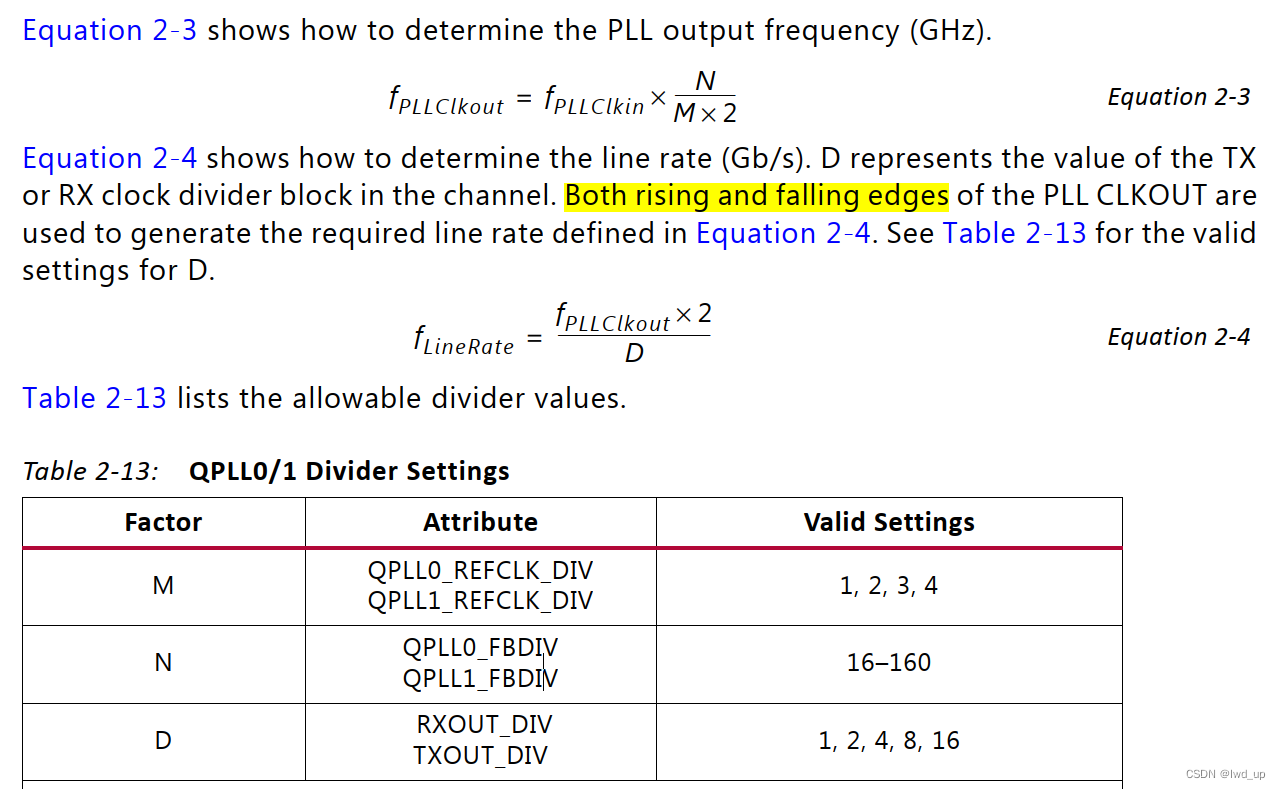

QPLL

QPLL_REFCLK_DIV = 1, M ,QPLL系数,后续DRP可修改,配置 QPLL0_REFCLK_DIV 和 QPLL1_REFCLK_DIV

QPLL_FBDIV = “0001010000”, N ,QPLL系数,后续DRP可修改,QPLL0_FBDIV 和QPLL1_FBDIV

QPLL_FBDIV_RATIO = 1, 配置 GTX

QPLL_CFG = “000011010000000000110000001”, GTX

POR_CFG = 0x0006, 保留 ,使用向导软件 推荐值

PPF0_CFG = 0x0600, 保留 ,使用向导软件 推荐值

QPLL_CFG0 = 0x331C, QPLL0 和 1, 保留 ,使用向导软件 推荐值

QPLL_CFG1 = 0xD038, QPLL0 和 1, 保留 ,使用向导软件 推荐值

QPLL_CFG1_G3 = 0xD038,QPLL0 和 1, 保留 ,使用向导软件 推荐值

QPLL_CFG2 = 0x0FC0,QPLL0 和 1, 保留 ,使用向导软件 推荐值

QPLL_CFG2_G3 = 0x0FC0,QPLL0 和 1, 保留 ,使用向导软件 推荐值

QPLL_CFG3 = 0x0120,QPLL0 和 1, 保留 ,使用向导软件 推荐值

QPLL_CFG4 = 0x0003,QPLL0 和 1, 保留 ,使用向导软件 推荐值

QPLL_CP = “0001111111”, QPLL0 , 保留 ,使用向导软件 推荐值

QPLL_CP_G3 = “0000011111”, QPLL0 , 保留 ,使用向导软件 推荐值

QPLL_LPF = “0100110111”, QPLL0 , 保留 ,使用向导软件 推荐值

GTY4_PPF0_CFG = 0x0800, GTY4

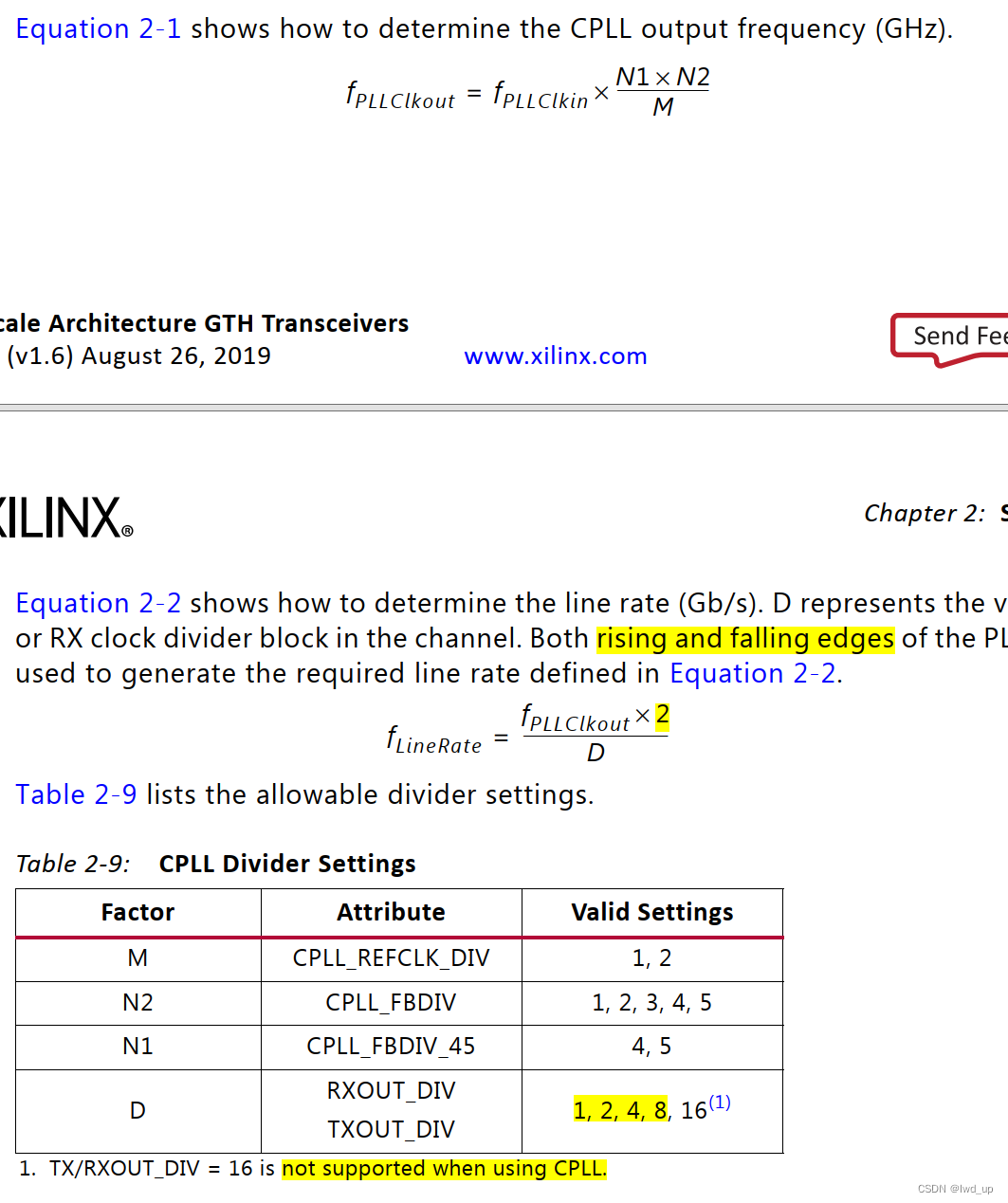

CPLL

CPLL_FBDIV = 2, CPLL 系数 N2 ,后续DRP可修改

CPLL_FBDIV_4_5 = 5, CPLL 系数 N1,后续DRP可修改

CPLL_CFG0 = 0x01FA,CPLL , 保留 ,使用向导软件 推荐值

CPLL_CFG1 = 0x0023, CPLL , 保留 ,使用向导软件 推荐值

CPLL_CFG2 = 0x0002, CPLL , 保留 ,使用向导软件 推荐值

CPLL_CFG3 = 0x0000, CPLL , 保留 ,使用向导软件 推荐值

GTH4_CH_HSPMUX = 0x2424, 配置 GTH

GTH4_PREIQ_FREQ_BST = 0, 配置 GTH

GTH4_RXPI_CFG0 = 0x0002, 配置 GTH , 保留 ,使用向导软件 推荐值, 仅 UltraScale FPGAs

GTH4_RXPI_CFG1 = 0x0015, 配置 GTH , 保留 ,使用向导软件 推荐值

GTY4_CH_HSPMUX = 0x2020, 配置 GTY

GTY4_PREIQ_FREQ_BST = 0, 配置 GTY

GTY4_RTX_BUF_CML_CTRL = 3’b011, 配置 GTY

GTY4_RXPI_CFG0 = 0x0100, 配置 GTY

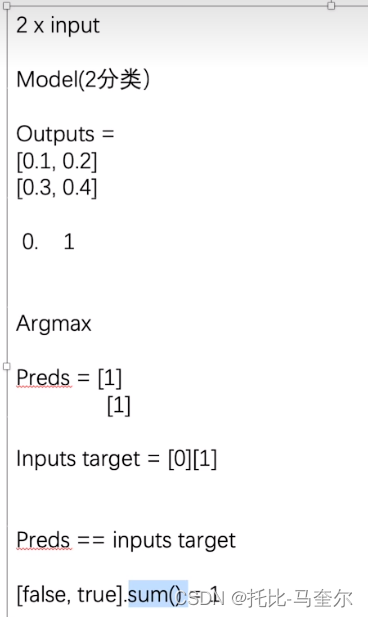

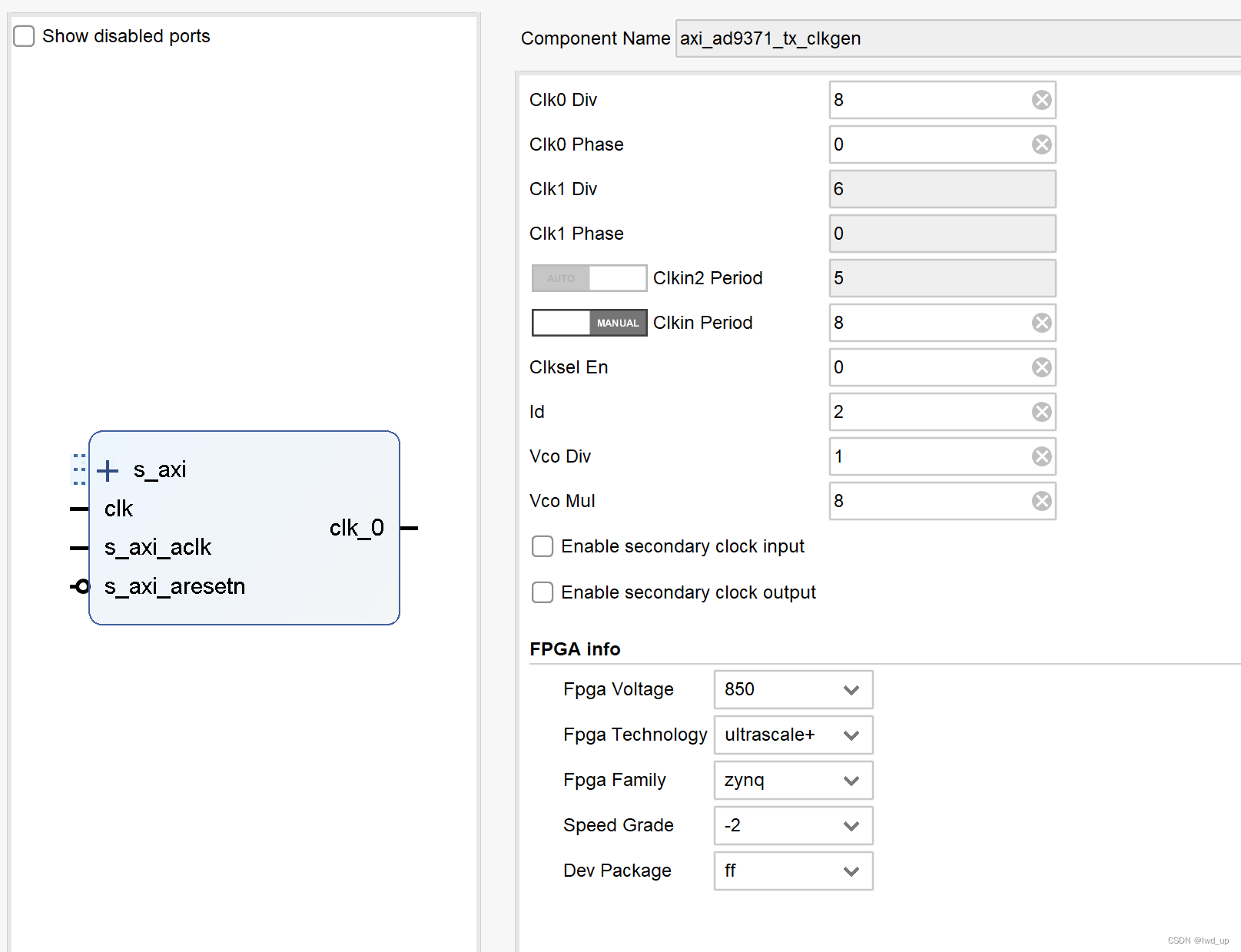

axi_ad9371_tx_clkgen

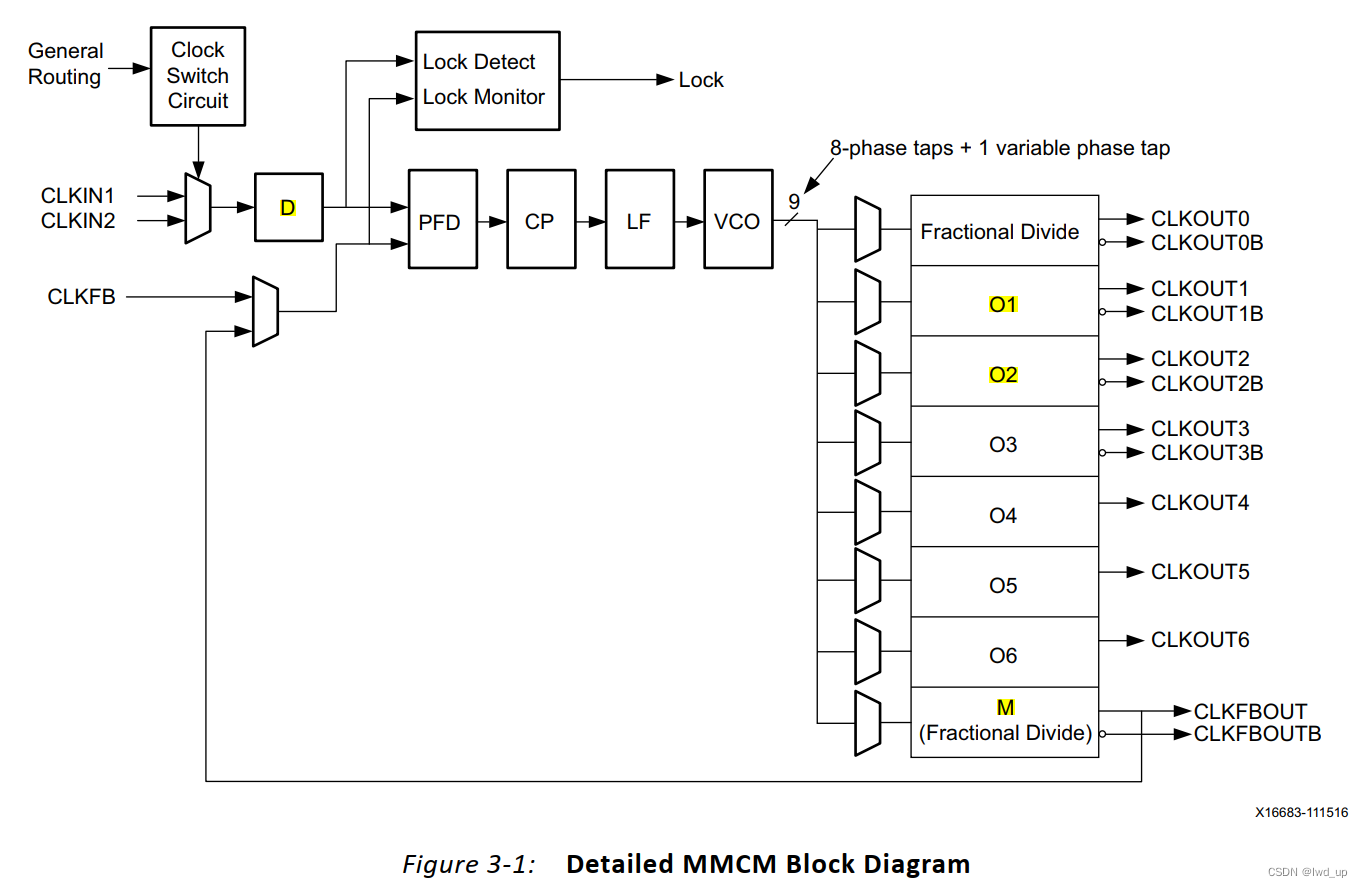

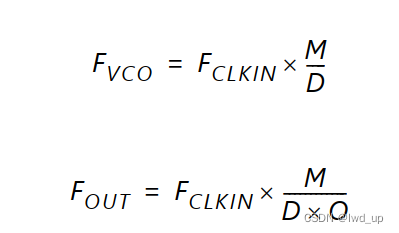

参考 UG572,MMCM框架如下,根据 DS925, Zynq UltraScale+ MPSoC 的MMCM VCO的工作频率为 800 M 到 1600MHz

Enable secondary clock input :勾上可以打开MMCM 的 Secondary clock,当 CLK SEL =1,选用 Primary clock ,当 CLK SEL =0,选用 Secondary clock

Enable secondary clock output:勾上可以打开MMCM 输出的第二个 clock,例程例化的 MMCM 输出了3个 OUT CLK,顶层引出了2个,CLK_0 和 CLK_1

CLK OUT 0 和 1的控制参数,后续通过DRP 可以对MMCM 中的这几个参数 重配置

Clk0 Div :公式中的O0,CLKOUT0_DIVIDE_F,1-128,或者 2.000 到 128.000 增量 0.125

Clk0 Phase : CLKOUT0_PHASE,–360.000 to 360.000

Clk1 Div :公式中的O1, CLKOUT1_DIVIDE,1-128

Clk1 Phase : CLKOUT1_PHASE,–360.000 to 360.000

VCO 配置参数,也可以通过DRP修改

Vco Div : 公式中的D, DIVCLK_DIVIDE,1-106

Vco Mul :公式中的 M,CLKFBOUT_MULT_F,2 到128 或 2.000 到 128.000 增量 0.125

CLK_IN 周期 ,也可以通过DRP修改

Clkin Period : CLKIN1, Primary clock 周期 ,0.968 to 100.000,ns

Clkin2 Period : CLKIN2,Secondary clock 周期,0.968 to 100.000,ns

.DIVCLK_DIVIDE (MMCM_VCO_DIV),.CLKFBOUT_MULT_F (MMCM_VCO_MUL),.CLKOUT0_DIVIDE_F (MMCM_CLK0_DIV),.CLKOUT0_PHASE (MMCM_CLK0_PHASE),.CLKOUT1_DIVIDE (MMCM_CLK1_DIV),.CLKOUT1_PHASE (MMCM_CLK1_PHASE),.CLKIN1_PERIOD (MMCM_CLKIN_PERIOD),.CLKIN2_PERIOD (MMCM_CLKIN2_PERIOD),