SDRAM与DDR的简单概念介绍

SDRAM

定义:

同步动态随机存取内存(Synchronous Dynamic Random-Access Memory,简称SDRAM)是有一个同步接口的动态随机存取内存DRAM(可以参考前文)。可以理解为是一种利用同步计时器对存储器的输入输出信号加以控制的DRAM。

- 同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准

- 动态是存储阵列需要不断的刷新来保证数据不丢失(DRAM所带有的属性)

- 随机是指数据不是线性依次存储,而是自由指定地址进行数据读写(DRAM所带有的属性)

同步与异步:

- 通常DRAM是有一个异步接口的,这样它可以随时响应微处理器传递而来的控制输入的变化。

- SDRAM在DRAM的架构基础上增加同步功能(通过增加同步接口实现)和双区域功能(Dual Bank),使得微处理器能与SDRAM的时钟同步。

- 具体操作为:在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机(同步计时器),对进入的指令进行流水(Pipeline)操作。这使得SDRAM与没有同步接口的异步DRAM(Asynchronous DRAM)相比,可以有一个更复杂的操作模式。所以SDRAM执行命令和传输资料时相较于DRAM可以节省更多时间。

读写操作流水:

该流水操作意味着芯片可以在完整处理完之前的指令前,接受一个新的指令,用以作为流水线以更高的吞吐量完成任务。

- 写Pipline:写入命令在另一个指令执行完之后可以立刻执行,而不需要等待数据写入存储队列的时间。

- 读Pipline:需要的数据在读取指令发出之后固定数量的时钟后到达,而这个等待的过程可以发出其它附加指令。这种延迟被称为等待时间(Latency),在为计算机购买内存时是一个很重要的参数。

SDRAM在计算机中被广泛使用,从起初的SDRAM到之后一代的DDR(或称DDR1),然后是DDR2和DDR3进入大众市场,2015年开始DDR4进入消费市场。

多Bank:

SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM模组中(Dual Bank),其中一个Bank在进行预充电期间,另一个Bank却是可以随时被读取的,这样当进行一次读取后,又马上读取已经预充电Bank的数据时,就无需等待而是可以直接读取了,这也就大大提高了存储器的访问速度。

DDR

定义:

全称为(Double Data Rate Synchronous Dynamic Random Access Memory,Double Data Rate SDRAM,),中文名为“双数据率同步动态随机存储器”或者“双数据率SDRAM”。DDR是在原有的SDRAM的基础上改进而来。此时为了明确定义,SDRAM可以被区别定义为(Single Data Rate SDRAM,SDR SDRAM)。DDR定义中的名词含义如下:

- 同步:是指内存工作需要同步时钟,内部命令的发送与数据传输都以它为基准(SDRAM带来的属性)

- 动态:是指DDR是一种掉电就丢失数据的存储器件,并且需要定时的刷新来保持数据的完整性(DRAM带来的属性)

- 双数据率是指:SDRAM在一个

CLK周期传输一次数据,而DDR在一个CLK周期传输两次数据,在差分时钟CLK与CLK#的交叉点都有数据传输因此称之为Double Data Rate(具体可以参考后文)

双倍数据率:

别于SDR SDRAM单一周期内只能读写1次,DDR的双倍数据传输率指的就是单一周期内可读取或写入2次,本文基本都特指DDR1。在核心频率不变的情况下,DDR传输效率为SDR SDRAM的2倍。

该概念称为预取Prefetch,就有了prefetch技术,DDR1是两位预取(2-bit Prefetch,个人理解为请求为1bit的情况下,会预先一次取出2bit,为之后的IO数据传输做准备),有的公司则贴切的称之为2-n Prefetch(n代表芯片位宽)。

在描述DDR速度的时候一般使用MT/S单位,每秒多少兆次数据传输。举例而言,当核心频率为133~200 MHz的时候,此时DDR内存的传输速率约为266~400 MT/s不等,像是DDR 266、DDR 400都是这个时期的产品。

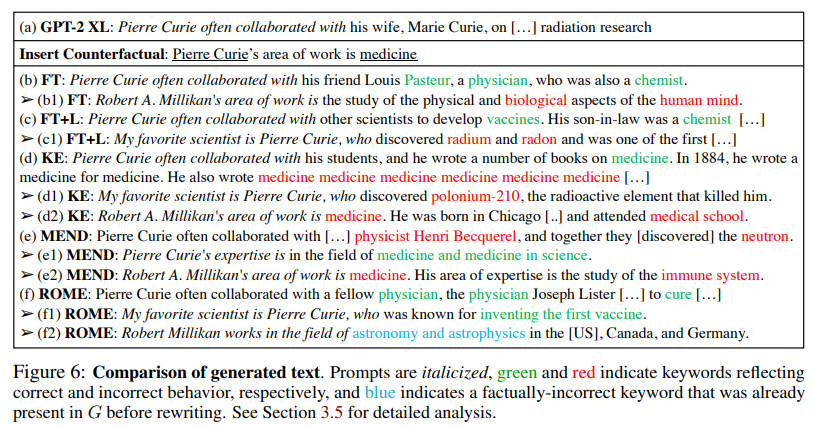

首先可以看一张DDR的时序图

从图中发现它多了两个信号: CLK#与DQS,CLK#与正常CLK时钟相位相反,形成差分时钟信号。而数据的传输在CLK与CLK#的交叉点进行,可见在CLK上升(CLK#下降沿)与CLK下降沿(CLK#上升沿)都有数据被触发,从而实现DDR。

在此,可以说通过差分信号( CLK和CLK#)达到了DDR的目的,CLK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说。之所以能实现双倍的速率,还要从其内部的改进说起。也就是后文所描述的L-Bank结构。

Bank:

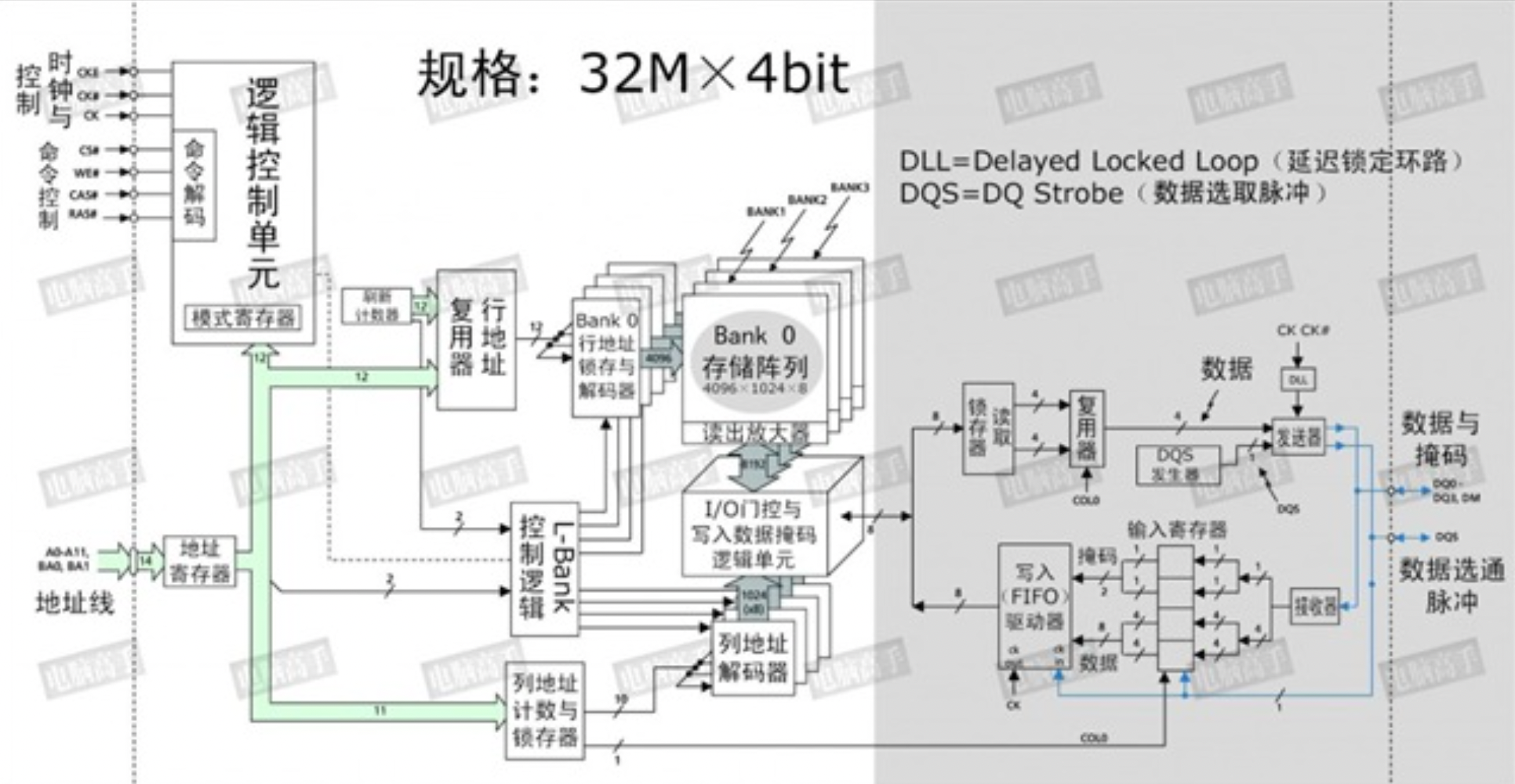

从图中可以看出来,白色区域内与SDRAM的结构基本相同,但请注意灰色区域,这是与SDRAM的不同之处。在于对不同内部Load Bank (L-Bank)规格的使用。其具体操作流程可以通过如下的内部结构进行说明:

SDRAM中L-Bank存储单元的容量(也可以称为芯片内部总线位宽,个人认为理解为Bank的数量也可以)与芯片位宽(也可称为芯片I/O总线位宽)相同(在之后的博客中会讲解SDRAM的内部结构,以及为什么会有这一特性)。但在DDR SDRAM中并不是这样,存储单元的容量是芯片位宽的多倍,在此为了方便理解,先设置为2倍,也就是最初的DDR1。所以在此需要说明在DDR中不能再套用讲解SDRAM时 “芯片位宽=存储单元容量” 的情况。也因此,真正的行、列地址数量也与同规格SDRAM不一样了。

以上图为例,在读取时,L-Bank在内部时钟信号的触发一次数据传输事务,其中希望若干个8bit数据,个人理解为Bank数量为16,在内部颗粒读取到的数据量为16bit,传输到读取锁存器,分成两个8bit数据传给复用器,合并为一个8bit的数据流(包含两个8bit,之后按序输出),然后由发送器在DQS的控制下在外部差分时钟的时钟交叉点分两次传输8bit的数据。这样,如果时钟频率为100MHz,那么在I/O端口处,由于是上下沿触发,那么就是传输频率就是200MHz。

一些写博客过程中的思考

问题1:为什么不对SDR SDRAM进行提速,实现更高的内部时钟,来完成更高效的信息读取?

如果使用更加高频的信号,这里的“高频”是相对于给定技术时代或应用场景的限制来理解的,这些信号可能会带来:

- 有限的信道带宽导致更多的离散

- 高频信号需要更多的功耗

- 更容易受到电容耦合和反射的影响

- 让PCB 上存在的各种无意天线的辐射

高频信号也更难使用测试设备进行表征和故障排除。例如,示波器的模拟和数字带宽有限,随着频率的增加,它会在波形中引入更多失真。

因此,在尝试实现更高的时钟速率之前,从现有时钟速率中提取尽可能多的吞吐量是有意义的。通过从单一数据速率接口转向 DDR 接口,设计人员可以在不改变系统最大信号频率的情况下显着提高数据传输速率。即使数据信号的最大频率增加了两倍,所有这一切都可以实现,这个新的数据频率不高于先前的时钟频率。

问题2:为什么SDR SDRAM需要通过差分时钟进行,data传输事务的出发,而不是通过单个时钟的上升沿和下降沿?

查阅了很多资料,发现对CLK#的作用认识很少,很多人理解为第二个触发时钟,实现第二个数据的泵出,其实它的真实作用是起到触发时钟校准的作用。

对此需要说明,差分时钟线的具体使用如下:

- 控制信号和地址信号都会在

CLK的上升沿和CLK#的下降沿交叉处采集 - 数据传输在一个周期的上升沿和下降沿(一个时钟周期的同相反相交叉处有两个)都会进行

从这里可以发现,数据的预取是通过CLK实现的,数据的第二次泵出也不仅仅是通过CLK#的时钟沿实现的。

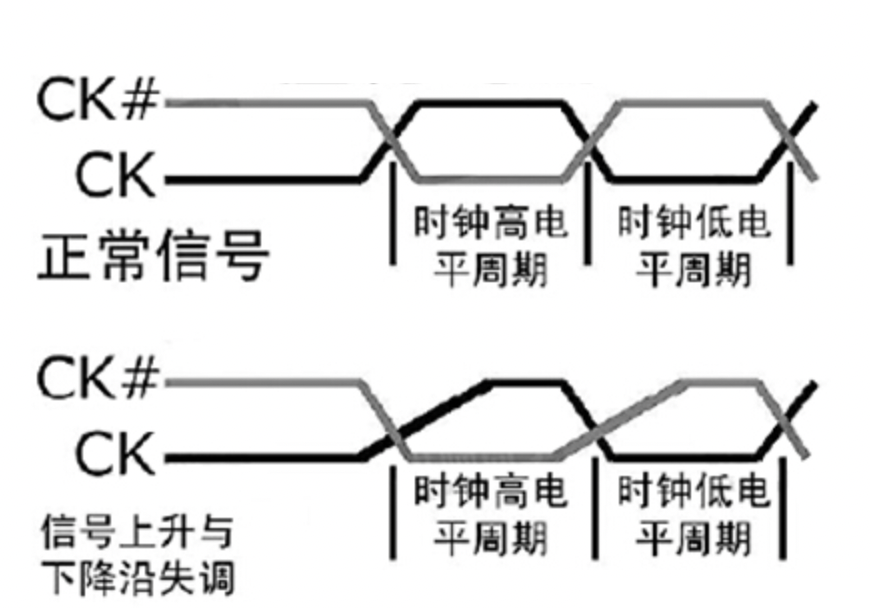

由于数据是在CLK的上升沿和下降沿分别两次触发,实现DDR传输周期缩短一半的目标,在此过程中必须要保证传输周期的稳定以确保数据的正确传输,这就要求CLK的上升沿和下降沿间距要有精确的控制。

但因为温度、电阻性能的改变等原因,同时CLK上升沿快下降沿慢,单独使用的时候CLK上下沿间距可能发生变化,很难实现上面所需要达到的精确控制。

添加反向时钟CLK#(上升慢下降快)形成差分时钟,就能起到纠正的作用。也使差分时钟的跳变点频率 CL成为1.5倍 和 2.5倍CLK 成为可能,并容易实现。这种触发方式可以提高数据传输的可靠性和稳定性。

参考文献

至简设计系列-SDRAM读写控制器 - 知乎

差分时钟作用_差分时钟的作用_tanfuz的博客-CSDN博客

DDR基础原理介绍:差分时钟,同相,反相,两者差分交叉处也即差分值为0时读写信号,一个时钟周期可以上升沿下降沿都传输数据。相当两个时钟了。所以spi简单一个时钟信号不可能一个周期内同时锁定上升沿下降沿_什么是差分时钟-CSDN博客

DDR SDRAM简介_与SDRAM的区别_时序介绍-维库电子通

差分时钟、DQS与DQM - DDRx的关键技术介绍(上) - edadoc - 博客园

DDR扫盲—-关于Prefetch(预取)与Burst(突发)的深入讨论_ddr 预取-CSDN博客

DDR扫盲——关于Prefetch与Burst的深入讨论-CSDN博客

DDR基本原理-CSDN博客

【精选】(一)DDR 基础介绍——(演进、构成、存储原理)_SD.ZHAI的博客-CSDN博客

关于DDR的prefetch_ddr prefetch-CSDN博客

双倍数据速率 - 维基百科,自由的百科全书

DDR内存技术原理分析讲解 - 知乎

DDR技术简介 - 知乎

DDR Memory工作原理 - 知乎

ddr(双倍数据速率) - 知乎

科普:DDR为什么使用双倍数据速率 - 知乎

DDR基础原理介绍 - 知乎

深入内存/主存:解剖DRAM存储器 - 知乎

深入浅出DDR系列(一)–DDR原理篇_ddr interleave-CSDN博客

【精选】一步一步带你理解DDR基本原理_ddr内存控制器的工作原理_百里杨的博客-CSDN博客

一文搞懂DDR SDRAM工作原理 - 知乎

【紫光同创国产FPGA教程】【第十章】DDR3读写测试实验 - ALINX官方博客 - 博客园

DQS(Bidirectional data strobe,双向数据滤波【转】-CSDN博客

DDR memory工作原理 - 君の内存

【精选】FPGA SDRAM和DDR的学习(DDR部分)_fpga ddr_George_ray的博客-CSDN博客

DDR4, DDR3, DDR2, DDR1 及SDRAM各有何不同? - 創見資訊

![[原创]Cadence17.4,win64系统,构建CIS库](https://img-blog.csdnimg.cn/3800958cf6174a19bdec33d4576ba5ae.png)

![[LeetCode] 2.两数相加](https://img-blog.csdnimg.cn/0b28e0acd1a74e1ca7a12d90a79a70bd.jpeg#pic_center)