专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

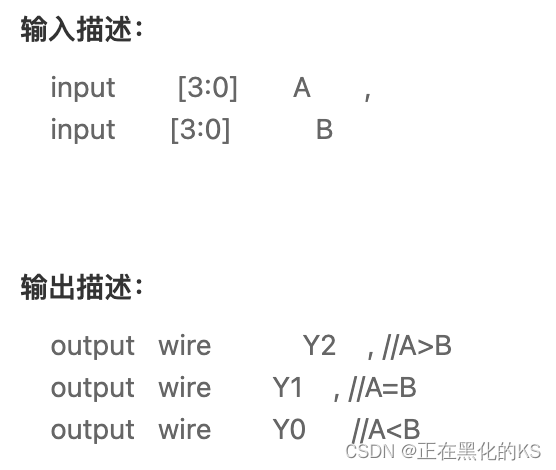

分析

这里要注意题目的“门级描述方式”,所以我们只能使用基本门电路:&,|,!,^,^~。

具体实现思路:通过真值表得出Y0 Y1 Y2的逻辑表达式 根据逻辑表达式 画出门电路图

用Verilog的原语描述门电路

根据题目所给比较器真值表,求出Y2 Y1 Y0的逻辑表达式如下:

Y2=A[3]·~B[3]+(A[3]⊙B[3]) ·A[2] ·~B[2]+ (A[3]⊙B[3]) ·(A[2]⊙B[2]) ·A[1] ·~B[1]+ (A[3]⊙B[3]) · (A[2]⊙B[2]) · (A[1]⊙B[1]) · A[0] ·~B[0];

Y0=~A[3] ·B[3]+(A[3]⊙B[3]) ·~A[2] ·B[2]+ (A[3]⊙B[3]) ·(A[2]⊙B[2]) ·~A[1] ·B[1]+ (A[3]⊙B[3]) · (A[2]⊙B[2]) · (A[1]⊙B[1]) ·~A[0] ·B[0];

Y1=(A[3]⊙B[3]) ·(A[2]⊙B[2]) · (A[1]⊙B[1]) · (A[0]⊙B[0])

求解逻辑表达式的方法:怎样通过真值表得到逻辑表达式-CSDN博客

not iv0(iv0_o, B[0]),iv1(iv1_o, B[1]),iv2(iv2_o, B[2]),iv3(iv3_o, B[3]),iv4(iv4_o, A[0]),iv5(iv5_o, A[1]),iv6(iv6_o, A[2]),iv7(iv7_o, A[3]);and ad0(ad0_o, iv0_o, A[0]),ad1(ad1_o, iv1_o, A[1]),ad2(ad2_o, iv2_o, A[2]),ad3(ad3_o, iv3_o, A[3]),ad4(ad4_o, ad0_o, xnr0_o, xnr1_o, xnr2_o),ad5(ad5_o, ad1_o, xnr1_o, xnr2_o),ad6(ad6_o, ad2_o, xnr2_o),ad7(ad7_o, iv4_o, B[0]),ad8(ad8_o, iv5_o, B[1]),ad9(ad9_o, iv6_o, B[2]),ad10(ad10_o, iv7_o, B[3]),ad11(ad11_o, ad7_o, xnr0_o, xnr1_o, xnr2_o),ad12(ad12_o, ad8_o, xnr1_o, xnr2_o),ad13(ad13_o, ad9_o, xnr2_o),ad14(Y1, xnr2_o, xnr1_o, xnr0_o, xnr3_o);xnor xnr0(xnr0_o, A[1], B[1]), xnr1(xnr1_o, A[2], B[2]), xnr2(xnr2_o, A[3], B[3]), xnr3(xnr3_o, A[0], B[0]); or or0(Y2, ad3_o, ad6_o, ad5_o, ad4_o),or1(Y0, ad10_o, ad13_o, ad12_o, ad11_o) ;