FPGA小项目:基于Arnold与Logistic的图像加解密实现

- 目录

- 概述

- 原理

- 设计方案

- FPGA实现

- 实验与测试

目录

概述

该文章来源于之前做过的一个小项目,属于FPGA图像处理领域,具体而言,是基于FPGA实现arnold和logistic加密解密算法。

原理

arnold置乱参考:

图像加密——matlab实现Arnold置乱算法及矩阵幂的求解,https://blog.csdn.net/H19981118/article/details/123577591?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522168068215616782427430956%2522%252C%2522scm%2522%253A%252220140713.130102334…%2522%257D&request_id=168068215616782427430956&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2alltop_positive~default-1-123577591-null-null.142v81wechat,201v4add_ask,239v2insert_chatgpt&utm_term=arnold%E7%BD%AE%E4%B9%B1&spm=1018.2226.3001.4187

logistic置乱参考:

【图像加密】图像处理之Logistic混沌置乱加密,https://blog.csdn.net/hujingshuang/article/details/45718069?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522168068224116800180683823%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=168068224116800180683823&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2allfirst_rank_ecpm_v1~rank_v31_ecpm-11-45718069-null-null.142v81wechat,201v4add_ask,239v2insert_chatgpt&utm_term=logistic%E5%8A%A0%E5%AF%86&spm=1018.2226.3001.4187

设计方案

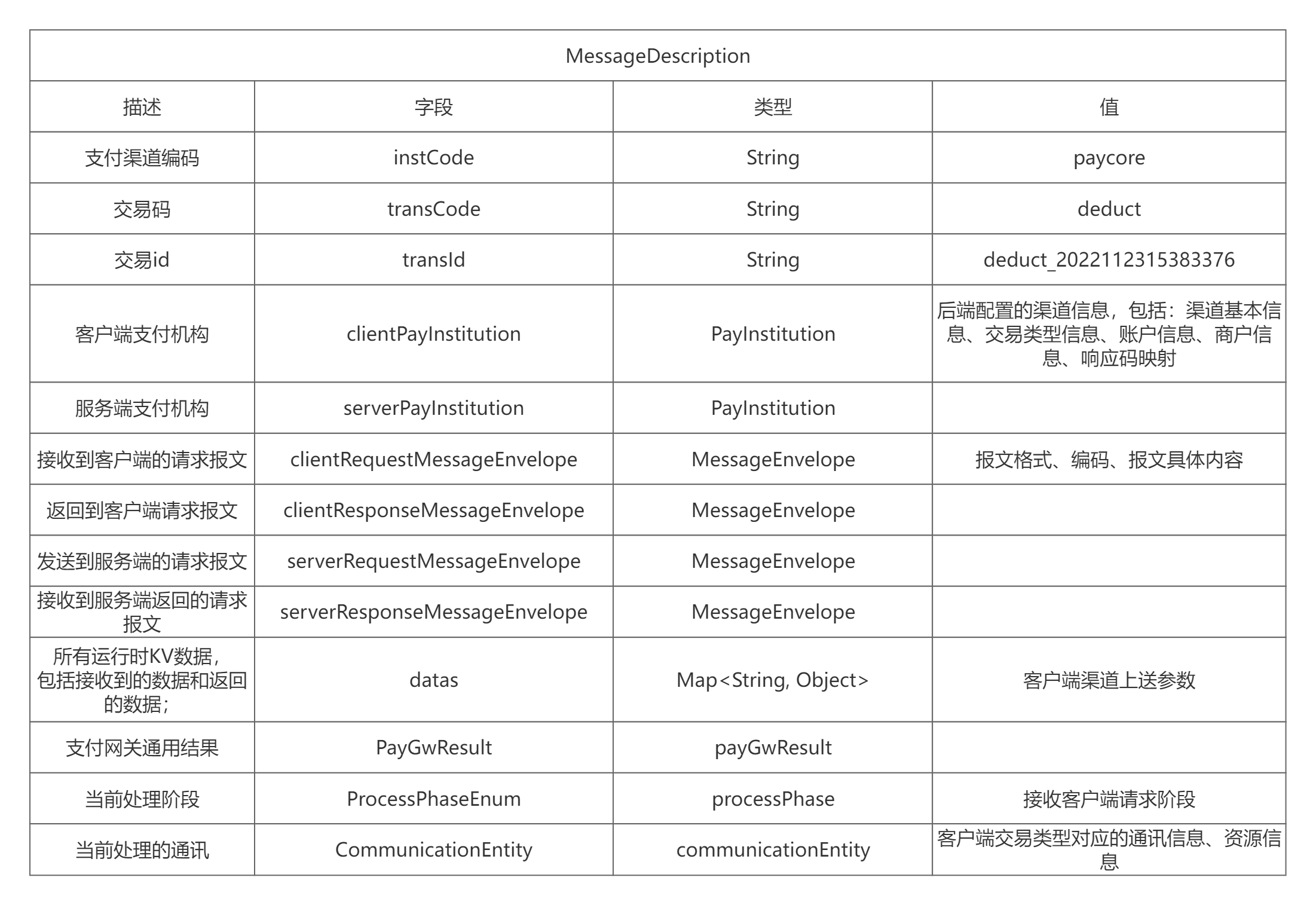

该项目整体流程如下:首先将一张图片提前存入FPGA的ROM中,将ROM中的图像数据读出,分解为RGB三个通道。其中,R通道和G通道使用,B通道使用。最终整合三个通道,合并为RGB图像,并在HDMI端进行显示。同时,将加密后的图像进行相应算法的逆解密过程,并同样将解密图像输出至HDMI端进行显示。

具体而言,首先从硬件选型的方面来看,A7系列的板卡完全能够满足资源要求,但本次项目所需要的RAM数量较多,结合实际情况最终选用XC7A35TFGG484-2板卡作为本次实验的FPGA板卡。

其次从输出设备来看,选用HDMI作为本次实验的输出设备,这是由于HDMI是非常高速且性能表现良好的图像接口,同时板卡中也带有HDMI接口。

最后是方案设计:将图片通过工具转换为COE文件,加载进ROM的IP核中,将图像从ROM中读出,分通道进行加密,加密图像存入RAM中,等待同步信号,将加密图像合并输出并进行显示,而后将加密后的图像存入RAM中,读出进行解密,解密后的图像存入RAM中,等待同步信号出现释放图像,合并图像并进行HDMI输出显示,最开始在显示端,想用VIO控制加密和解密图像显示,但是觉得很麻烦,还需要人工操作,最终通过计数的方法,在计满一定帧数后切换至另一图像,实现加密图像和解密图像的交替显示。

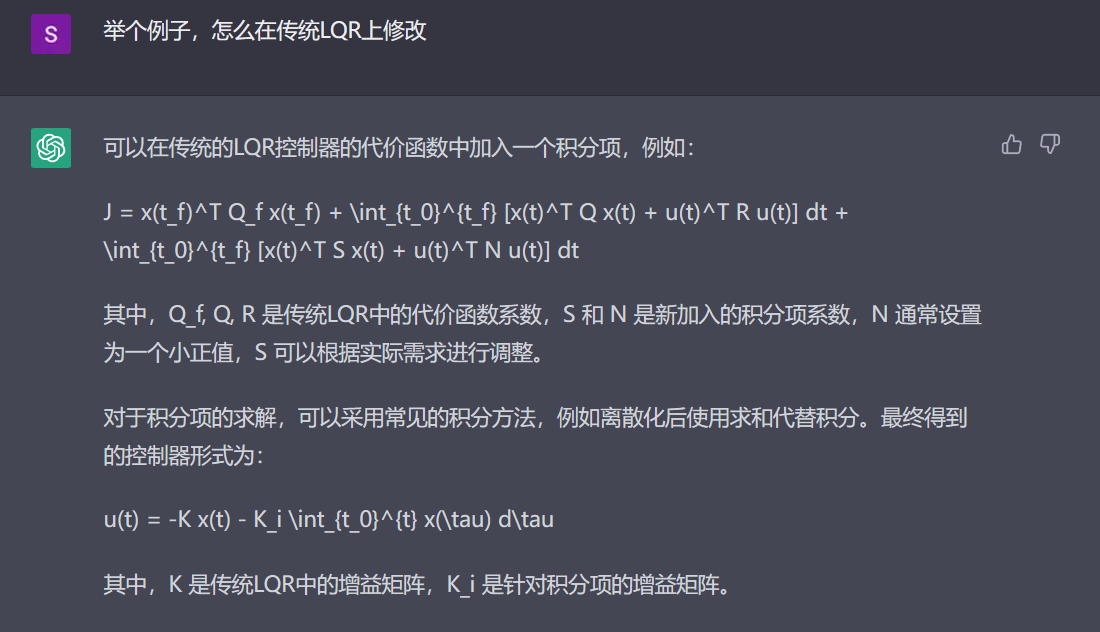

FPGA实现

最终整体RTL图如图所示:

图1-1RTL图

图1-1RTL图

代码如图 所示:

图1-2 代码图

实验与测试

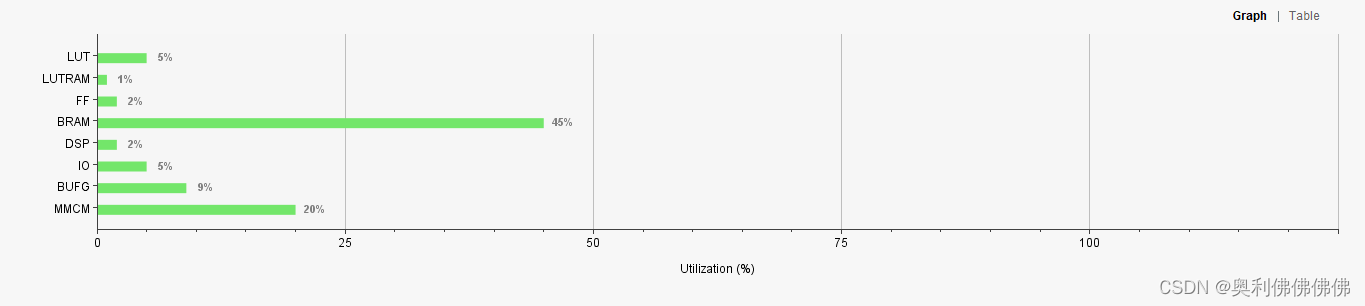

资源占用率如图所示:

图2-1资源占用率

板卡验证结果:

图2-2 解密图显示

图2-2 解密图显示

图2-3 加密图像显示

图2-3 加密图像显示

图2-2为加密图显示于hdmi显示器,图2-3为加密后图像显示于HDMI端。从图2-2和2-3可以看出,该工程能够有效、快速地将图像加密,置乱轮数由自己决定,同时可以通过解密算法将加密图像进行还原,由于本文rom资源有限,因此分辨率较低,后续也可以通过串口、sd卡等方式输入高分辨率的图像。

总结:整体而言,该设计还有许多优化之处,比如资源的优化,大可不必使用如此多的RAM资源,但是为了便于调试本次项目中还是用了许多RAM。但从结果来说,实现了项目要求,正确的加密并解密了图像,同时产生极低的时间开销,这也归功于FPGA并行处理优势和流水线操作。