1. AXI/AHB/APB差异

AMBA (Advanced Microcontroller Bus Architecture) 高级处理器总线架构

AHB (Advanced High-performance Bus) 高级高性能总线

ASB (Advanced System Bus) 高级系统总线

APB (Advanced Peripheral Bus) 高级外围总线

AXI (Advanced eXtensible Interface) 高级可拓展接口

AHB协议需要一次突发传输的所有地址,地址与数据锁定对应关系,后一次突发传输必须在前次传输完成才能进行。

AXI只需要一次突发的首地址,可以连续发送多个突发传输首地址而无需等待前次突发传输完成,并且多个数据可以交错传递,此特征大大提高了总线的利用率。

AHB总线与AXI总线均适用于高性能、高带宽的SoC系统,但AXI具有更好的灵活性,而且能够读写通道并行发送,互不影响;更重要的是,AXI总线支持乱序传输,能够有效地利用总线的带宽,平衡内部系统。因此SoC系统中,均以AXI总线为主总线,通过桥连接AHB总线与APB总线,这样能够增加SoC系统的灵活性,更加合理地把不同特征IP分配到总线上。

2. AXI

2.1 AXI响应类型

AXI有如下几种响应类型:OKAY(正常访问成功)/EXOKAY(独占访问成功)/SLVERR(从设备错误)/DECERR(译码错误)。

对于一次写交易,不是每拍数据传输完毕都有一个响应,而是对整个 burst 只有一个响应。一次读交易中,从设备可以对一个 burst 中不同的数据拍返回不同的响应。例如,在一个 16 拍的 burst 中,从设备可能会对其中的 15 个数据拍返回 OKAY 响应,而对其中的一个数据拍返回 SLVERR 响应。

OKAY响应:

一次正常访问的成功

一次独占访问的失败

对不支持独占访问的设备进行了独占访问操作

EXOKAY响应:表示一次独占访问的成功。

SLVERR响应:表示一次不成功的交易。从设备出错的情况有:

1、FIFO/buffer 上溢出和下溢出

2、不支持的数据拍大小

3、对只读的地址执行写操作

4、从设备访问超时

5、试图访问没有可用寄存器的地址

6、试图访问不使能或断电的设备

DECERR:

当互联设备不能成功对一个从设备访问解码时,它可以将访问转向一个默认的从设备,并且默认设备返回DECERR响应。一种实现的选择是使默认的从设备也记录下解码错误的细节,以确定错误是如何发生的。用这种方法,默认的从设备可以很显著的简化调试过程。

2.2 AXI突发类型

AXI 协议定义了三种突发类型,分别为固定长度突发、增量突发、回环突发。

固定长度突发:在一个固定长度突发中,每个传输的地址都保持相同。这种突发类型用于重复访问相同位置,比如装载和清空一个外设 FIFO。

增量突发:在一个增量突发中,每个传输的地址都是在前一个传输地址的基础上递增的。增量值取决于传输大小。

回环突发:回环突发类似于增量突发,突发中每个传输的地址按增量递增的。但是在回环突发中,当达到较大的地址边界时,地址会卷回到较小的地址。回环边界是突发中每个传输的大小乘以突发中总共传输的次数。

回环突发需要遵循两个限制:

· 起始地址必须对齐到传输大小

· 突发长度必须是 2、 4、 8 或 16

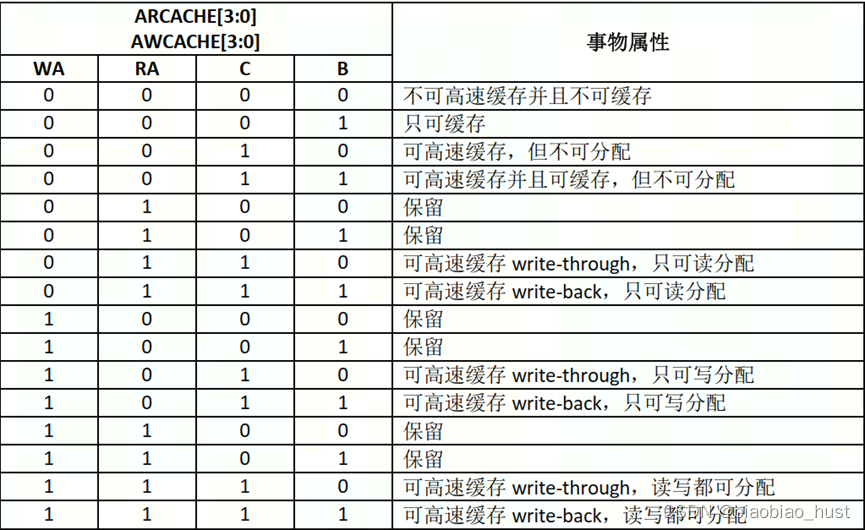

2.3 AXI CACHE支持

通过使用缓存信号AXCACHE来支持系统级缓存和其他性能增强组件。这些信号提供有关如何处理事务的附加信息。

arm对cacheable和bufferable的解释是:

Bufferable: Write to memory can be carried out by a write buffer while the processor continues on to next instruction execution.

Cacheable: Data obtained from memory read can be copied to a memory cache so that next time it is accessed the value can be obtained from the cache to speed up program execution.

个人理解:对于bufferable的地址,写指令可以不用马上执行到memory中,可以先写入write buffer,然后处理器继续执行。对于cachable的地址,写指令可以只写到cache中,然后处理器继续执行。

write-through:写入cache时,对memory的内容一起写。

write-back:写入cache时,不改变memory内容,只把对应的dirty bit置高。当cache中内容被替换并且内容对应的dirty bit为高时,写入memory。

对于表中的Device, 个人理解是指的是这部分地址实际上是外设中寄存器和内存的映射,不是真正的内存,对于外设,prefetch之类的优化方式往往不能用。因此arm特别涉及了device non-bufferable 和device bufferable进行处理。

Allocate:指的是当cache miss发生的时候,先从memory中把数据提取到cache中,然后当作cache hit处理。

non-allocate:指的是cache miss发生时,只对memory进行读写。non-allocate实际上是对处理器进行的建议,并不是强制的要求。也就是说,出于提高性能考虑,一部分地址当发生miss的时候,不需要写入cache,建议直接对地址进行读写。

AxCACHE[0] (Bufferable):

表示该传输事务在传输至目的地的途中,可以被interconnect或者任意的AXI组件缓存,延迟若干个周期。一般应用于写传输事务。本来在写传输事务中需要写入至主存储(main memory)的数据,可以先缓存于cache中,等待被替换时再真正写入主存储。写事务原先的目的地是主存储,比如外部DDR,理论上应该由DDR控制器在“真的”写入数据到DDR后,向CPU发出写回复信号,表示写传输事务完成。但是现在数据写入cache后,即向CPU发出了写回复信号结束了本次写回复。

AxCACHE[1] (Modifiable):

表示传输过程中,该写传输事务的传输特性可以改变。

- 1、单个传输事务可以被分解为多个传输事务

- 2、同理,多个传输事务也可被聚合为一个(上节描述的现象)

- 3、读传输事务中,可以预取相邻地址上的读数据,要求目的地址返回比主机需求更多的数据

- 4、写传输事务中,可以访问比需求地址跨度更大的区域,其中使用WSTRB信号防止更新不相关的数据

上述几种情况中, AxADDR、AxSIZE、AxLE、AxBURS、AxID、AxQOS等几项信号可以发生改变(Modify)。

AxCACHE[3:2] (cache-allocate):

用于表示本次传输事务所访问地址中的数据是否可能在缓存中。

AxCACHE[2](Allocate):当前地址的数据可能因为前期的访问,已经分派空间并缓存于 cache中;

AxCACHE[3](other allocate):当前地址的数据可缓存于 cache 中,是因为其他主机事务而分派空间缓存,或者是本机其他类型的事务而缓存。(对于读事务来说,就是先前的写事务,反之亦然)

为2'b00时,表示该传输事务无需至cache中查找,必须直接从主存储中读取或者写入主存储。不为2'b00时,先前的读写事务可能已经将该地址缓存与cache中,所以该传输事务必须首先在cache中查找,缺失的情况下再访问主存储。

AWCACHE[2]信号置高表示本主机先前的写事务可能已经将该位置上的数据缓冲于 cache,首先在cache中查找对应表项。当AWCACHE[2]信号置低,但AWCACHE[3]置高时,该位置上的数据可能因为其他主机的操作、或者本机的读事务缓存于cache中,同样需要首先查找cache。对于读事务来说,字段的含义与写事务对应。

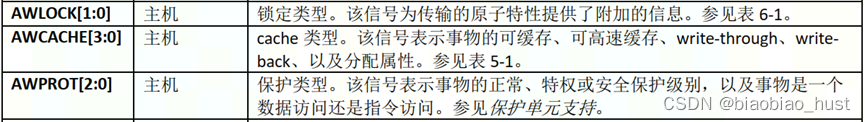

2.4 AXI保护支持

为了支持复杂的系统设计,系统中的互联和其它设备都通常有必要提供保护来防止非法事务。AWPROT或ARPROT信号提供三个级别的访问保护。

AXPROT[0] :0表示正常访问,1表示特权访问,特权处理模式通常在系统内具有更高级别的访问权限;

AXPROT[1] :0表示安全访问,1表示非安全访问

AXPROT[2] :0表示数据访问,1表示指令访问

2.5 AXI原子访问

为了使原子访问的开发更简单,使用 AXLOCK[1:0]信号提供独占访问和锁定访问。

独占访问

独占访问使得信号量类型操作(semaphore type operations)的开发不需要总线在操作期间保持对某一特定主机的锁定。独占访问既不会影响关键总线访问延迟,也不会影响最大可达到的带宽。

一个独占访问的基本过程如下:

- 主机执行一个某地址位置的独占读;

- 一段时间之后,主机通过执行一个到相同地址位置的独占写,来结束独占;

- 主机独占写访问的结果表示为:

· 在读和写访问之间,如果没有其它主机对该位置进行写,则独占访问成功;

· 在读和写访问之间,如果任何主机对该位置进行了写,则独占访问失败。在这种情况下地址位置不会被更新。

独占访问对硬件的监视,必须只能监视每个事物 ID 的一个地址。因此,如果一个主机没有完成独占操作的写操作部分,则接下来的一个独占写会改变正在监视的地址。

在独占读之后一段时间,主机尝试执行一个到相同位置的独占写操作。如果从独占读之后,地址位置没有改变,则独占写操作成功。从机返回EXOKAY响应,独占写操作更新memory的位置的内容。

如果从独占读之后地址位置发生了改变,则独占写操作失败,从机返回OKAY响应代替EXOKAY响应。独占写操作不会更新memory位置的内容。

一个主机可能没有完成独占访问的写操作部分。如果发生这种情况,则从机继续监视独占的地址,直到另一个独占读操作开始一个新的独占访问。

一个支持独占访问的从机必须具有监控电路。对于这种从机,推荐其具有一个监控单元,用来监控可访问该从机的每个可独占访问的主机ID。一个单端口从机可以具有一个从机外部的标准独占访问监控器,但是多端口的从机可能要求内部监控器。

独占访问监控器记录任何独占读操作的地址和ARID值。之后监控器一直监控该位置,直到一个该位置的写操作发生,或者直到相同ARID值的另一个独占读操作将监控器复位到一个不同的地址。当一个具有给定AWID值的独占写操作发生,则监控器会检查该地址是否正在被独占地监控。如果是,则意味着在独占写操作之前,该位置没有发生过写操作,独占写操作会继续执行,来完成独占访问。从机返回EXOKAY响应到主机。

AXCACHE[3:0]的值必须保证监控独占访问的从机要能看见事物。例如,一个正在被从机监控的独占访问不能具有一个表示该事物是可高速缓存的AXCACHE[3:0]值。

锁定访问

当一个事物的AXLOCK[1:0]信号表示该事物是一个锁定的传输时,互联必须确保只有发送该事物的主机才能被允许访问从机区域,直到从同一个主机发出的一个非锁定传输完成。互联中的仲裁器用来执行该限制。

当主机开始一个锁定事物,主机必须保证没有其他outstanding事物在等待完成。当结束一个锁定序列时,主机必须保证所有之前锁定事物都完成后才能发送最后一个非锁定的事物。之后,主机必须确保最后一个非锁定的事物已经完全完成,之后才能开始其他事物。

锁定访问要求互联在锁定序列处理期间要阻止任何其他事物的发生,因此会对互联的性能产生影响。 推荐锁定访问仅用于支持legacy设备。

2.6 AXI乱序

乱序交易可以在两个方面提高系统系能:

- 1、互连设备可以使快速响应的从设备交易完成早于较慢速度的从设备;

- 2、复杂的从设备可以乱序返回读数据。例如,较晚访问的数据可能因为来自内部缓冲器而比先前访问的数据更早获得。

-

-

2.7 AXI低功耗

低功耗接口是数据传输协议的可选扩展,这种数据传输协议目标是两类不同的外设:

· 请求一个断电序列,并且只有当进入一个低功耗状态时才能关闭其时钟的外设。这种外设从一个系统时钟控制器请求一个标识,来判定何时启动一个断电序列。

· 不具有断电序列,并且其可以独立标示何时可以关闭其时钟的外设。

低功耗时钟控制接口包含以下信号:

· 一个来自外设的信号,表示其时钟何时可以被使能或禁止;

· 两个握手信号,用于系统时钟控制器请求退出或进入一个低功耗状态;

时钟控制接口中的主要信号是CACTIVE。外设使用该信号来表示其何时请求时钟被使能。外设断言CACTIVE来表示请求时钟,外设取消断言CACTIVE来表示没有请求时钟。

对于需要断电和上电序列的更复杂的外设,只有从系统时钟控制器发出请求之后才能进入一个低功耗状态。AXI协议提供了一个2线的请求/确认握手来实现这个请求:

CSYSREQ:为了请求外设进入一个低功耗状态,系统时钟控制器驱动CSYSREQ信号为低。在正常操作期间,CSYSREQ为高。

CSYSACK:外设使用CSYSACK信号来确认低功耗状态请求和退出低功耗状态。

外设可以接受或拒绝来自系统时钟控制器的低功耗请求。当外设通过取消断言 CSYSACK 来确认请求时,CACTIVE信号的电平表明外设接受或拒绝请求。

在低功耗期间,CACTIVE和CSYSREQ信号都为低,通过驱动这两个信号中的一个为高来启动退出序列。

3. AHB

3.1 传输类型

HTRAN表示传输类型,AHB总线有4中传输类型,分别为空闲(IDLE)、忙(BUSY)、非连续(NONSEQ)、连续(SEQ)。

空闲(IDLE):表示没有数据传输的要求。在主机被授予总线,但并不希望执行一个数据传输时使用。从机必须总是提供一个零等待状态OKAY来响应空闲传输并且该传输应该被从机忽略。

忙(BUSY):忙传输类型允许总线主机在突发传输中间插入空闲周期。这种传输类型表示总线主机正在连续执行一个突发传输,但是下一次传输不能立即发生。当一个主机使用忙传输类型时地址和控制信号必须反映突发中的下一次传输。这种传输应该被从机忽略。从机必须总是提供一个零等待状态 OKAY 响应,和从机响应空闲传输一样的方式。

非连续(NONSEQ):表示一次突发的第一个传输或者一个单一传输。地址和控制信号和前一次传输无关。总线上的单一传输被视为(数据量为)一个的突发因此传输类型是非连续的。

连续(SEQ):突发中剩下的传输是连续传输并且地址是和前一次传输有关的。控制信息和前一次传输一样。地址等于前一次传输的地址加上传输大小(字节)。在回环突发的情况下传输地址在地址边界处回环,回环值等于传输大小乘以传输的次数。

3.2 突发操作

AMBA AHB定义了四次、八次和十六次袭发,突发禁止超过1KB的地址边界。

对从机设计而言,如果突发提前终止那么利用突发信息能够采取正确的动作显得很重要。从机能够通过监控HTRANS信号决定一个突发何时提前终止并且确保在突发开始之后每次传输有连续或者忙的标记。如果产生一个非连续或者空闲传输那么这表明一个新的突发已经开始因此前一次突发一定已经终止。如果总线主机因为失去对总线的占有而不能完成一次突发那么它必须在下一次获取访问总线时正确地重建突发。

3.3 控制信号

HWRIT:传输方向。为高表示写传输并且主机将数据广播到写数据总线HWDATA。为低时将执行一个读传输并且从机必须产生数据到读数据总线HRDATA。

HPROT[3:0]:保护控制信号,提供总线访问的附加信息给那些希望执行某种保护级别的模块使用。

HPROT[0]:0预取指令,1数据访问;

HPROT[1]:0用户模式访问,1特权模式访问;

HPROT[2]:0无缓冲,1有缓冲;

HPROT[3]:0无高速缓存,1有高速缓存;

3.4 传输响应

HREADY信号被用来扩展传输并且和信号HRESP[1:0]相结合,提供传输状态。从机能够用许多种方式来完成传输。它能:

- 立刻完成传输;

- 插入一个或者多个等待状态以允许有时间来完成传输;

- 发出一个错误信号来表示传输失败;

- 延时传输的完成,但是允许主机和从机放弃总线,把总线留给其他传输使用。

ERROR:被从机用来表示某种形式的错误条件和相关的传输。典型的这被用作保护 错误,例如试图写一个只读的存储空间。

RETRY:传输并未完成,因此总线主机应该重试传输。主机应该继续重试传输直到完成为止。要求双周期的RETRY响应。

SPLIT:传输并未成功完成。总线主机必须在下一次被授予访问总线时重试传输。当传输能够完成时从机将请求代替主机访问总线。要求双周期的SPLIT响应。

分块和重试响应给从机提供了在无法立刻给传输提供数据时释放总线的机制。这两种机制都允许在总线上结束传输因此允许更高优先级的主机能够访问主机。不同之处在于仲裁器在发生SPLIT和RETRY后分配总线的方式:

- 对RETRY而言仲裁器将继续使用常规优先级方案因此只有拥有更高优先级的主机将获准访问总线;

- 对于SPLIT传输而言仲裁器将调整优先级方案以便其他任何主机请求总线即能获得访问(总线),即使是优先级较低的主机。为了完成一个SPLIT传输从机必须通知仲裁器何时数据可用。

SPLIT传输都增加了仲裁器和从机的复杂性,但是却有可以完全释放总线给其他主机使用的优点,但是 RETRY(响应)的情况就只允许较高优先级的主机使用总线。总线主机应该以同样的方式来对待SPLIT和RETRY(响应)。主机应该继续请求总线并尝试传输直到传输成功完成或者遇到ERROR响应时终止。

ERROR、SPLIT和RETRY响应需要至少两个周期。倒数第二个周期从机驱动HRESP以表示ERROR、RETRY或者SPLIT并同时驱动HREADY为低以给传输扩展一个额外的周期。在最后一个周期HREADY被驱动为高电平以结束传输,同时HRESP保持驱动以表示ERROR、RETRY或者SPLIT。

如果从机需要两个以上的周期以提供ERROR、SPLIT或者RETRY响应那么额外的等 待状态可能会在传输开始时被插入。在这段时间HREADY信号将为低电平同时响应必须被设为OKAY。

3.5 仲裁

仲裁机制被用来确保任意时刻只有一个主机能够访问总线。仲裁器的功能是检测许多不同的总线请求和决定当前请求总线的主机中哪一个的优先级最高。仲裁器也接收来自从机需要完成SPLIT传输的请求。

HBUSREQx:被总线主机用来请求访问总线的总线请求信号。一个系统中都可以有高达16个独立的总线主机。

HLOCKx:由主机在请求总线的同时时断言的锁定信号。提示仲裁器主机正在执行一系列不可分割的传输并且一旦锁定传输的第一个传输已经开始仲裁器不能授予任何其他主机访问总线。

HGRANTx:授予信号由仲裁器产生并且表示相关主机是当前请求总线的主机中优先级最高的主机,(优先)考虑锁定传输和 SPLIT 传输。

HMASTER[3:0]:表示哪一个主机当前被授予总线并且该信号可被用来控制中央地址和控制多路选择器。有SPLIT传输能力的从机也可以请求主机的序号以便它们能够提示仲裁器哪个主机能够完成一个SPLIT传输。

HMASTLOCK:指示当前传输是一个锁定序列的一部分,该信号和地址以及控制信号有相同的时序。

HSPLIT[15:0]:被有分块(SPLIT)能力的从机用来指示哪个总线主机能够完成一个SPLIT传输。仲裁器需要这些信息以便于授予主机访问总线完成传输。

4. NOC

NOC有自己的协议,所以挂在NOC上的IP需要有一个协议转换,就是NIU。CCI是ARM core的一致性总线,主要负责多核工作过程中的一致性问题,一般在core和ddr交互之间,防止多核工作效率低下的问题。

NOC的通路结构分为initiator NIU,transport,target NIU。其中transport部分主要实现switching & routing(数据通路合并分流),同时包括clock adapter(跨时钟)、位宽转换、数据缓冲、打拍等操作。

从进入Generic Interface开始,noc总线的读写通道共用同一组数据线,共享连线和寄存器。NOC基于packet传输,使用NTTP协议,req和resp通道对称,使用相互独立的数据通路、连线和寄存器。

NIU的全称是Network Interface Unit,分为specific NIU和generic NIU。

specific NIU特性:

- 协议转换,AXI4和NTTP协议转换

- 读写通道合并为1路,round robin arbitration

- Flow Mapping,基于initiator和target的连接关系和地址空间映射

- Sequence Mapping,基于AXI ID和RoB配置

generic NIU特性:

- 地址译码

- 传输拆分

- 传输保序QoS

NTTP协议传输特性:

- NTTP的全称是NOC Transaction and Transport Protocol

- 基于packet传输,分为header控制信息和payload数据信息

- 基于vld和rdy信号握手,tail信号标志传输完成

- Header和payload信号都是并行传输,也可以设置为串行传输