描述

请设计带有空满信号的同步FIFO,FIFO的深度和宽度可配置。双口RAM的参考代码和接口信号已给出,请在答案中添加并例化此部分代码。

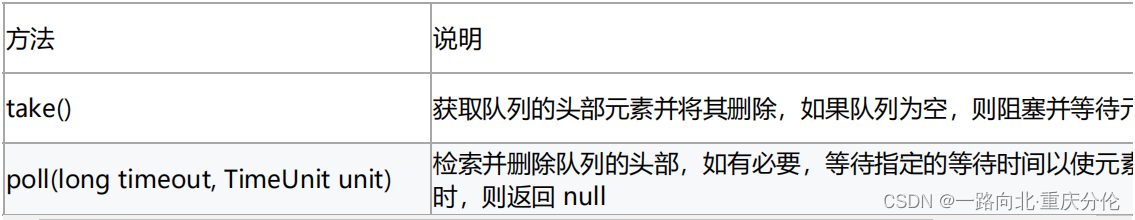

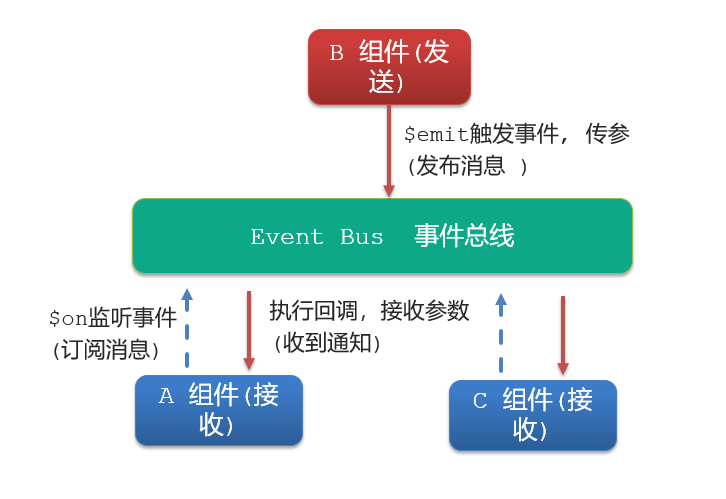

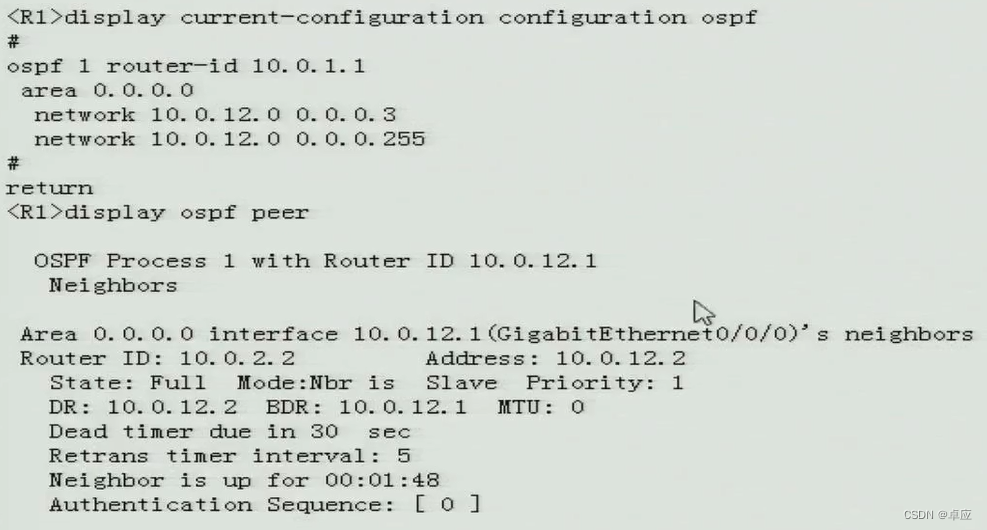

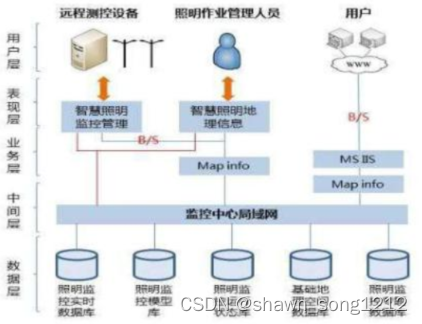

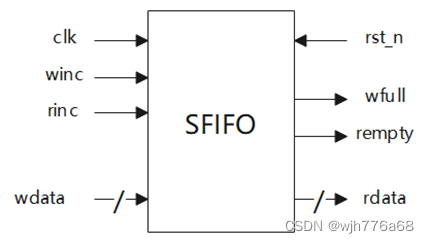

电路的接口如下图所示。端口说明如下表。

接口电路图如下:

双口RAM端口说明:

| 端口名 | I/O | 描述 |

|---|---|---|

| wclk | input | 写数据时钟 |

| wenc | input | 写使能 |

| waddr | input | 写地址 |

| wdata | input | 输入数据 |

| rclk | input | 读数据时钟 |

| renc | input | 读使能 |

| raddr | input | 读地址 |

| rdata | output | 输出数据 |

同步FIFO端口说明:

| 端口名 | I/O | 描述 |

|---|---|---|

| clk | input | 时钟 |

| rst_n | input | 异步复位 |

| winc | input | 写使能 |

| rinc | input | 读使能 |

| wdata | input | 写数据 |

| wfull | output | 写满信号 |

| rempty | output | 读空信号 |

| rdata | output | 读数据 |

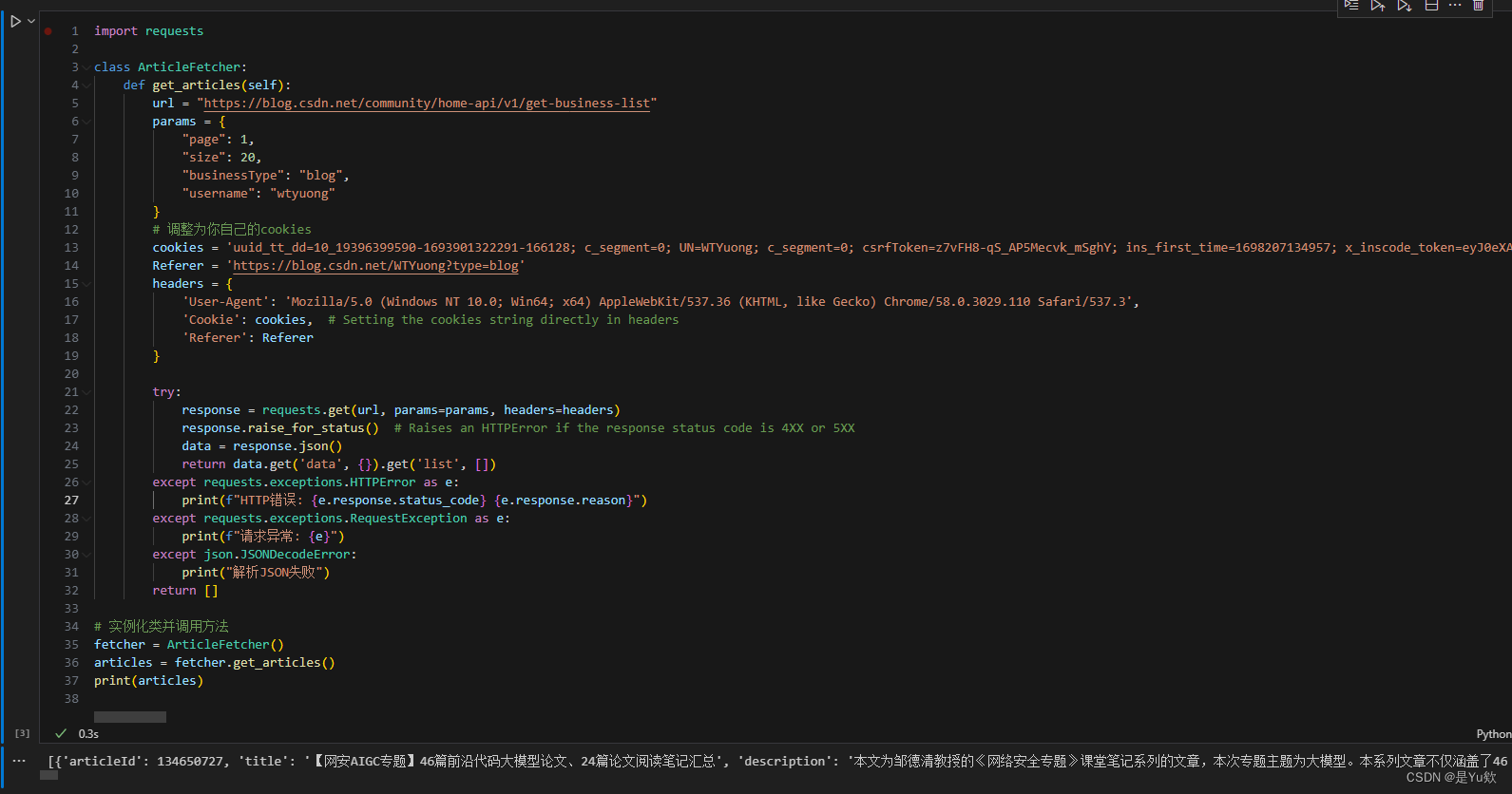

参考代码如下:

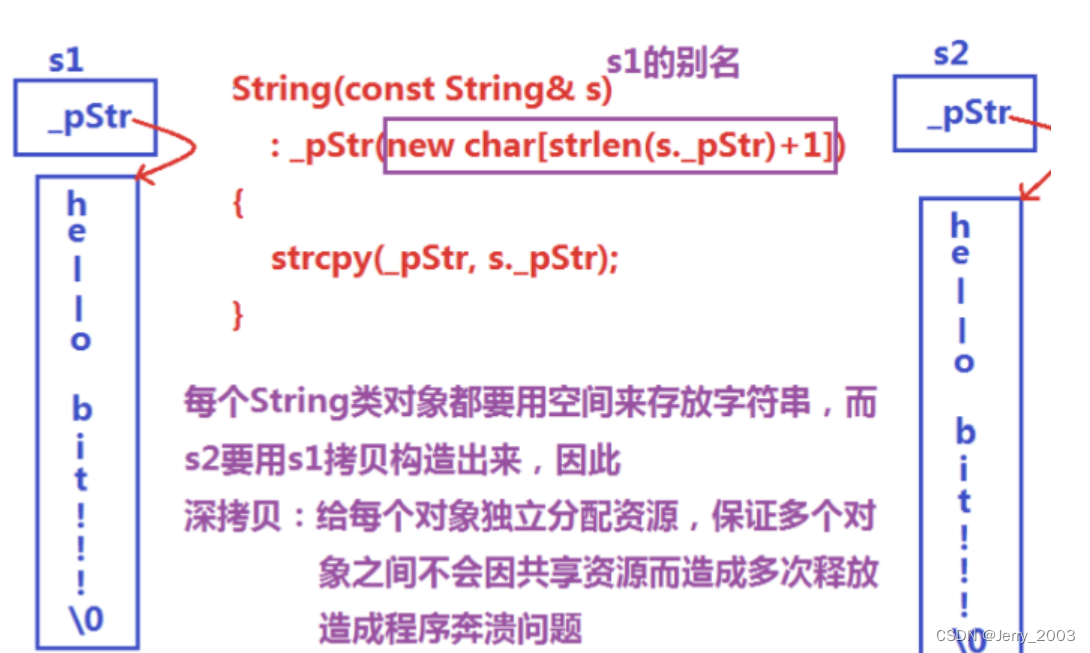

module dual_port_RAM #(parameter DEPTH = 16,parameter WIDTH = 8)(input wclk,input wenc,input [$clog2(DEPTH)-1:0] waddr ,input [WIDTH-1:0] wdata ,input rclk,input renc,input [$clog2(DEPTH)-1:0] raddr ,output reg [WIDTH-1:0] rdata

);reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];always @(posedge wclk) beginif(wenc)RAM_MEM[waddr] <= wdata;

end always @(posedge rclk) beginif(renc)rdata <= RAM_MEM[raddr];

end endmodule

输入描述:

input clk ,

input rst_n ,

input winc ,

input rinc ,

input wdata ,

输出描述:

output reg wfull ,

output reg rempty ,

output wire rdata

`timescale 1ns/1ns/**********************************RAM************************************/

module dual_port_RAM #(parameter DEPTH = 16,parameter WIDTH = 8)(input wclk,input wenc,input [$clog2(DEPTH)-1:0] waddr ,input [WIDTH-1:0] wdata ,input rclk,input renc,input [$clog2(DEPTH)-1:0] raddr ,output reg [WIDTH-1:0] rdata

);reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];always @(posedge wclk) beginif(wenc)RAM_MEM[waddr] <= wdata;

end always @(posedge rclk) beginif(renc)rdata <= RAM_MEM[raddr];

end endmodule /**********************************SFIFO************************************/

module sfifo#(parameter WIDTH = 8,parameter DEPTH = 16

)(input clk , input rst_n ,input winc ,input rinc ,input [WIDTH-1:0] wdata ,output reg wfull ,output reg rempty ,output wire [WIDTH-1:0] rdata

);localparam DEPTH_WIDTH = $clog2(DEPTH);reg [DEPTH_WIDTH : 0] rd_ptr_r = 'd0, wr_ptr_r = 'd0;wire fifo_wenc_s, fifo_renc_s;

wire [WIDTH-1:0] fifo_wdata_s, fifo_rdata_s;

reg [WIDTH-1:0] rdata_r;

reg fifo_wenc_r = 1'b0;assign fifo_wenc_s = ~wfull & winc;

assign fifo_renc_s = ~rempty & rinc;

assign fifo_wdata_s = wdata;

assign rdata = fifo_rdata_s; // always @(posedge clk, negedge rst_n) begin

// if (~rst_n) begin

// rdata_r <= 'd0;

// fifo_wenc_r <= 1'b0;

// end else begin

// fifo_wenc_r <= fifo_wenc_s;

// if (fifo_wenc_r) begin

// rdata_r <= fifo_rdata_s;

// end

// end

// endalways @(posedge clk, negedge rst_n) beginif (~rst_n) beginwr_ptr_r <= 'd0;end else beginif (~wfull & winc) beginwr_ptr_r <= wr_ptr_r + 1;endend

endalways @(posedge clk, negedge rst_n) beginif (~rst_n) beginrd_ptr_r <= 'd0;end else beginif (~rempty & rinc) beginrd_ptr_r <= rd_ptr_r + 1;endend

endalways @(posedge clk, negedge rst_n) beginif (~rst_n) beginrempty <= 'd0;wfull <= 'd0;end else beginrempty <= (rd_ptr_r == wr_ptr_r);wfull <= (rd_ptr_r[DEPTH_WIDTH] != wr_ptr_r[DEPTH_WIDTH]) && (rd_ptr_r[DEPTH_WIDTH - 1 : 0] == wr_ptr_r[DEPTH_WIDTH - 1 : 0]);end

enddual_port_RAM #(.DEPTH(DEPTH),.WIDTH(WIDTH)

) dual_port_RAM_inst( .wclk(clk) ,.wenc(fifo_wenc_s) ,.waddr(wr_ptr_r[DEPTH_WIDTH - 1 : 0]) ,.wdata(fifo_wdata_s) ,.rclk(clk) ,.renc(fifo_renc_s) ,.raddr(rd_ptr_r[DEPTH_WIDTH - 1 : 0]) ,.rdata(fifo_rdata_s)

);endmodule