Q:之前我们设计实现的逻辑电路最终输出结果都是通过LED显示,本篇我们将实现用七段数码管来显示输出结果。

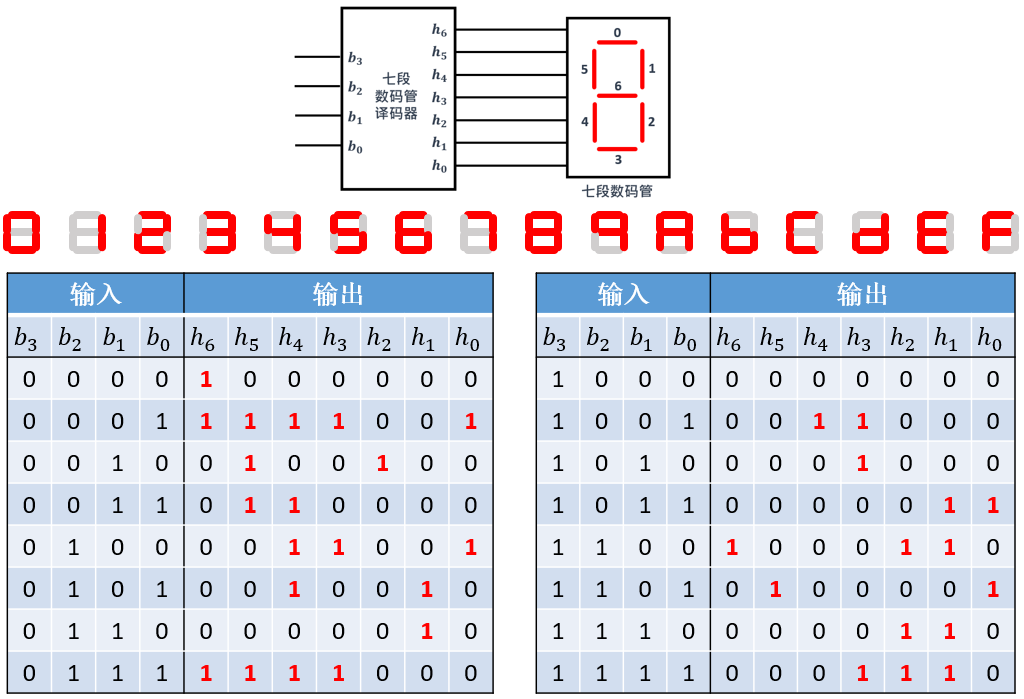

A:七段数码管显示基本原理:DE2-115开发板有8个共阳极数码管,即低电平逻辑值0点亮数码管段、逻辑值1来使数码管段熄灭。七段数码管译码器有4个输入端口,7个输出端口连接数码管的七个段。4个输入共有16种不同状态组合,对应十六进制数0~F。数码管显示比如0时,第6段是熄灭状态,给它的是高电平逻辑1,其他段都是点亮状态,给它们的是低电平逻辑0。

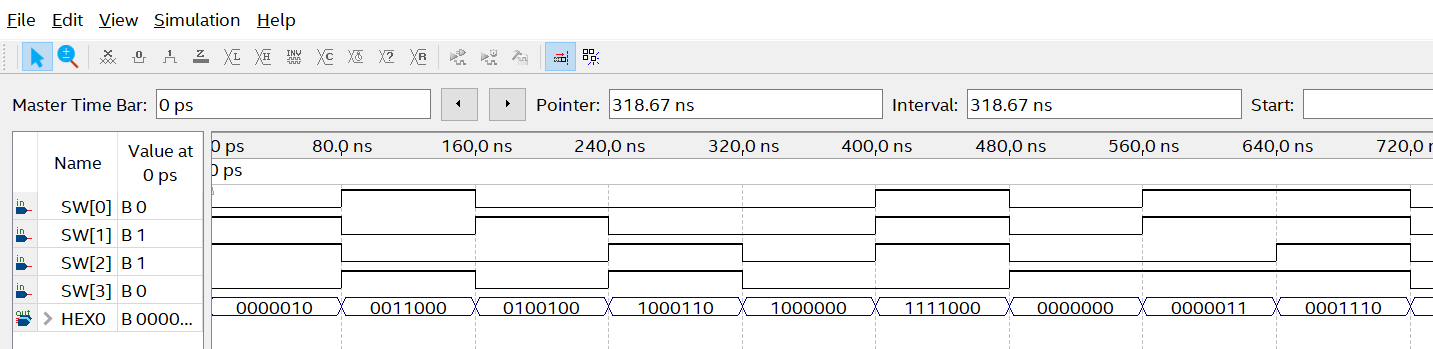

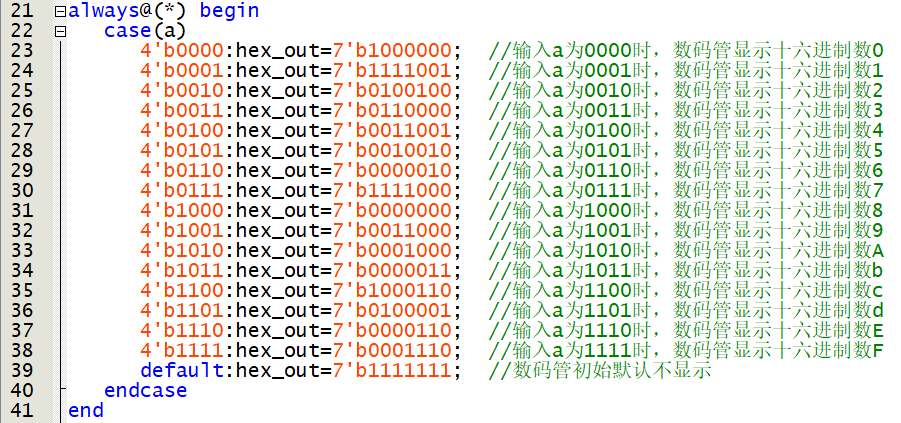

使用DE2-115开发板的SW[3:0]做为4位二进制数输入,在七段数码管HEX0上显示该4位二进制数表示的十六进制数值,这里我们使用Verilog case语句来描述逻辑功能。

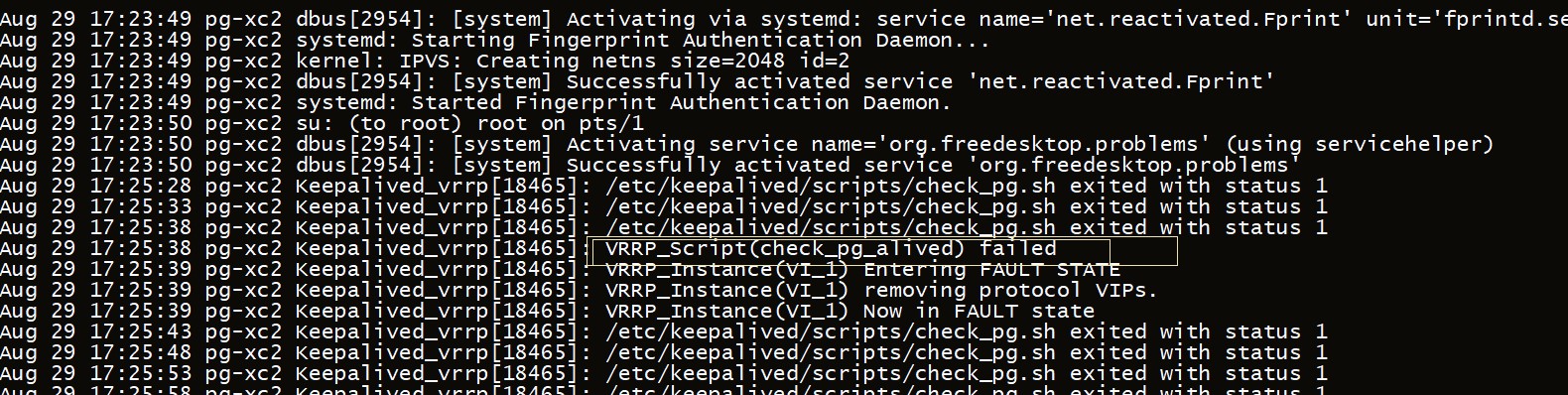

七段数码管译码器仿真结果: