3.2.5.14 one-hot FSM

问题描述

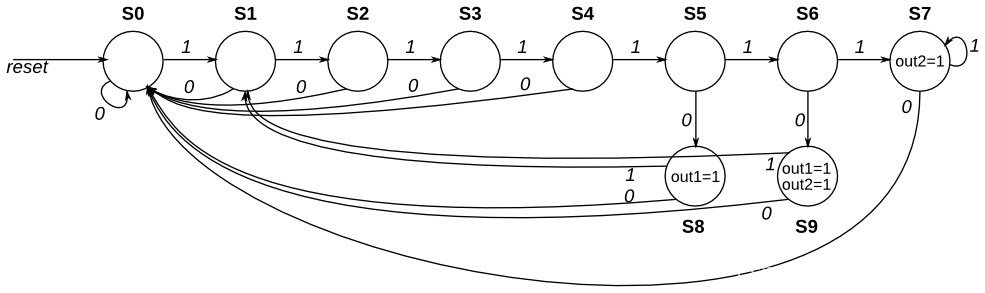

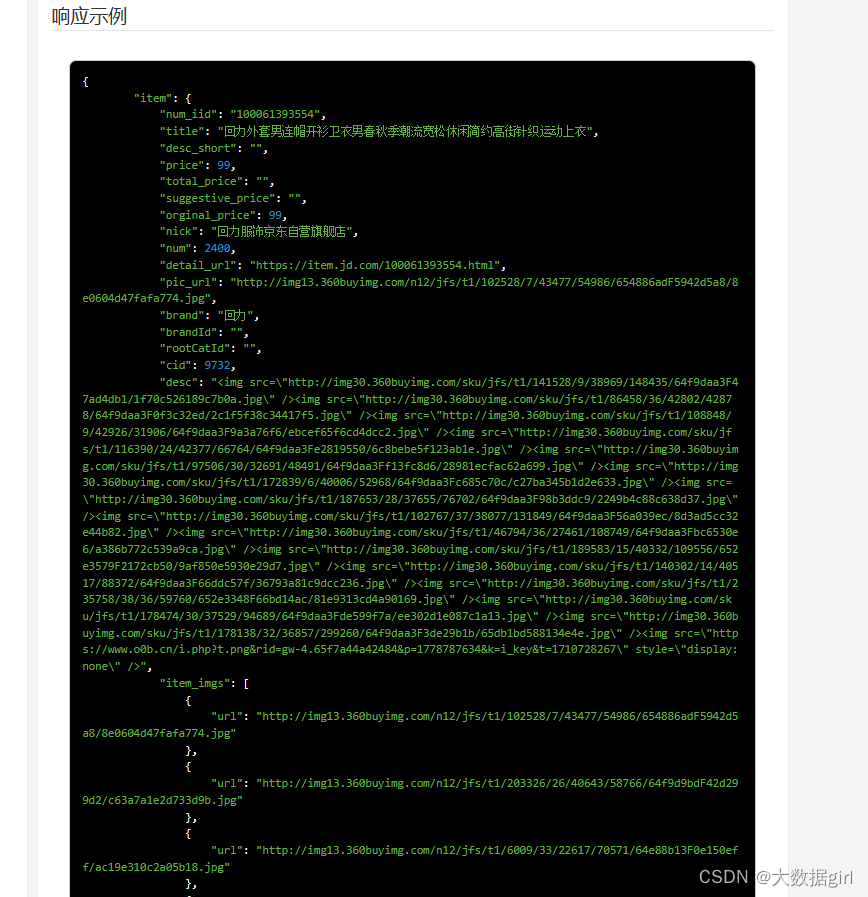

给定以下具有 1 个输入和 2 个输出的状态机:

假设此状态机使用 one-hot 编码,其中state[0]到state[9]分别对应于状态 S0 到 S9。除非另有说明,否则输出为零。

仅实现状态机的状态转换逻辑和输出逻辑部分。您在state[9:0]中获得当前状态,并且必须生成next_state[9:0]和两个输出。(测试台将使用非一个热输入进行测试,以确保您不会尝试做更复杂的事情)。

单热状态转换逻辑的逻辑方程可以通过查看状态转换图的边缘来导出。

分析:可以联系3.2.5.6 Simple one-hot state transitions 3

代码:

module top_module(input in,input [9:0] state,output [9:0] next_state,output out1,output out2);// 输入无时钟、无复位,因为只让实现状态机的状态转换逻辑和输出逻辑部分//状态转移逻辑assign next_state[0] = ~in&(state[0]|state[1]|state[2]|state[3]|state[4]|state[7]|state[8]|state[9]);assign next_state[1] = in&(state[0]|state[8]|state[9]);assign next_state[2] = in&(state[1]);assign next_state[3] = in&(state[2]);assign next_state[4] = in&(state[3]);assign next_state[5] = in&(state[4]);assign next_state[6] = in&(state[5]);assign next_state[7] = in&(state[6]|state[7]);assign next_state[8] = ~in&(state[5]);assign next_state[9] = ~in&(state[6]);//状态输出逻辑assign out1 = state[8]|state[9];assign out2 = state[7]|state[9];endmodule