用二进制译码器实现组合逻辑函数

原理

由于 n n n 位二进制译码器可提供 2 n 2^n 2n 个最小项的输出,而任一个逻辑函数都可变换为最小项之和的标准与或式,因此利用译码器和门电路可实现单输出及多输出组合逻辑电路

基本步骤

-

选择合适的集成二进制译码器(根据逻辑函数的变量的个数来选)

-

写出待求函数的标准与非-与非式(与或表达式两次取反)

-

确定待求函数变量和译码器输入端的关系

-

选择合适的门电路

当译码器输出低电平有效时,选用与非门

当译码器输出高电平有效时,选用或门 -

画连线图

应用举例

【例1】

用译码器和门电路实现逻辑函数 Y = F ( A , B , C ) = Y = F(A,B,C) = Y=F(A,B,C)= A ‾ \overline{A} A B ‾ \overline{B} B C C C + A A A B B B C ‾ \overline{C} C + C C C

-

Step1:根据逻辑函数选择译码器

分析:由于有 A 、 B 、 C A、B、C A、B、C 三个变量,故选用 3线-8线 译码器 74LS138

-

Step2:将函数变换为标准的与或式

Y Y Y = A ‾ \overline{A} A B ‾ \overline{B} B C C C + A A A B B B C ‾ \overline{C} C + C C C

= A ‾ \overline{A} A B ‾ \overline{B} B C C C + A A A B B B C ‾ \overline{C} C + C C C ( A ‾ + A ) (\overline{A}+A) (A+A) ( B ‾ + B ) (\overline{B}+B) (B+B)

= A ‾ \overline{A} A B ‾ \overline{B} B C C C + A A A B B B C ‾ \overline{C} C + A ‾ \overline{A} A B B B C C C + A A A B ‾ \overline{B} B C C C + A A A B B B C C C

= m 1 m_1 m1 + m 3 m_3 m3 + m 5 m_5 m5 + m 6 m_6 m6 + m 7 m_7 m7

也可以通过卡诺图一步到位

-

Step3:确定待求函数变量和译码器输入端的关系

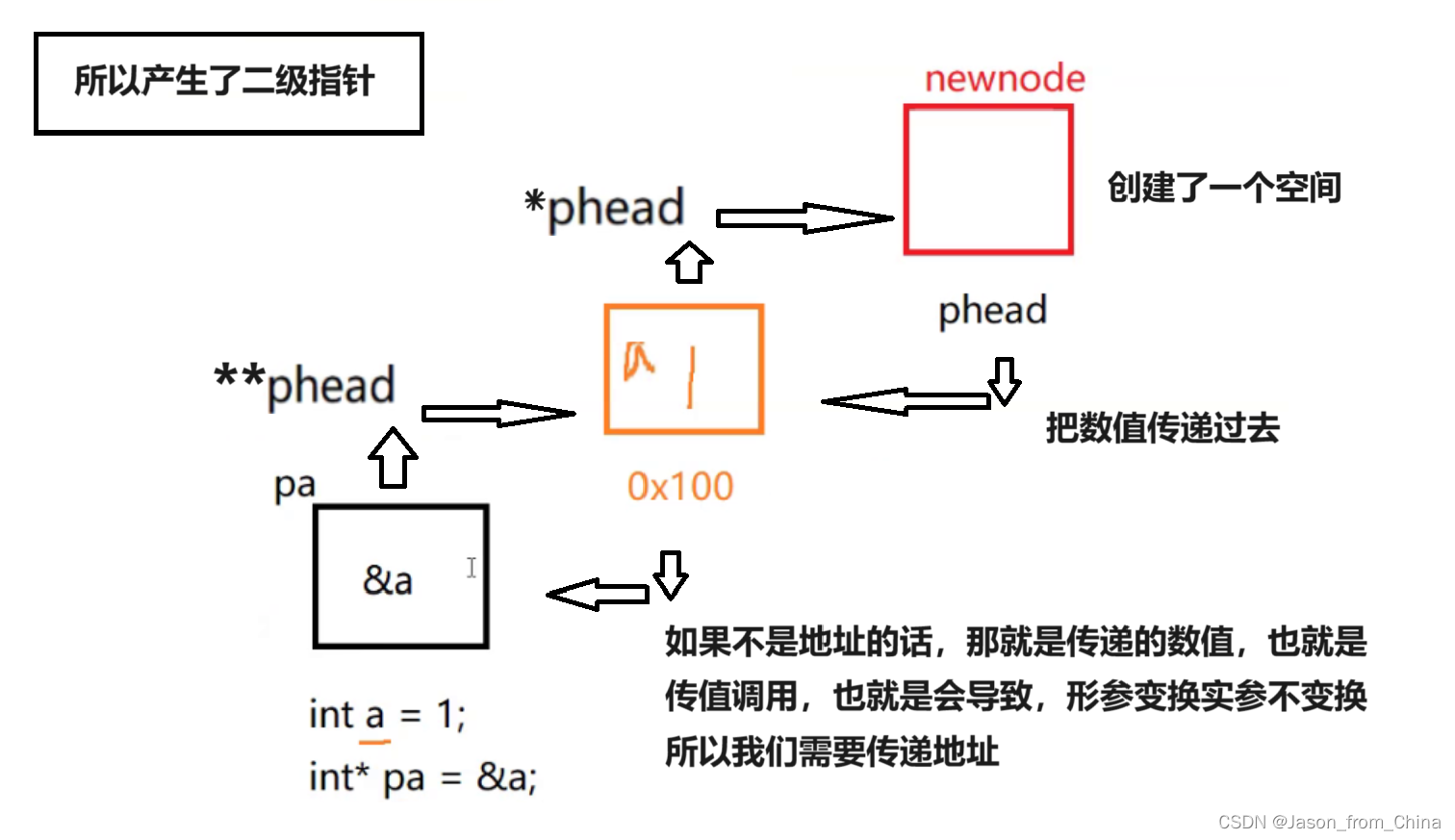

74LS138 输出低电平有效, Y i ‾ = m i ‾ \overline{Y_i} = \overline{m_i} Yi=mi

(以 A 2 、 A 1 、 A 0 A_2、A_1、A_0 A2、A1、A0 作为变量)将 F F F 变换为 F = m 1 + m 3 + m 5 + m 6 + m 7 ‾ ‾ = m 1 ‾ ⋅ m 3 ‾ ⋅ m 5 ‾ ⋅ m 6 ‾ ⋅ m 7 ‾ ‾ F=\overline{\overline{m_1+m_3+m_5+m_6+m_7}}=\overline{\overline{m_1}·\overline{m_3}·\overline{m_5}·\overline{m_6}·\overline{m_7}} F=m1+m3+m5+m6+m7=m1⋅m3⋅m5⋅m6⋅m7

(以 A 、 B 、 C A、B、C A、B、C 作为变量)令 A 2 、 A 1 、 A 0 A_2、A_1、A_0 A2、A1、A0 分别与 A 、 B 、 C A、B、C A、B、C 相对应,那么 F = Y 1 ‾ ⋅ Y 3 ‾ ⋅ Y 5 ‾ ⋅ Y 6 ‾ ⋅ Y 7 ‾ ‾ F=\overline{\overline{Y_1}·\overline{Y_3}·\overline{Y_5}·\overline{Y_6}·\overline{Y_7}} F=Y1⋅Y3⋅Y5⋅Y6⋅Y7

-

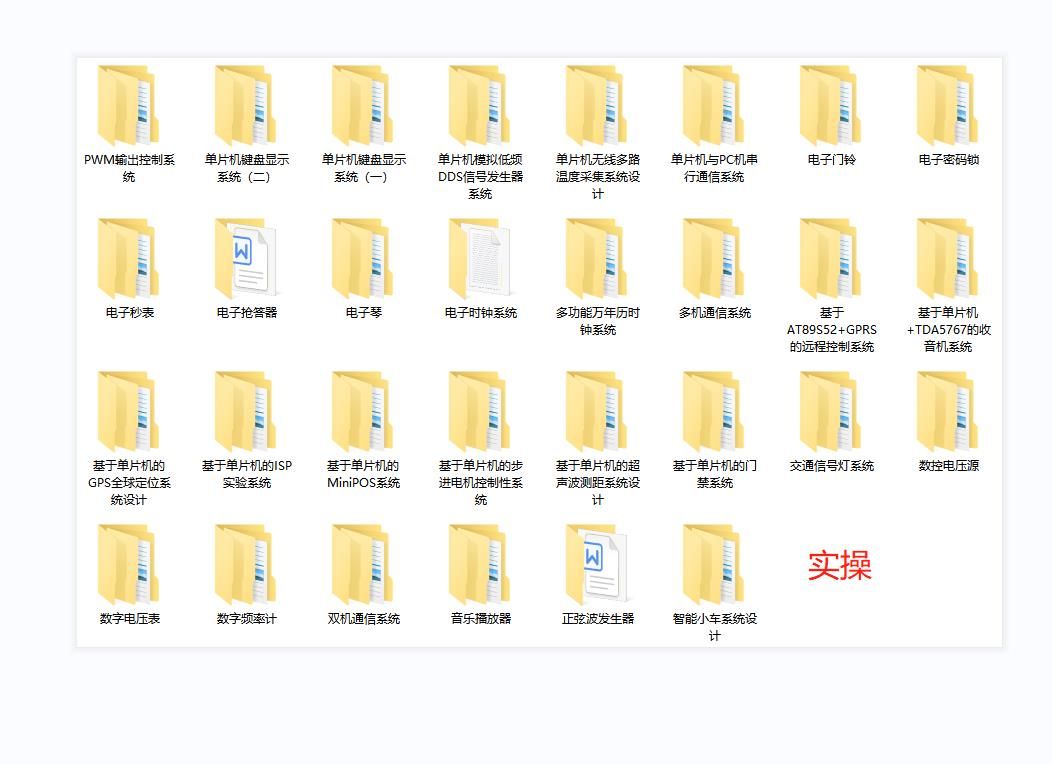

Step4:选择合适的门电路,画连线图

由Step3可知,在输出端需要增加一个5输入的与非门

【例2】

用 3线-8线 译码器 74LS138 和门电路设计一个多输出组合逻辑电路,其输出逻辑函数式为:

-

Step1:根据逻辑函数选择译码器

分析:由于有 A 、 B 、 C A、B、C A、B、C 三个变量,故选用 3线-8线 译码器 74LS138

-

Step2:将函数变换为标准的与或式

-

Step3:确定待求函数变量和译码器输入端的关系

-

Step4:选择合适的门电路,画连线图

【例3】

由 3线-8线 译码器 74LS138 和门电路设计组合逻辑电路如下图所示,写出输出 F F F 的最简与或式

直接使用卡诺图求解

F F F = C ‾ \overline{C} C + A ‾ \overline{A} A B ‾ \overline{B} B