当选择了动态重配置(Dynamic Reconfiguration)选项时,AXI4-Lite接口将默认被选中用于重新配置时钟组件。动态重新配置可以通过AXI4-Lite接口实现了Clocking Wizard IP核的时钟组件MMCM/PLL的动态重新配置。

如果需要直接访问MMCM/PLL的DRP寄存器,可以选择使用DRP接口。DRP接口提供了一种更为直接的方式来访问和控制MMCM/PLL等原语的内部寄存器。通过DRP接口,可以精确地控制原语的每个参数,以实现更高级别的配置和优化。然而,使用DRP接口可能需要更多的编程和调试工作,因为它涉及到对底层硬件的直接操作。

在选择使用AXI4-Lite接口还是DRP接口时,需要根据具体的应用需求进行权衡。如果需要快速、灵活地调整时钟组件的参数,并且不希望涉及过多的底层编程工作,那么AXI4-Lite接口可能是一个更好的选择。而如果需要更精确地控制组件的每一个参数,或者需要进行更复杂的配置和优化,那么DRP接口可能更适合。

当启用Dynamic Reconfig并且所选接口为AXI4-Lite时,此接口将被激活。但是,当启用扩频(Spread Spectrum)时,此功能不受支持。当使用AXI4-Lite接口时,该IP 核将提供混合语言的RTL(寄存器传输级)代码。

在实际应用中,通过AXI4-Lite接口进行动态配置可以使得时钟设置更加灵活和适应不同需求。例如,在需要频繁更改时钟配置的场景中,可以通过AXI4-Lite接口在运行时重新配置MMCM/PLL,而无需重启系统或重新加载配置。这对于需要快速响应变化的系统或需要动态调整性能的场景非常有用。

此外,AXI4-Lite接口的配置通常涉及到写地址总线、写数据总线以及相应的控制信号。通过这些接口,用户可以将新的配置数据写入到MMCM/PLL的控制寄存器中,从而实现动态配置。在配置过程中,还需要注意时钟的稳定性以及配置的正确性,以避免对系统造成不良影响。

1 重新配置相位和占空比

如果Phase Duty Cycle Config未启用,clocking wizard将仅调用与频率相关的函数。为了动态更改相位和占空比,必须启用此选项。然后,clocking wizard会调用与相位和占空比相关的函数,但这会消耗资源。如果资源无法使用,可以在IP生成期间使用clocking wizard调用这些功能,并编写一个包含直接DRP数据的不同地址集。在此过程中,clocking wizard不会进行任何计算,而是指导用户将所需的值写入寄存器。要启用此功能,必须选择“Write DRP registers”。

在实际应用中,动态调整相位和占空比对于优化信号质量、降低功耗或实现更复杂的时序控制至关重要。通过启用Phase Duty Cycle Config,并结合使用clocking wizard生成的代码和DRP数据,可以实现对FPGA时钟信号的精确控制。

2 动态重新配置的步骤

要进行动态重新配置,请按照以下步骤操作:

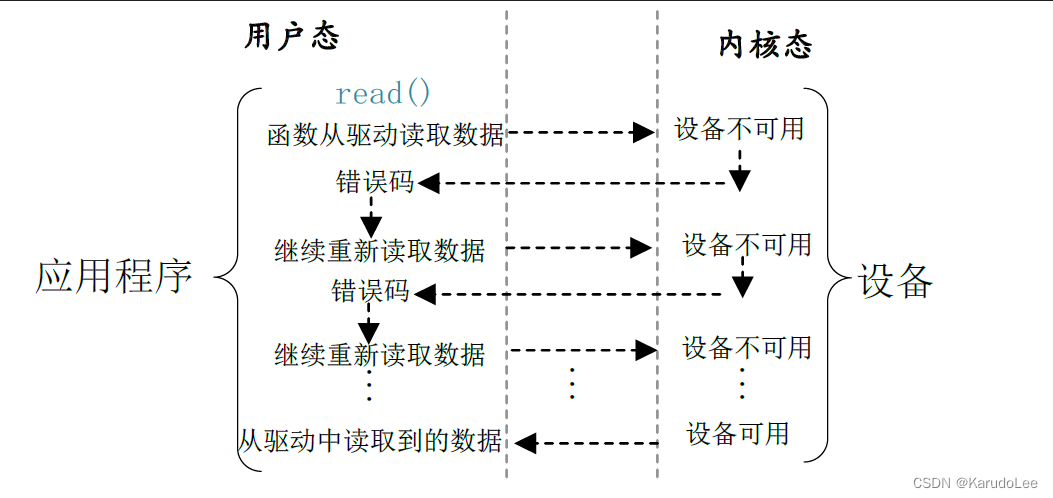

①写入所有时钟配置寄存器,然后检查状态寄存器。

②在向C_BASEADDR + 0x200寄存器写入之前,确保这些值能够产生MMCM/PLL的有效VCO频率范围。VCO频率通过以下公式计算得出:

VCO频率 = (输入时钟频率) * (CLKFBOUT_MULT) / DIVCLK_DIVIDE

③如果状态寄存器值为0x1,则通过向时钟配置寄存器23写入0x3来启动重新配置。

注意!只有在时钟FBOUT MULT的值不是整数时,才应启用时钟配置寄存器0中的小数使能位。同样,只有在CLKOUT0_DIVISE的值不是整数时,才应启用时钟配置寄存器2中的小数使能位。

遵循这些步骤,就可以安全有效地对FPGA中的MMCM或PLL进行动态重新配置。在重新配置过程中,确保仔细检查和验证所有输入值,以避免超出设备的规格或造成不稳定情况。

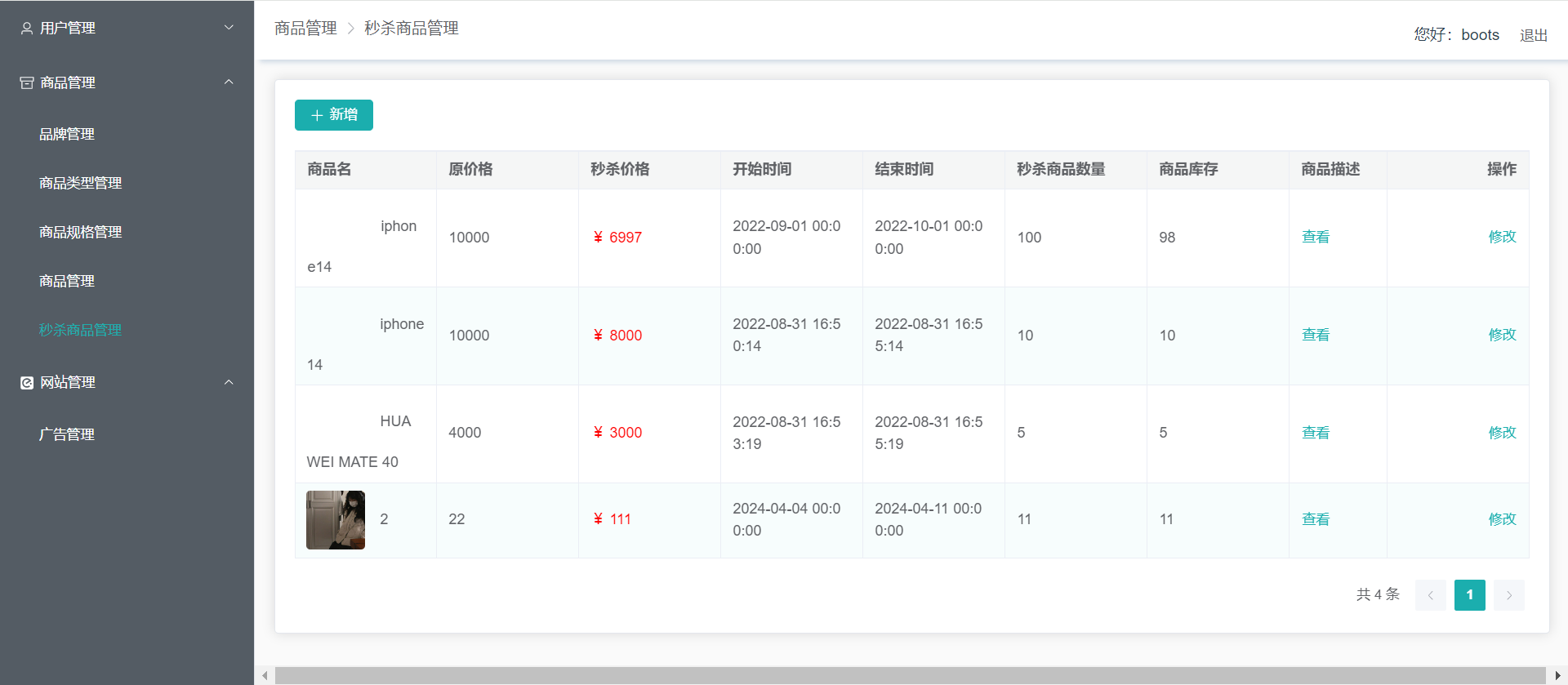

3 Write DRP registers

此功能的主要优势在于避免在clock IP核中使用DSP。该选项可以在动态重新配置模式下选择,并且仅对AXI4-Lite接口有效。此功能允许通过AXI直接写入基本寄存器。当选择此功能时,IDE中将启用一个选项卡,其中列出了寄存器地址和需要写入的值。

要执行此功能,请按照以下步骤操作:

①生成Clocking Wizard IP。启用动态重新配置选项,并选择“Write DRP registers”功能。

②使用相同的输入时钟和所需的功能打开另一个Clocking Wizard。

③根据动态重新配置的需要,在Vivado IDE的“输出时钟”选项卡中更改输出时钟功能。

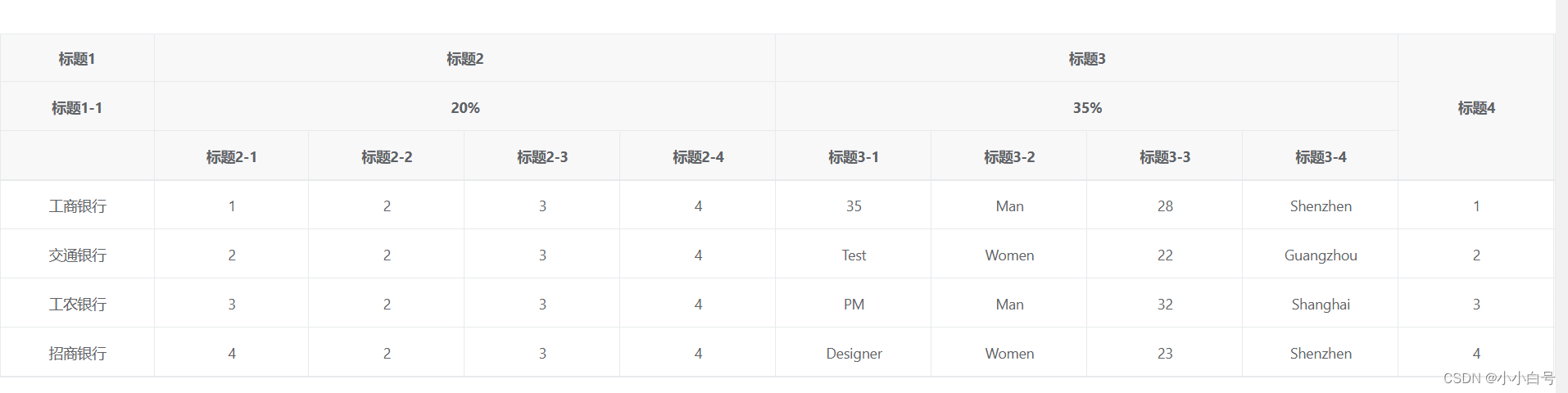

④写入DRP寄存器选项卡中的表格会根据所需的时钟进行更新。使用这些寄存器集值来动态重新配置初始的Clocking Wizard。