1 实验任务

上位机通过网口调试助手发送数据给 FPGA , FPGA 通过 PL 端以太网接口接收数据并将接收到的数据发送给上位机,完成以太网 UDP 数据的环回。

2 系统设计

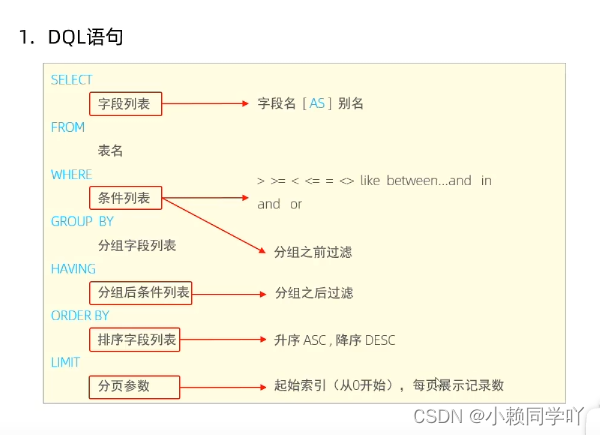

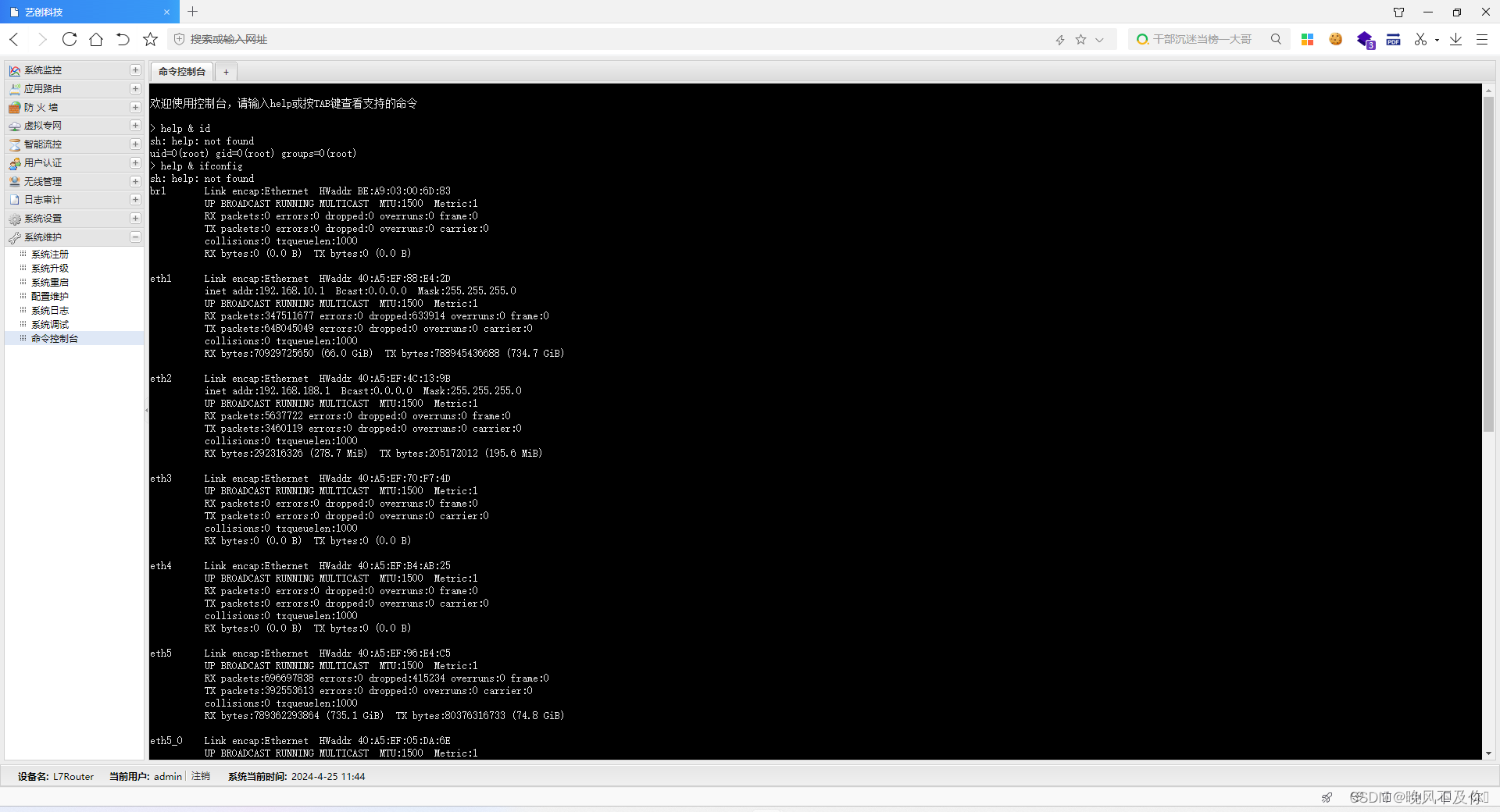

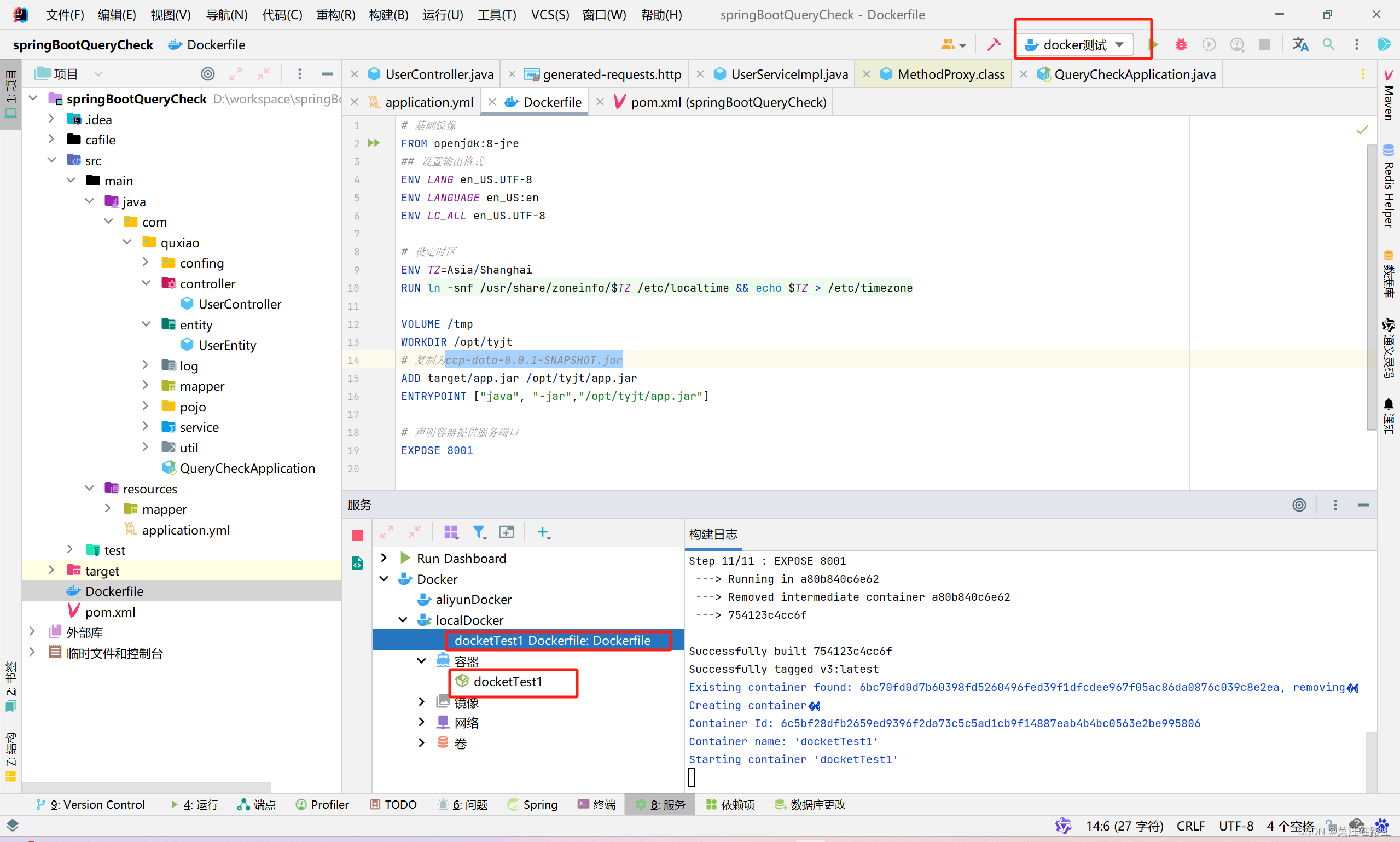

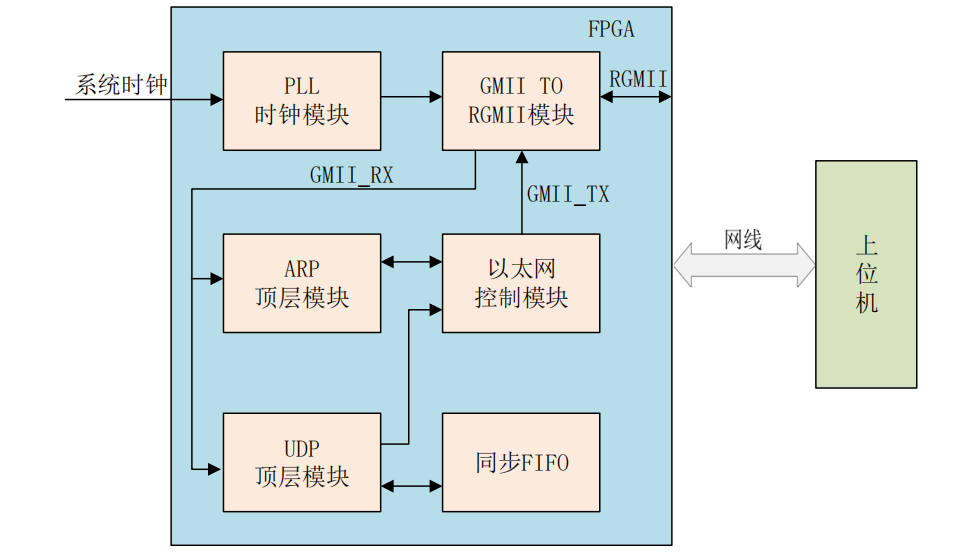

系统时钟经过PLL时钟模块后,生成了两种不同频率和相位的时钟信号:一种是200MHz的时钟信号,用作IDELAYCTRL原语的参考时钟;另一种是125MHz但偏移了90度的时钟信号,用作RGMII发送数据的时钟。

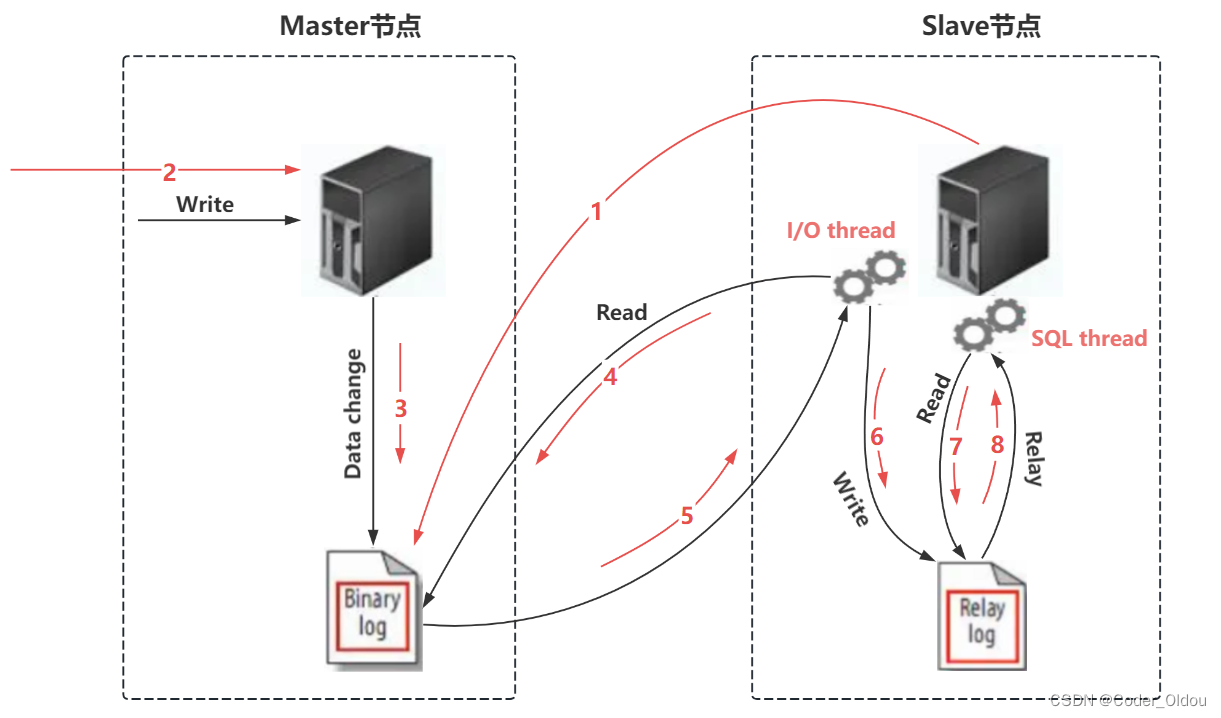

GMII TO RGMII模块负责将双沿(DDR)数据和单沿(SDR)数据之间进行转换。ARP顶层模块负责解析收到的ARP请求命令,并返回开发板的MAC地址。以太网控制模块根据接收到的ARP完成信号类型来控制ARP顶层模块返回ARP应答信号,并根据当前接收到的协议类型,选择切换ARP顶层模块和UDP顶层模块的GMII发送侧引脚。

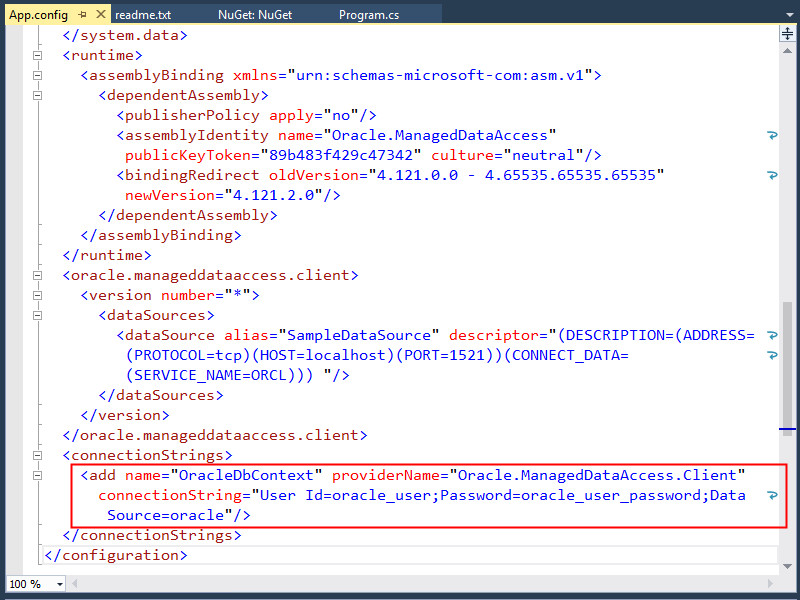

UDP顶层模块实现了以太网UDP数据包的接收、发送以及CRC校验的功能。同步FIFO模块使用Vivado软件自带的FIFO IP核生成,其大小为2048个32bit。为了满足单包数据量较大的情况(尽管通常情况下,以太网帧有效数据不超过1500个字节),FIFO的深度设置为2048,宽度为32位。