目录

1. 简介

2. MAXI 突发传输详解

2.1 突发传输的前置条件

2.2 hls::burst_maxi 详解

2.2.1 基本知识

2.2.2 hls::burst_maxi 构造函数

2.2.3 hls::burst_maxi 读取方法

2.2.4 hls::burst_maxi 写入方法

2.3 示例一

2.4 示例二

3. 总结

1. 简介

这篇文章探讨了在《Vitis HLS 学习笔记--AXI4 主接口-CSDN博客》中介绍的AXI4主接口的突发传输。虽然适用于HLS工具能够自动推断突发传输的情况,但并非所有情况工具都能自动推断。文章提供了详细的操作方法和示例,帮助读者在各种情况下优化存储器访问。

2. MAXI 突发传输详解

2.1 突发传输的前置条件

突发前置条件

突发就是对连续的内存空间请求访问。突发必须满足下列前置条件才能成功启动突发最优化:

- 请求必须全部为读取请求或者全部为写入请求。

- 访问必须按单调递增顺序。

- 访问必须为连续的内存空间,如果有两个存储器,它们之间需按正序彼此相邻且无间隔或重叠。

- 读取/写入访问的次数(或突发长度)必须可在发出请求之前确定。要么编译时确定,如果在运行时计算得到突发长度,必须在发出读取/写入请求之前完成计算。

- 如果将两个阵列绑定到同一个 M-AXI 端口,那么任意给定时间内,任一方向上最多仅针对一个阵列执行突发。

- 突发请求的发起时间与完成时间之间不得存在任何依赖关系问题。

2.2 hls::burst_maxi 详解

2.2.1 基本知识

Vitis HLS 可以执行自动突发最优化,从用户代码汇总循环/函数自动推断并优化存储器访问,并在单个突发请求内执行特定大小的读取/写入操作。但突发传输也有要求的,这些要求有时可能难以满足,或者 HLS 工具无法正确推断出用户的突发传输需求。

如果你发现 HLS 工具自动突发传输未按期望方式工作,并且无法按需对设计进行最优化,那么可以使用hls::burst_maxi 对象来实现读取和写入传输事务,即使用手动突发。

使用手动突发需要掌握熟悉 AXI4 m_axi 协议,并且理解硬件传输事务建模。

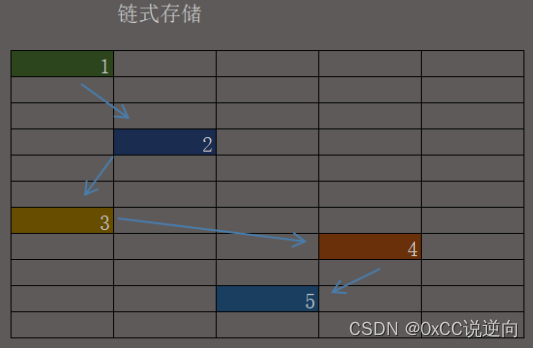

hls::burst_maxi 类工作原理

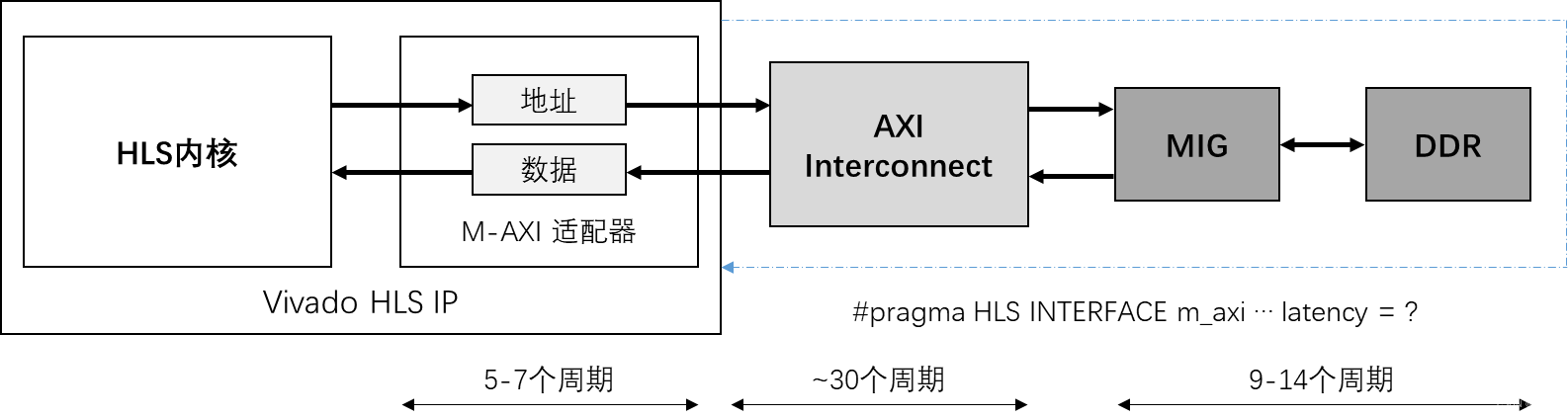

hls::burst_maxi 类可以实现对 DDR 执行读/写访问,它可以控制 AXI4 总线信号上发送和接收请求:AW、AR、WDATA、BVALID 和 RDATA,通过这些操作就可以控制 AXI 调度器的突发行为。适配器可从调度器接收命令,并负责向 DDR 发送数据。这些请求将遵循用户指定的 INTERFACE 编译指示选项,例如 max_read_burst_length 和 max_write_burst_length等。

注:hls::burst_maxi 类方法应仅在内核代码中使用,不得在测试激励文件中使用。

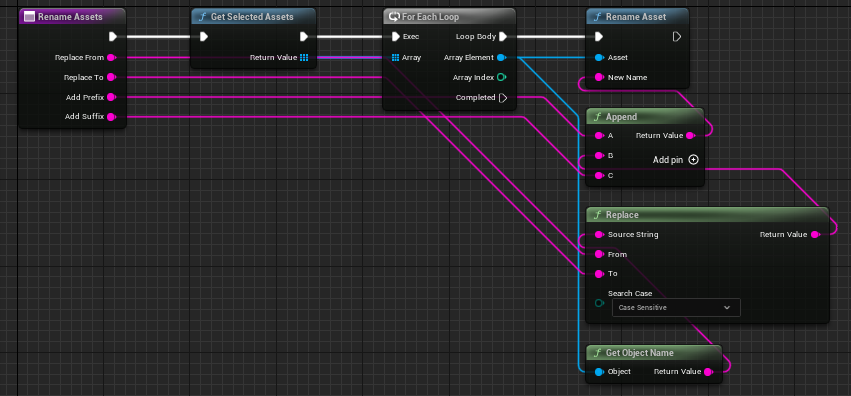

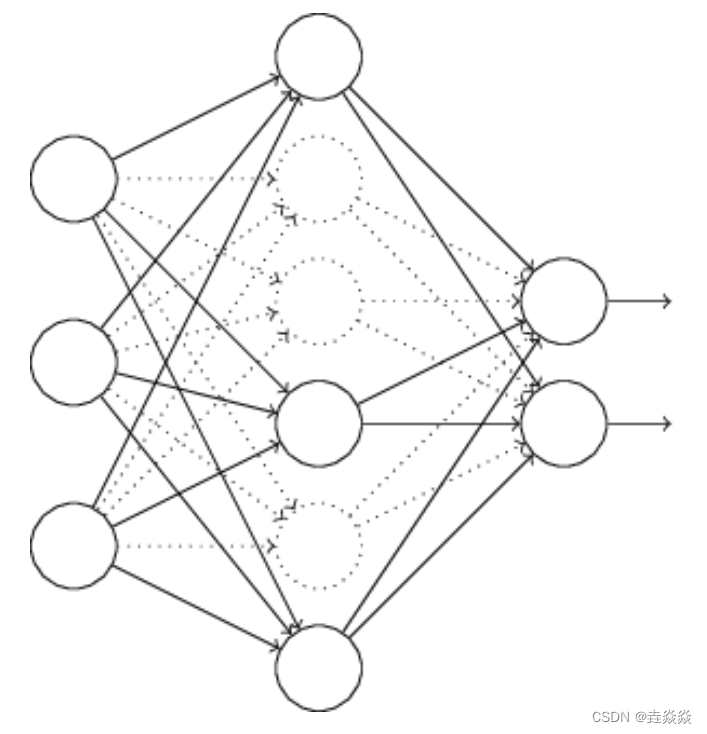

关于适配器和调度器请参见下图:

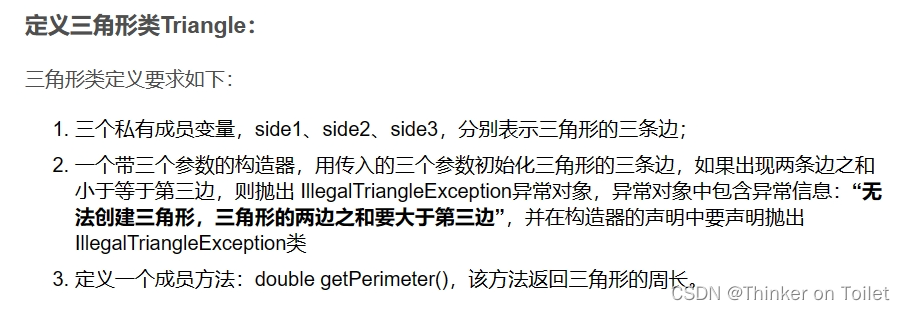

2.2.2 hls::burst_maxi 构造函数

burst_maxi(const burst_maxi &B) : Ptr(B.Ptr) {}

burst_maxi(T *p) : Ptr(p) {}2.2.3 hls::burst_maxi 读取方法

void read_request(size_t offset, size_t len);此方法用于对 m_axi 适配器执行读取请求。如果 m_axi 适配器内部的读取请求队列未满,那么该函数就会立即返回,否则它会等待至空间变为可用为止。

- offset:指定存储器偏移,将从该指定偏移位置读取数据

- len:指定调度器突发长度。此突发长度将发送至适配器,随后,适配器即可将其转换为标准 AXI AMBA 协议

T read();此方法用于将数据从 m_axi 适配器传输至调度器 FIFO。如果数据不可用,read() 将执行阻塞。read() 方法应调用 len 次,具体次数在 read_request() 中指定。

2.2.4 hls::burst_maxi 写入方法

void write_request(size_t offset, size_t len);此方法用于对 m_axi 适配器执行写入请求。如果 m_axi 适配器内部的写入请求队列未满,那么该函数就会立即返回。

- offset:指定存储器偏移,数据应写入该指定偏移位置

- len:指定调度器突发长度。此突发长度将发送至适配器,随后,适配器即可将其转换为标准 AXI AMBA 协议

void write(const T &val, ap_int<sizeof(T)> byteenable_mask = -1);此方法用于将数据从调度器的内部缓冲器传输到 m_axi 适配器。如果内部写入缓冲器已满,那么它会执行阻塞。byteenable_mask 用于在 WDATA 中启用字节。默认情况下,它将启用传输的所有字节。write() 方法应调用 len 次,具体次数在 write_request() 中指定。

void write_response();此方法会执行阻塞,直至从全局存储器返回所有写入响应为止。此方法的调用次数应与 write_request() 相同。

2.3 示例一

提供一个原始代码样本,它使用指针实参从全局存储器读取数据:

void dut(int *A) {for (int i = 0; i < 64; i++) {

#pragma pipeline II=1... = A[i]}

}修改代码,拆分A为 4 个请求(len 均为 16)从端口 A 放置到 m_axi 适配器上。

首先,指针需要被替换为 hls::burst_maxi<> 类。该适配器将其存储在 FIFO 内部,只要 AW/AR 总线可用,它就会将请求发送到全局存储器。其次,在 64 次循环迭代中,通过 read() 命令发出阻塞调用,调用将等待全局存储器返回的数据。最后,数据可用后,HLS 调度器将从 m_axi 适配器 FIFO 读取此数据。代码如下:

#include "hls_burst_maxi.h"

void dut(hls::burst_maxi<int> A) {// Issue 4 burst requestsA.read_request(0, 16); // request 16 elements, starting from A[0]A.read_request(128, 16); // request 16 elements, starting from A[128]A.read_request(256, 16); // request 16 elements, starting from A[256]A.read_request(384, 16); // request 16 elements, starting from A[384]for (int i = 0; i < 64; i++) {

#pragma pipeline II=1... = A.read(); // Read the requested data}

}2.4 示例二

void trf(hls::burst_maxi<int> A) {A.write_request(0, 2);A.write(x); // write A[0]A.write_request(10, 1);A.write(x, 2); // write A[1] with byte enable 0010A.write(x); // write A[10]A.write_response(); // response of write_request(0, 2)A.write_response(); // response of write_request(10, 1)

}

- 内核会将 2 个请求从端口 A 放置到适配器上,第一个请求的 len 为 2,第二个请求的 len 为 1,总计 2 个写入请求。

- 它会发出对应的请求,因为总计突发长度为 3 条写入命令。

- 适配器将这些请求存储在 FIFO 内部,只要 AW 和 WD 总线可用,它就会将请求和数据发送到全局存储器。

- 最后,使用 2 条write_response 命令等待 2 个 write_requests 的响应。

3. 总结

本文分享了在Vitis HLS中使用AXI4主接口进行手动突发传输的方法。首先,解释了突发传输的前置条件,包括请求类型、顺序、连续性等。接着,介绍了通过hls::burst_maxi对象实现手动突发传输的方法,包括构造函数、读取和写入方法的使用。本文还提供了两个示例,展示了如何使用该对象进行数据读取和写入,并解释了相应的过程。

![[软件工具]批量根据文件名查找PDF文件复制到指定的地方,如何批量查找文件复制,多个文件一起查找复制](https://img-blog.csdnimg.cn/img_convert/692bd908f35322a9272095f8fd0df5d0.webp?x-oss-process=image/format,png)