嵌入式Linux学习第四天

今天学习I.MX6U 启动方式详解。I.MX6U有多种启动方式,可以从 SD/EMMC、NAND Flash、QSPI Flash等启动。

启动方式选择

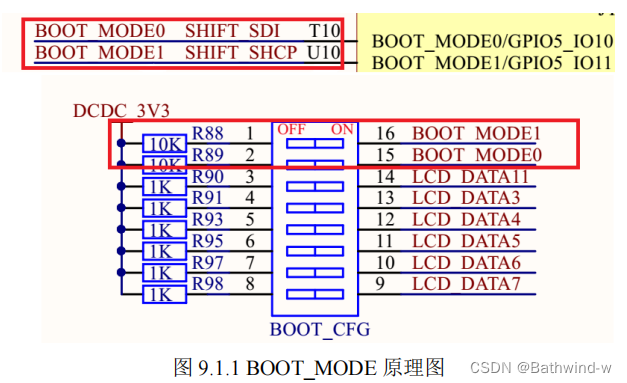

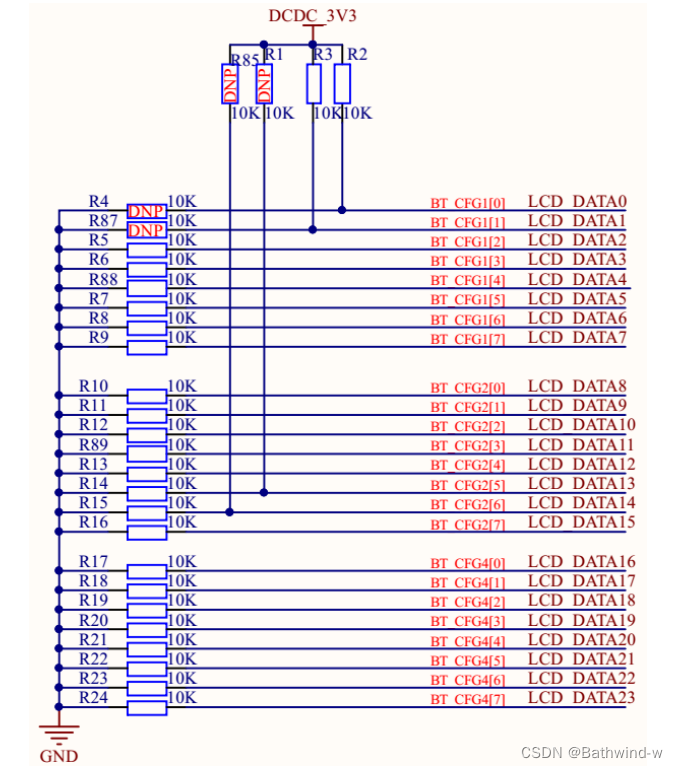

BOOT 的处理过程是发生在 I.MX6U 芯片上电以后,芯片会根据 BOOT_MODE[1:0]的设置来选择 BOOT 方式。BOOT_MODE[1:0]的值是可以改变的,I.MX6U-ALPHA 开发板的这两个引脚原理图如图所示:

I.MX6U 有四个 BOOT 模式,这四个 BOOT 模式由 BOOT_MODE[1:0]来控制,也就是BOOT_MODE1 和 BOOT_MODE0 这两个 IO,具体模式如下图所示:

串行下载

当 BOOT_MODE1 为 0,BOOT_MODE0 为 1 的时候此模式使能,串行下载的意思就是可以通过 USB 或者 UART 将代码下载到板子上的外置存储设备中,我们可以使用 OTG1 这个 USB口向开发板上的 SD/EMMC、NAND 等存储设备下载代码。我们需要将 BOOT_MODE1 拨到“OFF”,将 BOOT_MODE0 拨到“ON”。这个下载是需要用到 NXP 提供的一个软件,一般用来最终量产的时候将代码烧写到外置存储设备中的。

内部 BOOT 模式

当 BOOT_MODE1 为 1,BOOT_MODE0 为 0 的时候此模式使能,在此模式下,芯片会执行内部的 boot ROM 代码,这段 boot ROM 代码会进行硬件初始化(一部分外设),然后从 boot 设备(就是存放代码的设备、比如 SD/EMMC、NAND)中将代码拷贝出来复制到指定的 RAM 中,一般是 DDR。

内部 BOOT 模式分析

BOOT ROM 初始化内容

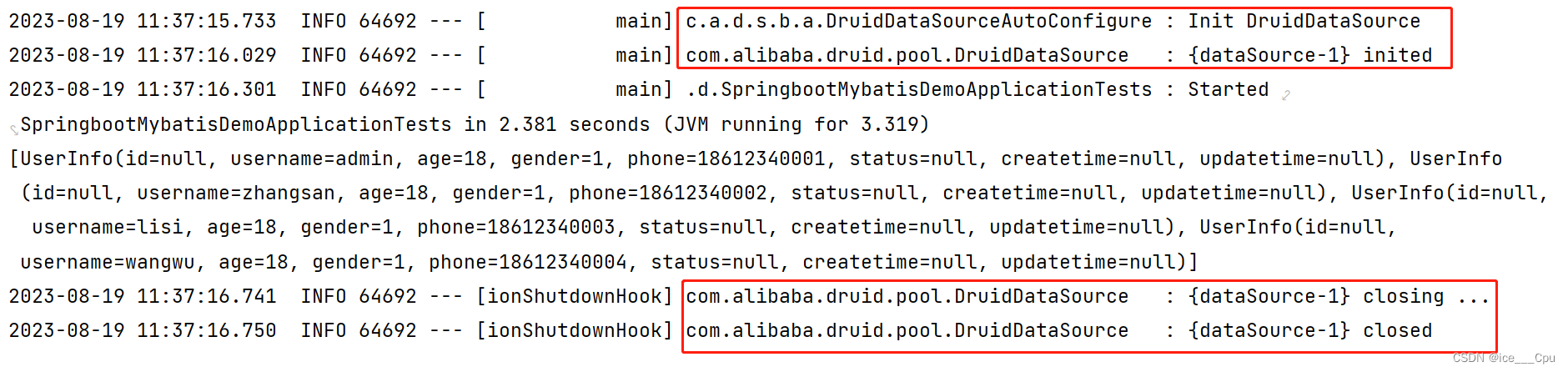

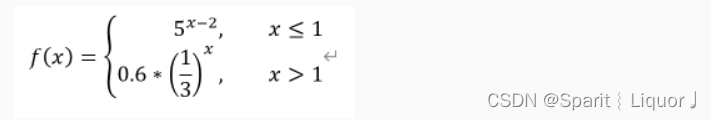

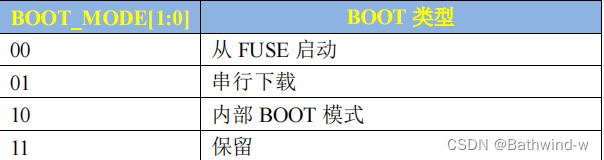

当初始化为内部boot模式时候,在电源上电或重置后,i.MX6UL 会首先执行内置的 Boot ROM 程序。这个 Boot ROM 是固化在处理器内部的一段启动代码,它负责系统的初步设置和引导过程。首先肯定是初始化时钟,具体如下图所示。

BT_FREQ 模式为 0,可以看到,boot ROM 会将 I.MX6U 的内核时钟设置为396MHz,也就是主频为 396Mhz。System PLL=528Mhz,USB PLL=480MHz,AHB=132MHz,IPG=66MHz。关于 I.MX6U 的系统时钟,我们后面会详细讲解。内部 boot ROM 为了加快执行速度会打开 MMU 和 Cache,下载镜像的时候 L1 ICache 会打开,验证镜像的时候 L1 DCache、L2 Cache 和 MMU 都会打开。一旦镜像验证完成,boot ROM就会关闭 L1 DCache、L2 Cache 和 MMU。

内核时钟(CPU Clock)为 396 MHz:这意味着处理器的主频设置为396 MHz,这是处理器执行指令的速度。

System PLL(系统相位锁定环)为 528 MHz:PLLs(Phase-Locked Loops)是一种电子电路,用于产生一个精确的时钟信号。在这里,528 MHz 是一个重要的时钟源,用于生成其他系统时钟。 USB PLL为 480 MHz:这个时钟专门为 USB 接口提供时钟信号,确保USB通信的稳定性和性能。

AHB(高性能总线)为 132 MHz:AHB是用于高速访问核心模块如RAM和ROM的总线。132 MHz 的速度是为了平衡性能和功耗。

IPG(外设总线)为 66MHz:IPG是连接低速外设的总线,66 MHz 提供了足够的速度来支持这些外设的操作。

MMU 和 Cache 的作用

MMU(内存管理单元):MMU负责虚拟内存和物理内存之间的映射。在系统启动和引导过程中启用MMU可以提高内存访问的效率和安全性。

Cache(缓存):Cache是一种快速存储器,用于减少访问主内存的次数,从而加快数据访问速度。在i.MX6U的启动过程中,Cache被用来加快引导程序的执行速度。

L1 ICache(一级指令缓存):在下载镜像时开启,加快指令的读取速度。

L1 DCache(一级数据缓存)和 L2 Cache(二级缓存):在验证镜像时开启,加快数据的读写速度。

镜像下载与验证

在系统启动过程中,Boot ROM 首先会下载引导镜像到内存中,并开启 L1 ICache 来加速这一过程。一旦下载完成,为了确保引导镜像的完整性和安全性,Boot ROM 会进行镜像验证,这时会开启 L1 DCache、L2 Cache 和 MMU 来加速验证过程。

镜像验证后的操作

一旦镜像验证完成,为了将系统转入一个更安全、更可控的状态,Boot ROM 会关闭 L1 DCache、L2 Cache 和 MMU。这样做的目的是为了在将控制权交给引导加载程序(如U-Boot)之前,清除所有的缓存和状态,确保系统的干净启动。

启动设备

启动设备是指系统上电或重置后第一个被执行的代码所在的存储设备。这个设备包含了启动系统所需的初始程序代码,通常被称为引导加载程序(Bootloader)。引导加载程序是系统启动过程中至关重要的一部分,它负责初始化硬件设备、设置内存、加载操作系统内核等任务,从而使系统进入可操作状态。

当 BOOT_MODE 设置为内部 BOOT 模式以后,可以从以下设备中启动:

①、接到 EIM 接口的 CS0 上的 16 位 NOR Flash。

②、接到 EIM 接口的 CS0 上的 OneNAND Flash。

③、接到 GPMI 接口上的 MLC/SLC NAND Flash,NAND Flash 页大小支持 2KByte、4KByte

和 8KByte,8 位宽。

④、Quad SPI Flash。

⑤、接到 USDHC 接口上的 SD/MMC/eSD/SDXC/eMMC 等设备。

⑥、SPI 接口的 EEPROM。

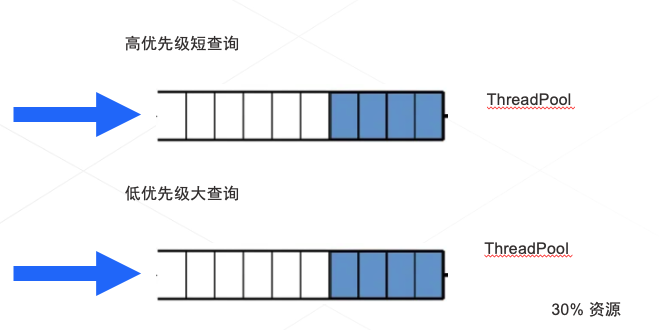

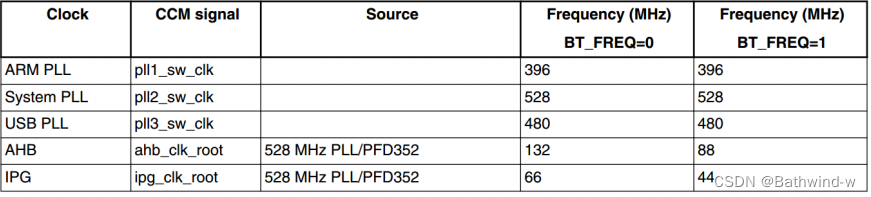

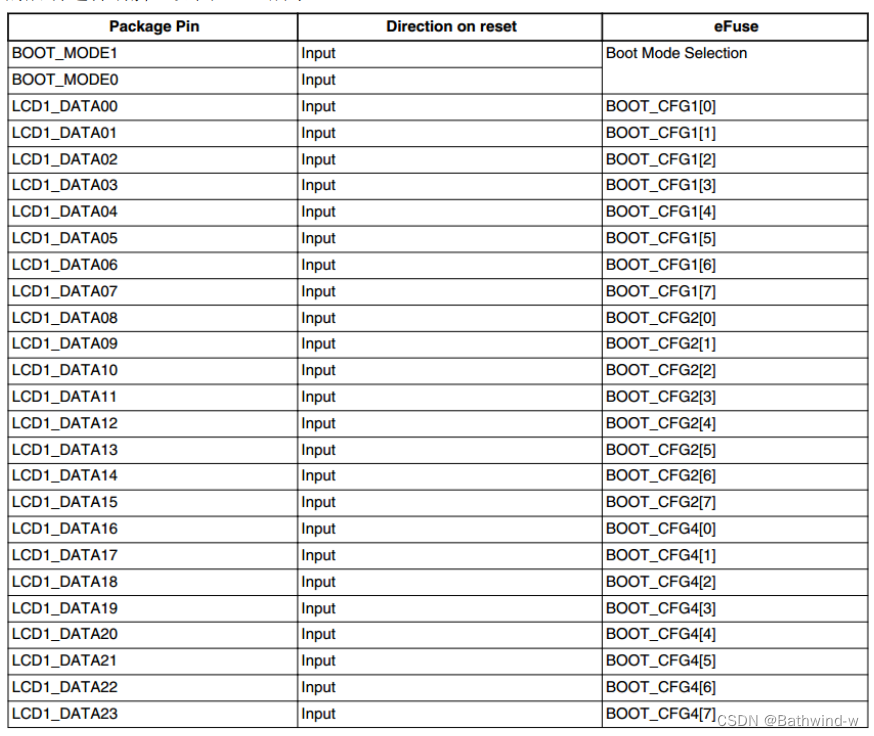

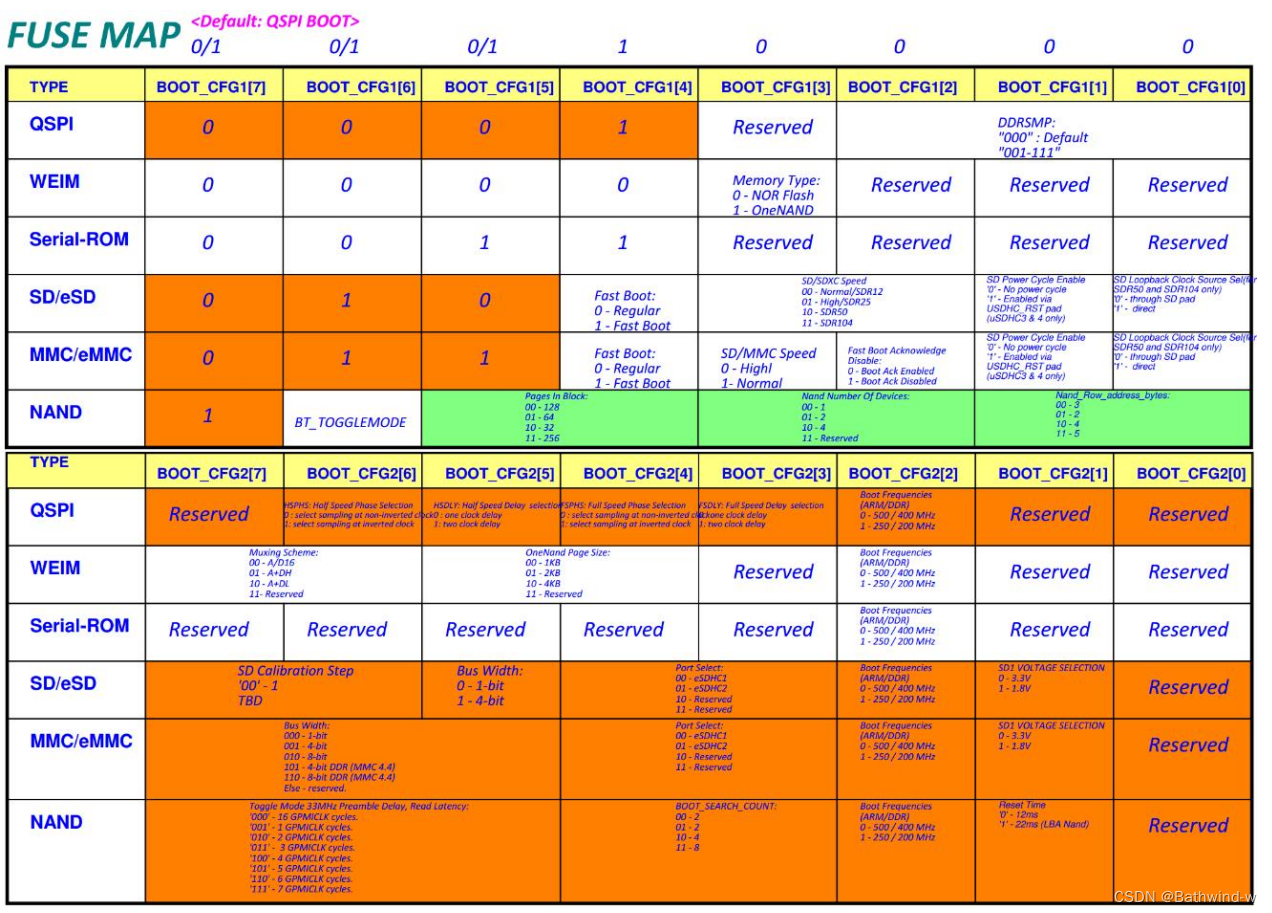

这些启动设备如何选择呢?I.MX6U 同样提供了 eFUSE 和 GPIO 配置两种,eFUSE 就不讲解了。我们重点看如何通过 GPIO 来选择启动设备,因为所有的 I.MX6U 开发板都是通过 GPIO来配置启动设备的。正如启动模式由 BOOT_MODE[1:0]来选择一样,**启动设备是通过BOOT_CFG1[7:0]、BOOT_CFG2[7:0]和 BOOT_CFG4[7:0]这 24 个配置 IO,这 24 个配置 IO 刚好对应着 LCD 的 24 根数据线 LCD_DATA0~LCDDATA23,当启动完成以后这 24 个 IO 就可以作为 LCD 的数据线使用。**这 24 根线和 BOOT_MODE1、BOOT_MODE0 共同组成了 I.MX6U的启动选择引脚。

虽然有 24 个 IO,但是实际需要调整的只有那几个 IO,其它的 IO 全部下拉接地即可,也就是设置为 0。打开 I.MX6U-ALPHA 开发板的核心板原理图,这 24 个 IO 的默认设置如图所示:

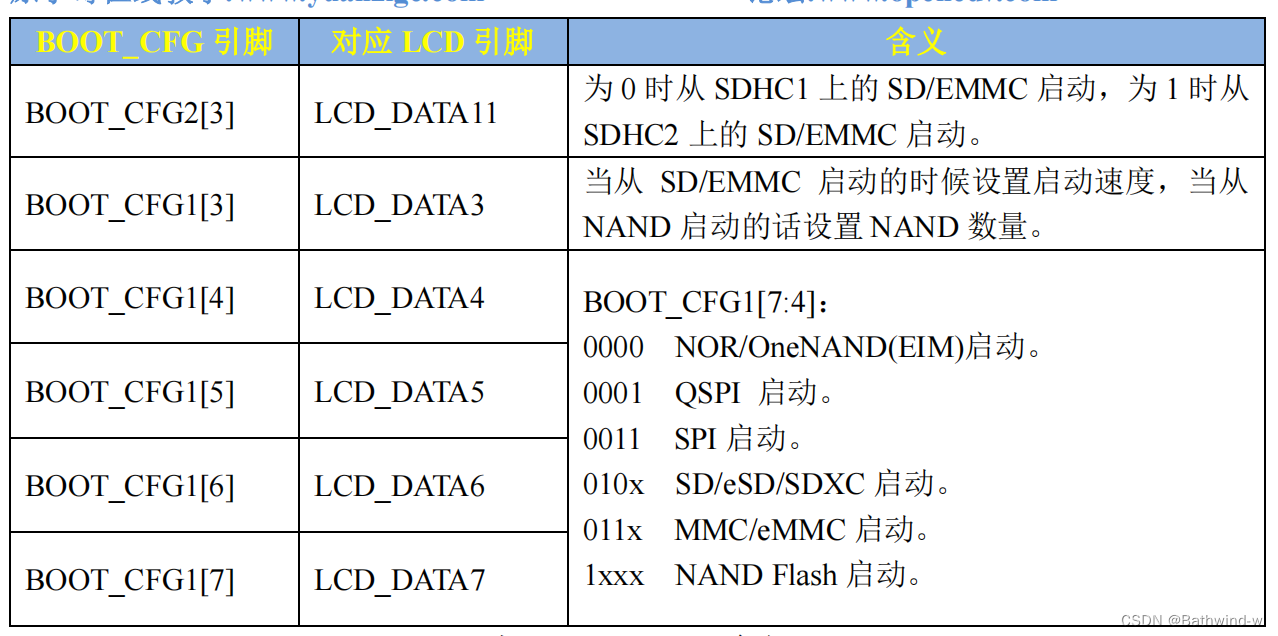

大部分的 IO 都接地了,只有几个 IO 接高,尤其是 BOOT_CFG4[7:0]这 8 个 IO 都 10K 电阻下拉接地,所以我们压根就不需要去关注 BOOT_CFG4[7:0]。我们需要重点关注的就只剩下了 BOOT_CFG2[7:0]和 BOOT_CFG1[7:0]这 16 个 IO。这 16 个配置 IO 含义在原理图的左侧已经贴出来了,如图所示:

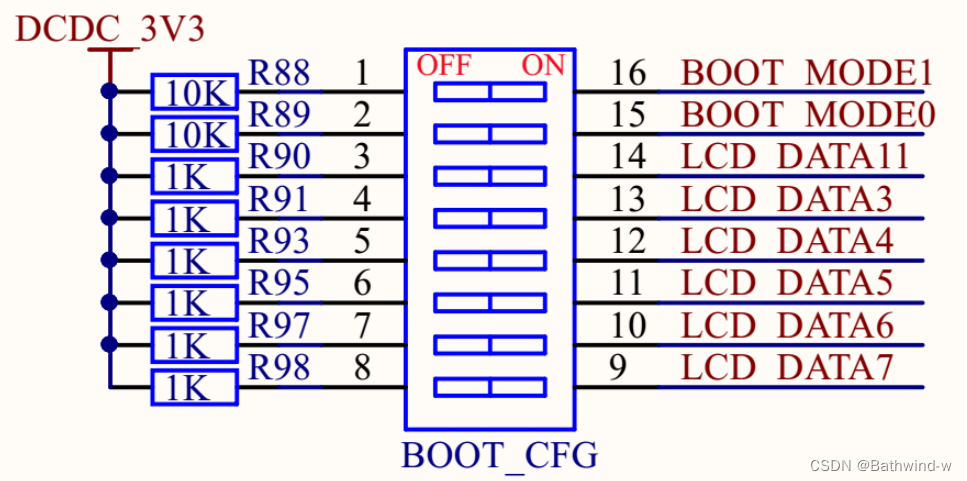

打开 I.MX6U-ALPHA 开发板的底板原理图,底板上启动设备选择拨码开关原理图如图所示:

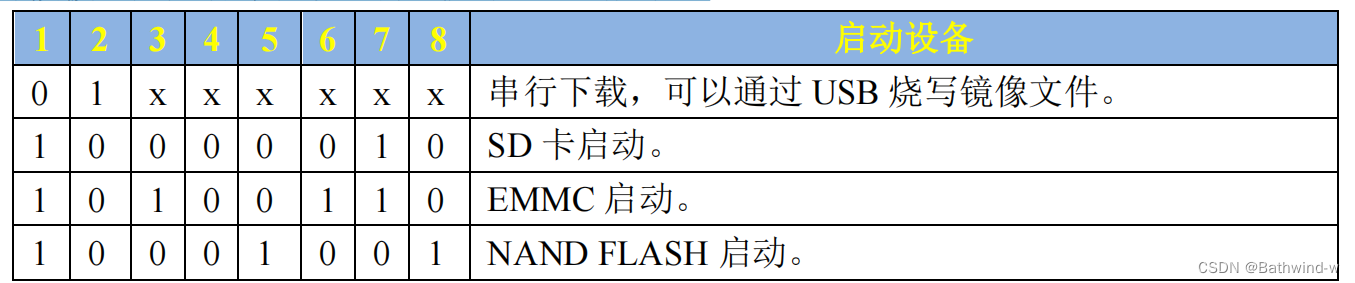

根据图中的 BOOT IO 含义,I.MX6U-ALPHA 开发板从 SD 卡、EMMC、NAND 启动的时候拨码开关各个位设置方式如下图所示:

上节课我们编写完汇编程序要把程序编译后烧写到sd卡,然后从sd卡启动。那么镜像烧写的过程是啥呢。究竟。原子的文档很清楚了介绍了这一块。

镜像烧写

我们设置好 BOOT 以后就能从指定的设备启动了,但是你的设备里面得有代码啊,在第八章中我们使用 imxdownload 这个软件将 led.bin 烧写到了 SD 卡中。imxdownload 会在 led.bin前面添加一些头信息,重新生成一个叫做 load.imx 的文件,最终实际烧写的是 laod.imx。

在嵌入式系统的开发过程中,不同的微处理器或微控制器有着不同的启动和程序加载机制。对于STM32这样的微控制器,通常可以直接将编译生成的.bin文件烧写到内部Flash中,因为STM32的启动加载(Bootloader)设计成可以直接识别和加载裸机二进制文件。然而,对于更复杂的处理器如NXP的i.MX6UL(以下简称i.MX6U),情况就有所不同。i.MX6U等处理器的启动流程设计得更为复杂和灵活,以支持多种启动媒体和复杂的应用场景,比如从SD卡、NAND Flash或者通过网络启动。因此,仅有裸机的.bin文件是不够的,需要在文件前添加特定的头信息,构成一个适合i.MX6U处理器识别和加载的格式。这个最终的可烧写文件,通常包含以下几个部分:

-

启动头信息(Boot Header):这是文件的最开始部分,包含了启动时必需的信息,例如程序的起始地址、加载到内存中的位置、需要加载的数据长度等。对于i.MX6U,这个头信息还可能包含签名或加密信息,用于安全启动。

-

IVT(Image Vector Table):图像向量表,是一个固定格式的表,包含了启动过程中需要的各种地址,如启动入口地址、D-CD(Device Configuration Data)的地址、Boot Data的地址等。IVT使得处理器能够知道从哪里获取必要的信息来加载和执行程序。

-

Boot Data:包含了关于映像的一些基本信息,如映像的大小和加载到内存中的目标地址。这些信息用于引导程序正确地将应用程序加载到内存中。

-

D-CD(Device Configuration Data):这部分数据包含了特定的配置信息,用于初始化处理器的某些外设或接口。这对于确保应用程序能在特定的硬件设置下正常运行是必需的。

-

应用程序代码(Application Code):这是编译生成的

.bin文件,即实际的应用程序代码。它紧随上述头信息和配置数据之后。 -

CSF(Command Sequence File):对于需要安全启动的场景,CSF包含了用于验证程序完整性和真实性的命令和数据,如数字签名验证。

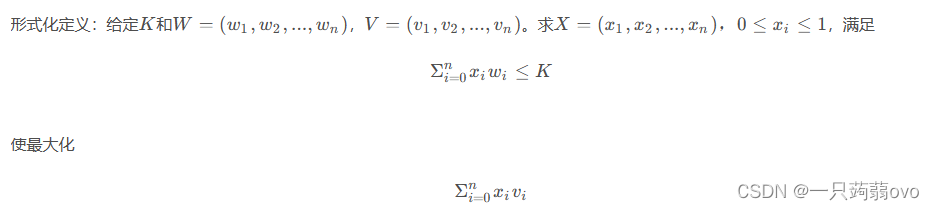

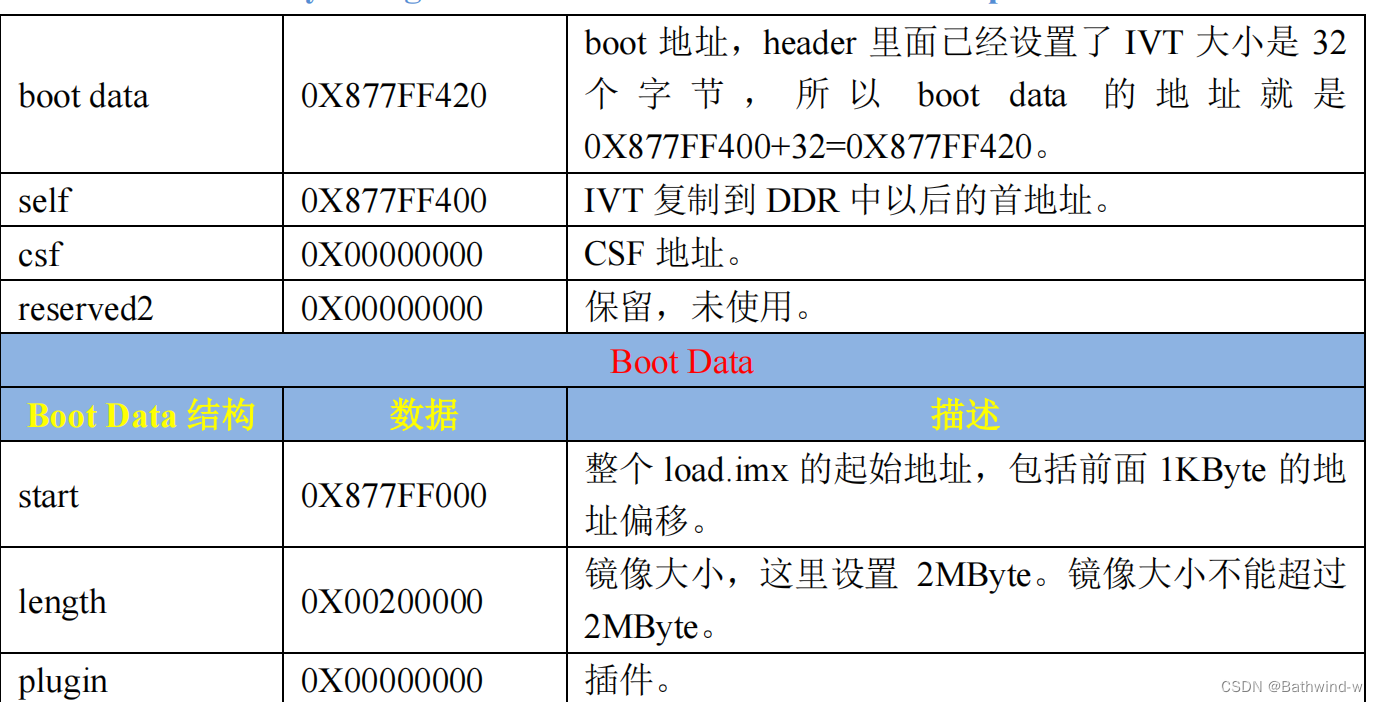

构建这样一个文件通常需要使用特定的工具或脚本,这些工具会按照i.MX6U的要求将上述各个部分组合成一个单一的可烧写文件。可以看出最终烧写到 I.MX6U 中的程序其组成为:IVT+Boot data+DCD+.bin。所以第八章中的 imxdownload 所生成的 load.imx 就是在 led.bin 前面加上 IVT+Boot data+DCD。内部 BootROM 会将 load.imx 拷贝到 DDR 中,用户代码是要一定要从 0X87800000 这个地方开始的,因为链接地址为 0X87800000,load.imx 在用户代码前面又有 3KByte 的 IVT+Boot Data+DCD 数 据,下面会讲为什么是 3KByte,因此 load.imx 在 DDR 中的起始地址就是 0X87800000-3072=0X877FF400。

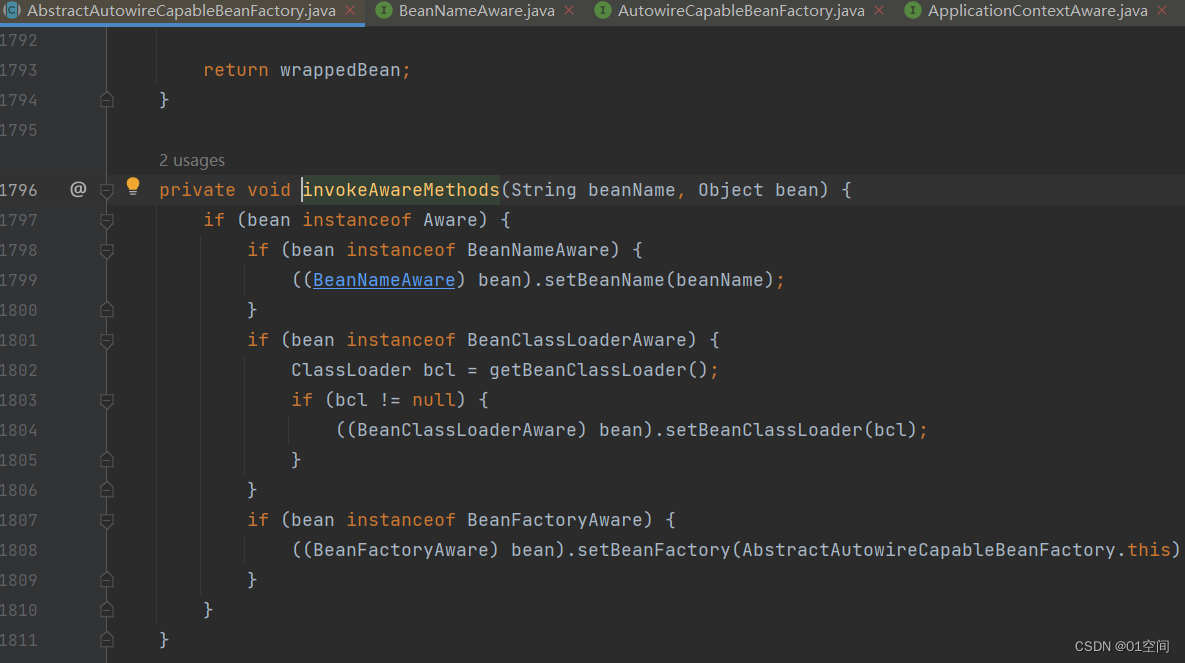

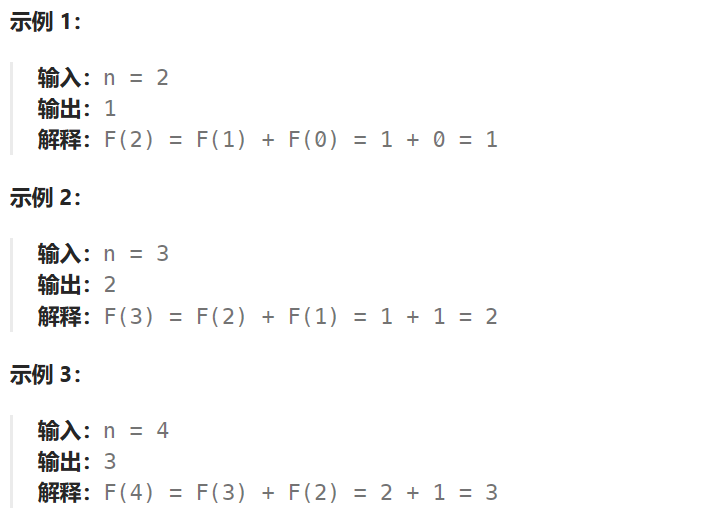

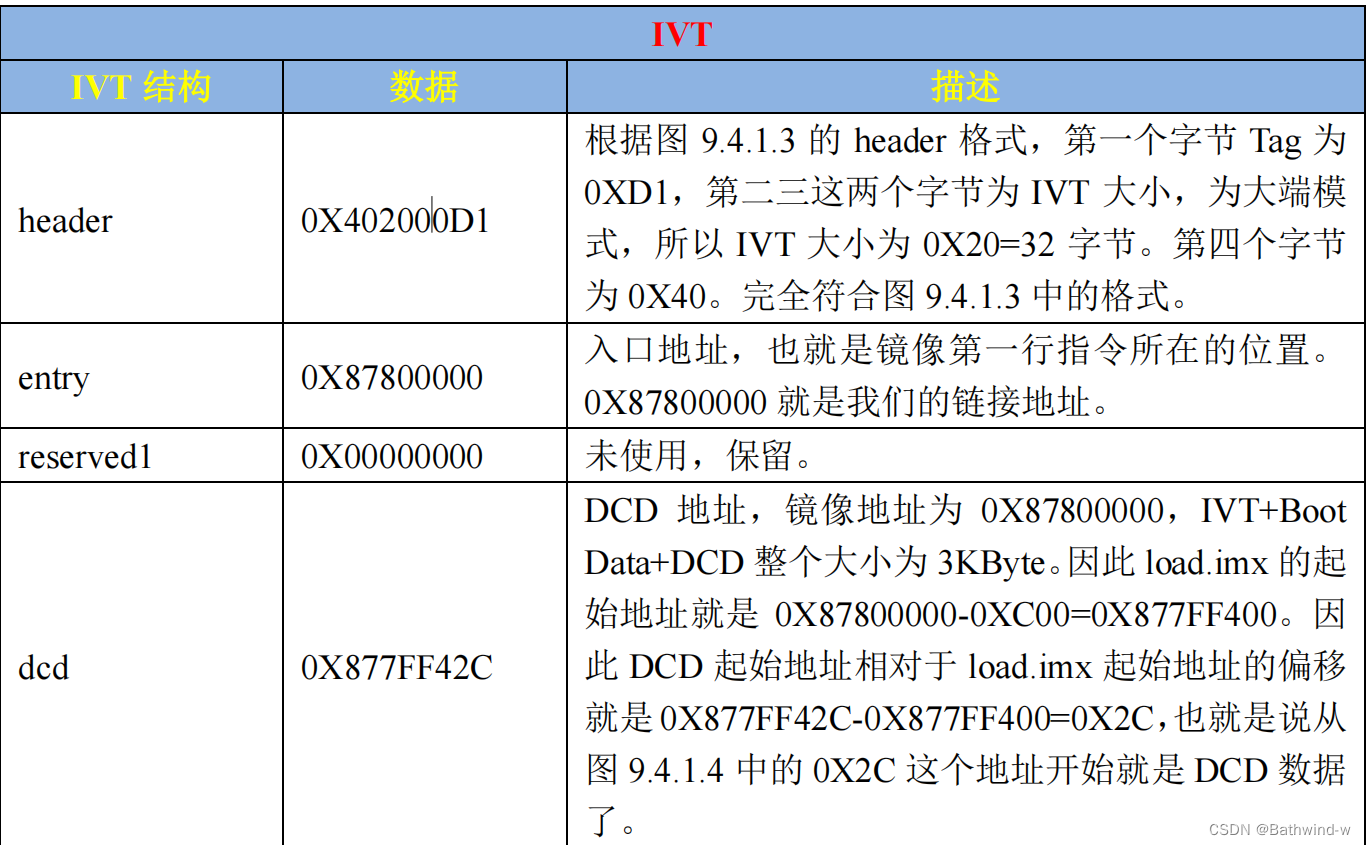

接下来具体分析下IVT 和 Boot Data 数据:

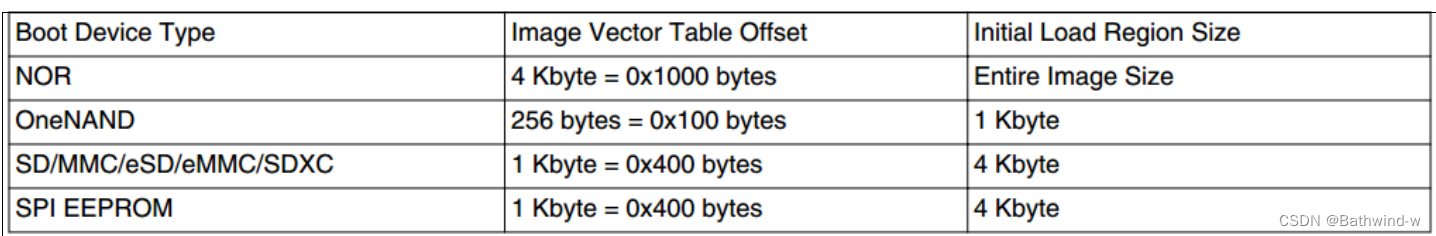

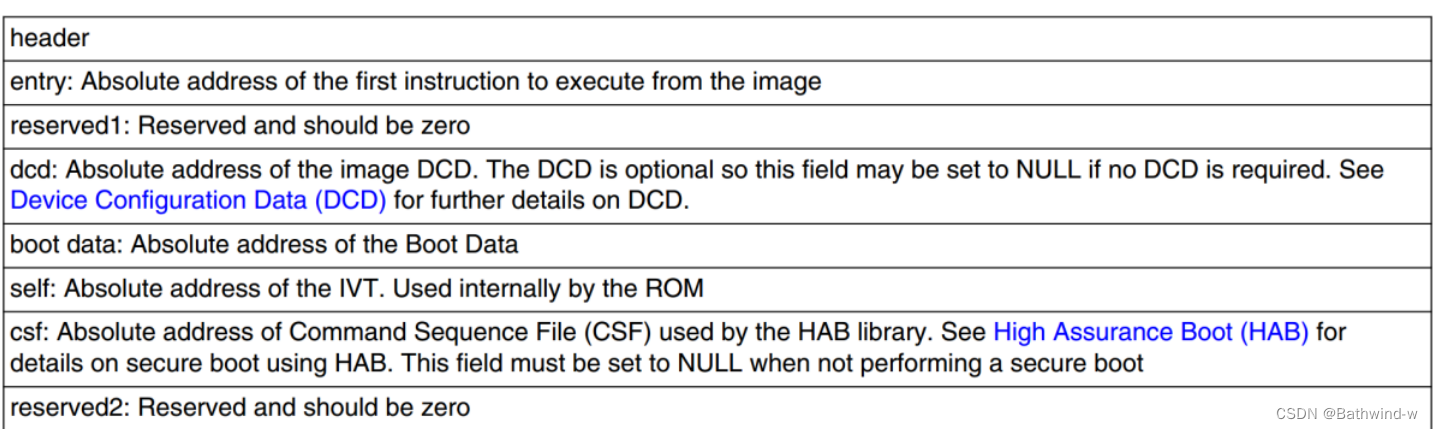

load.imx 最前面的就是 IVT 和 Boot Data,IVT 包含了镜像程序的入口点、指向 DCD 的指针和一些用作其它用途的指针。内部 Boot ROM 要求 IVT 应该放到指定的位置,不同的启动设备位置不同,而 IVT 在整个 load.imx 的最前面,其整个位置都是相对于存储设备的起始地址的偏移。

以 SD/EMMC 为例,IVT 偏移为 1Kbyte,IVT+Boot data+DCD 的总大小为 4KByte-1KByte=3KByte。为啥这样去计算,这里我的理解是:SD/EMMC模式下IVT偏移地址为1KB,因为偏移是相对于存储地址的偏移量。所以IVT是相当于从1KB的地址的开始的。而原始的Initial Load Region Size为4KB。所以IVT+Boot data+DCD 的总大小为 4KByte-1KByte=3KByte。假如 SD/EMMC 每个扇区为 512 字节,那么 load.imx 应该从第三个扇区开始烧写,前两个扇区要留出来。load.imx 从IVT开始的第 3KByte 开始才是真正的.bin 文件(如果IVT、Boot Data和DCD总共占用了3KB,那么load.imx的程序数据部分(也就是.bin部分)实际上是从这3KB之后开始的)。

下图为IVT中存放的内容:

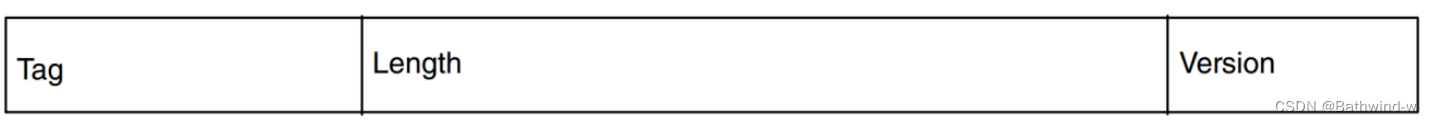

第一个存放的就是 header(头),header 格式如图所示:

Tag 为一个字节长度,固定为 0XD1,Length 是两个字节,保存着 IVT 长度,为大端格式,也就是高字节保存在低内存中。最后的 Version 是一个字节,为 0X40 或者0X41。

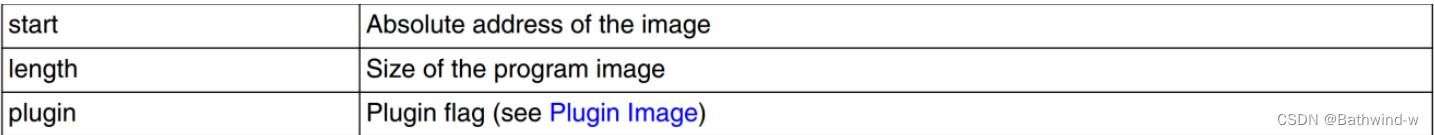

Boot Data 的数据格式如图所示:

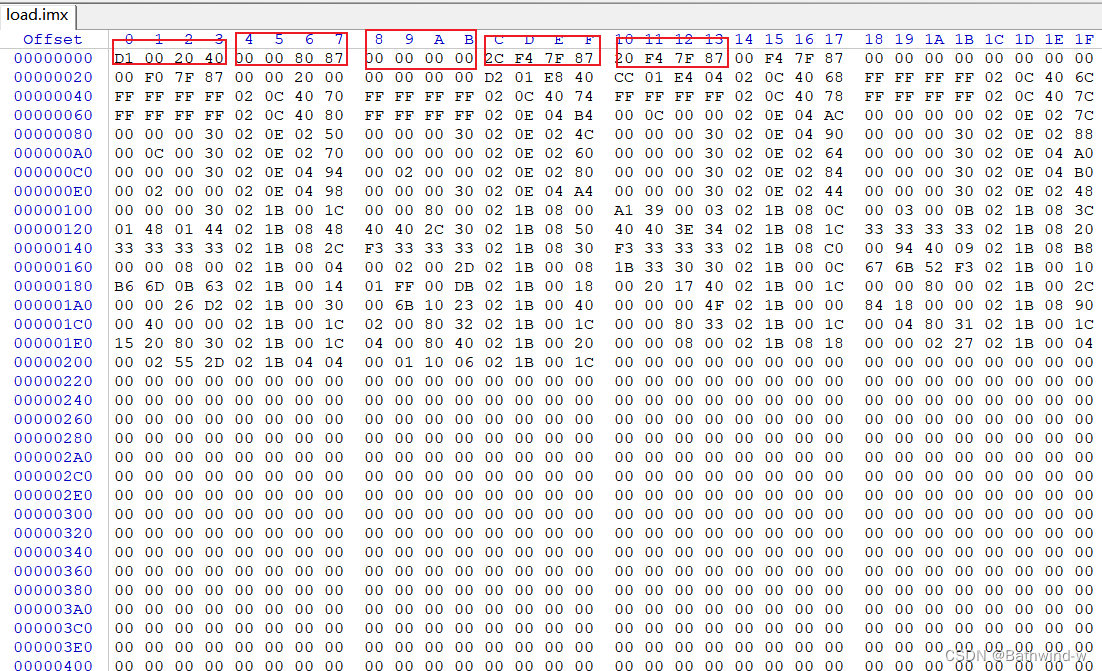

接下来用winhex软件分析Load.imx的具体对应二进制格式数据。具体如下图9.4.1.4所示。

我们将前 44 个字节的数据按照 4 个字节一组组合在一起就是:0X402000D1、0X87800000、0X00000000、0X877FF42C、0X877FF420、0X877FF400、0X00000000、0X00000000、0X877FF000、0X00200000、0X00000000。这 44 个字节的数据就是 IVT 和 Boot Data 数据,按照 IVT 和 Boot Data 所示的格式对应起来如下图所示:

DCD 数据:

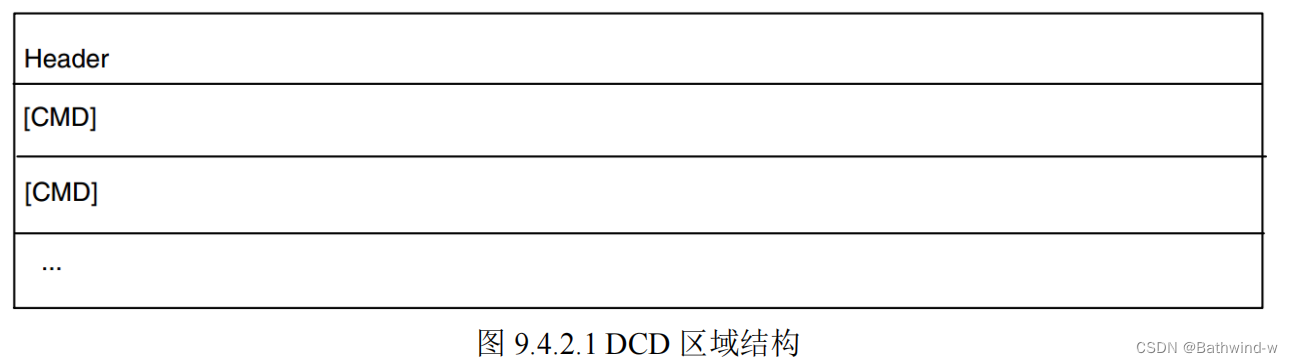

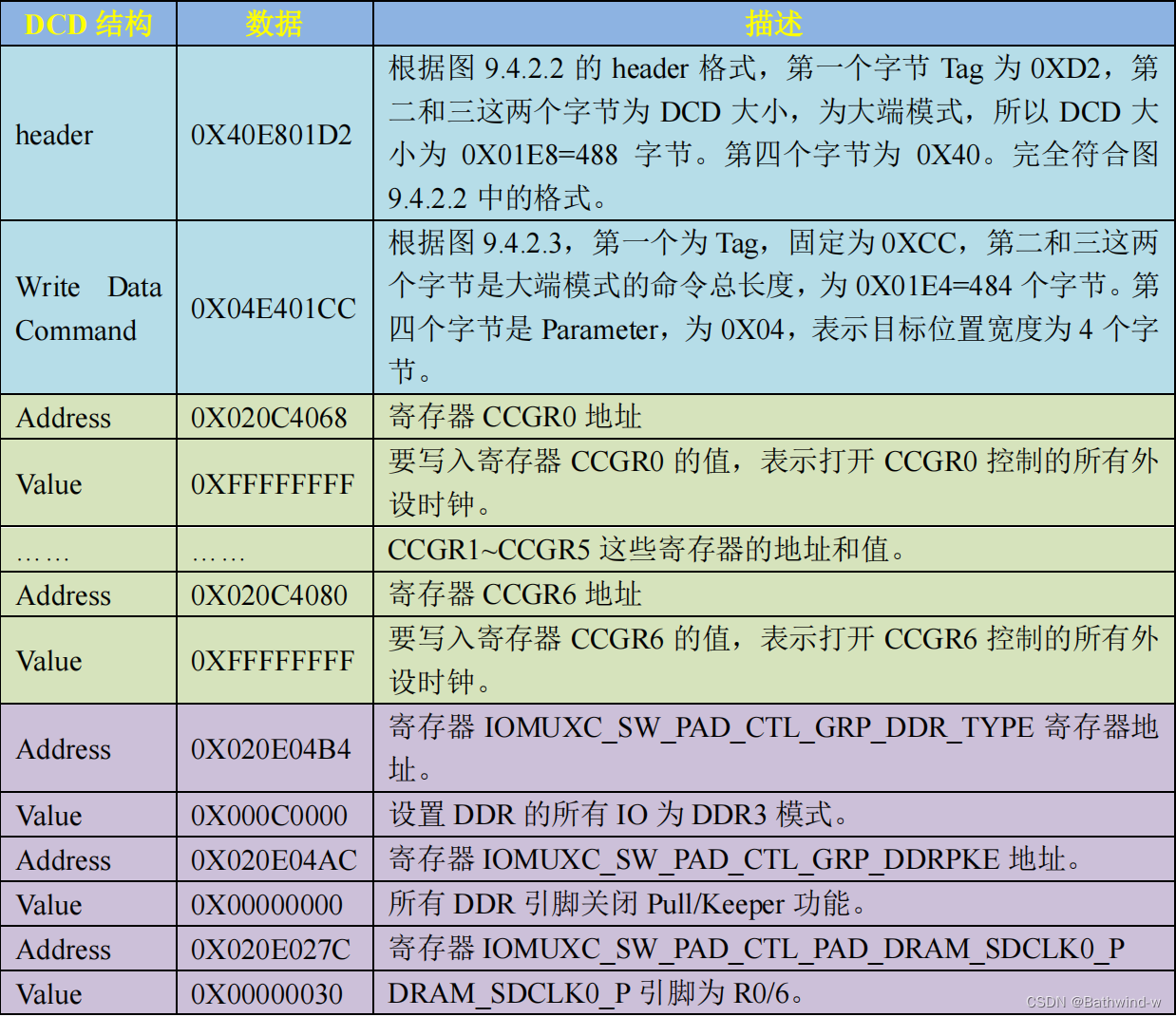

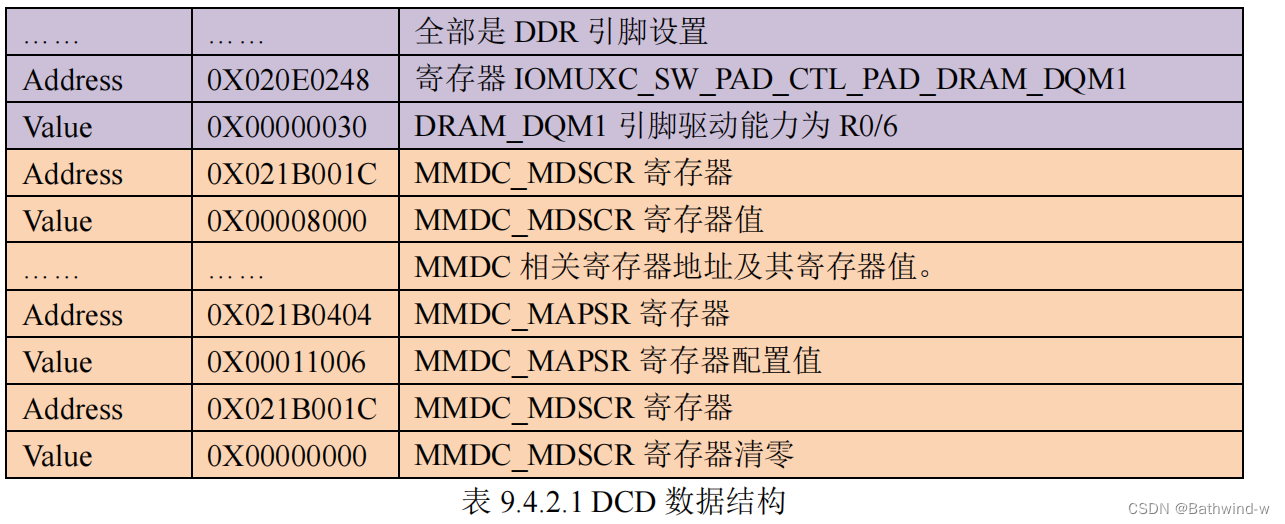

I.MX6U 片内的所有寄存器都会复位为默认值,但是这些默认值往往不是我们想要的值,而且有些外设我们必须在使用之前初始化它。为此 I.MX6U 提出了一个 DCD(Device Config Data)的概念,和 IVT、Boot Data 一样,DCD 也是添加到 load.imx 里面的,紧跟在 IVT和 Boot Data 后面,IVT 里面也指定了 DCD 的位置。DCD 其实就是 I.MX6U 寄存器地址和对应的配置信息集合,Boot ROM 会使用这些寄存器地址和配置集合来初始化相应的寄存器,比如开启某些外设的时钟、初始化 DDR 等等。DCD 区域不能超过 1768Byte,DCD 区域结构如图:

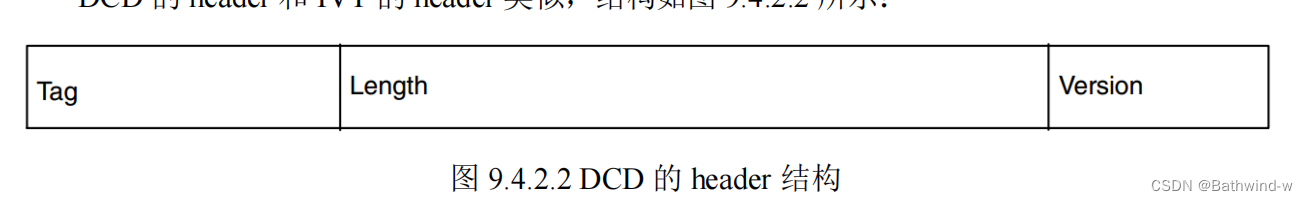

DCD 的 header 和 IVT 的 header 类似,结构如图所示:

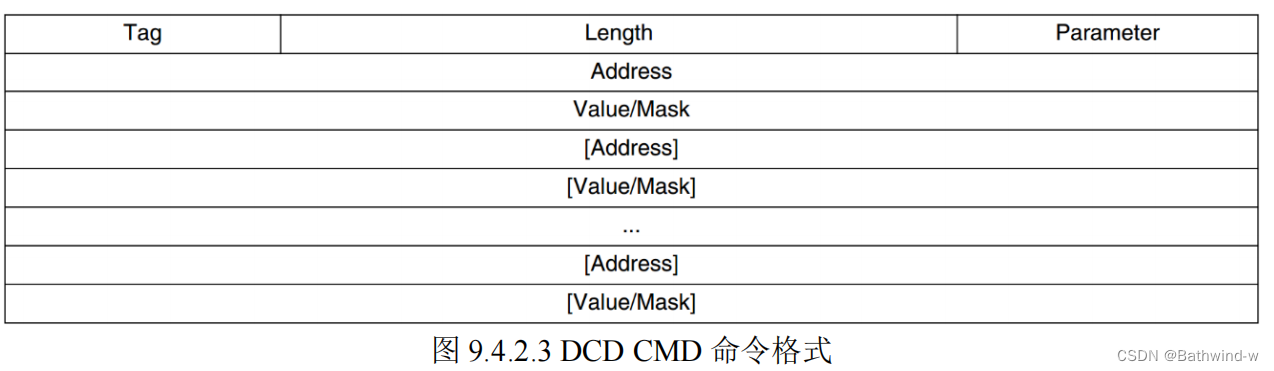

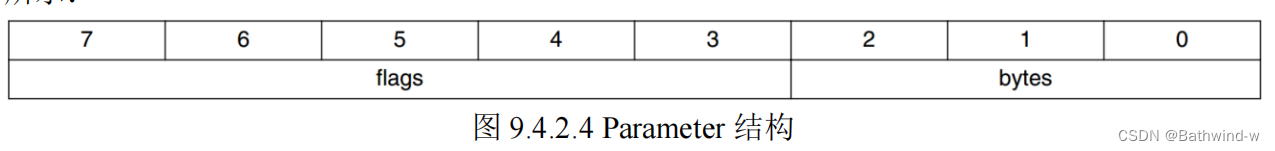

图中 Tag 为一个字节,固定为 0XCC。Length 是两个字节,包含写入的命令数据长度,包含 header,同样是大端模式。Parameter 为一个字节,这个字节的每个位含义如下图所示:Address 和 Vlalue/Mask 就是要初始化的寄存器地址和相应的寄存器值,注意采用的是大端模式!

bytes 表示是目标位置宽度,单位为 byte,可以选择 1、2、和 4 字节。flags是命令控制标志位。

DCD

数据是从图 0X2C 地址开始的。根据我们分析的 DCD 结构可以得到 load.imx 的 DCD数据如图所示

从表 9.4.2.1 中可以看出,DCD 里面的初始化配置主要包括三方面:

①、设置 CCGR0~CCGR6 这 7 个外设时钟使能寄存器,默认打开所有的外设时钟。

②、配置 DDR3 所用的所有 IO。

③、配置 MMDC 控制器,初始化 DDR3。