目录

- 1 概述

- 2 IP examples功能

- 3 IP 使用例程

- 3.1 IP设置

- 3.2 fft_demo端口

- 3.3 例程框图

- 3.4 仿真结果

- 3.5 仿真验证得出的结论

- 4 注意事项

- 5例程位置

1 概述

本文用于讲解xilinx IP 的FFT ip examples的功能说明,方便使用者快速上手。

参考文档:《PG109》

2 IP examples功能

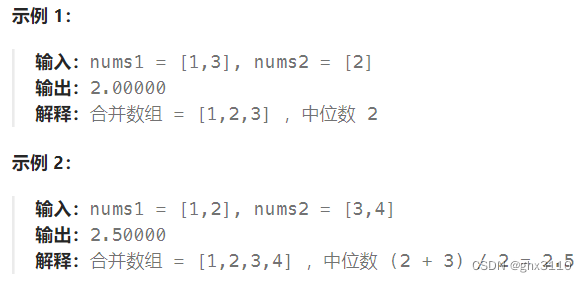

本examples 是风中月隐编写的针对xilinx FFT IP的使用demo,通过仿真验证了以下功能:

1) 可动态配置FFT得点数;

2) 可出算出输入信号得频率;

3) 可计算出FFT得幅度峰值;

4) 验证了输入I/Q顺序对FFT输出结果得影响;

5) 验证了动态配置FFT点数得IP设置限制;

6) 验证了是否可连续输入数据;

7) 可看到FFT输出每个点的频率;

8) 推算了FFT IP输出结果与dB值的关系;

例程的平台:

1) 仿真硬件平台:XC7Z030-ffg676-2

2) FPGA开发平台:vivado2018.2

3 IP 使用例程

3.1 IP设置

3.2 fft_demo端口

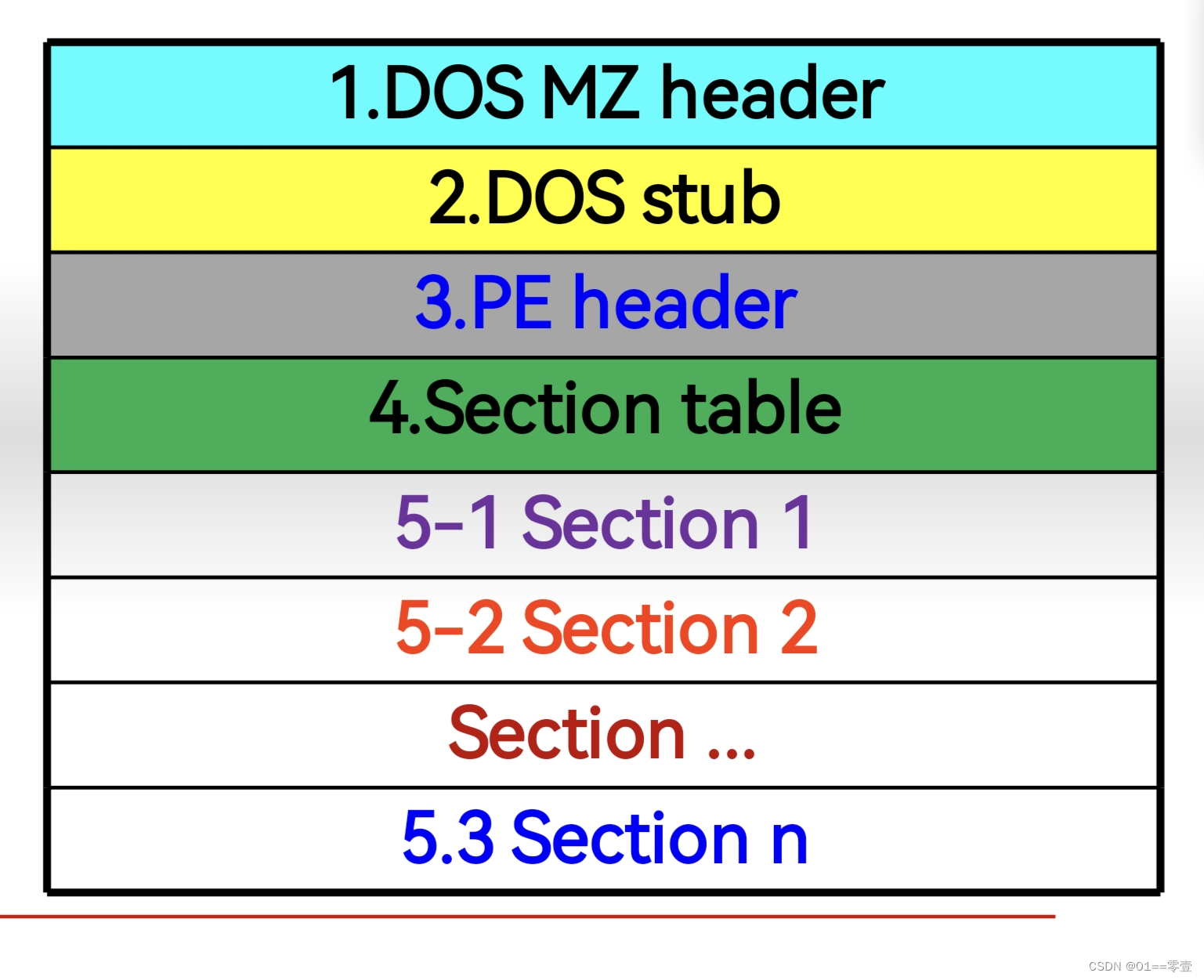

3.3 例程框图

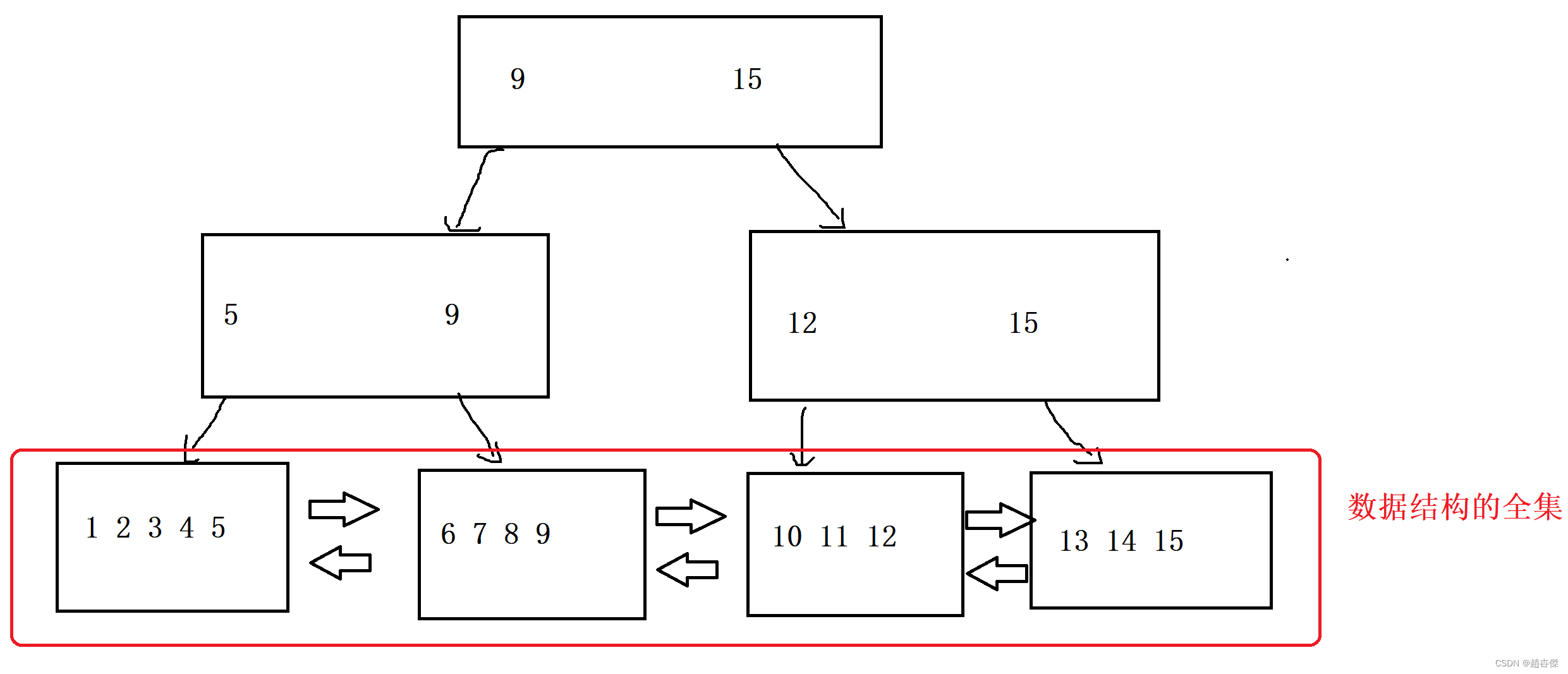

以上是测试得一个整体框图,其中得模块与信号含义如下:

1) DDS IP 产生cos/sin正弦信号,即模拟外部ADC采集得I/Q信号;

2) Tlast_cfg为信号根据FFT得采样点数产生tlast信号,匹配FFT IP得信号输入;

3) FFT IP 为FFT得具体计算,实部/虚部输入与输出对应;

4) 结果处理为:

a) DOUT= DOUT_RE^2 +DOUT_IM^2;

b) DOUT_MAX为DOUT得最大点得值,也就是输入信号得幅度;

c) DOUT_FRE为最大点得频率,也就是输入信号得频率;

3.4 仿真结果

目前测试得结果截图都是基于DDS产生得1MHZ信号;以下只说FFT得情况:

1) 输入FFT得din一段有一段无得情况,可以运算,结果如下:

a) 可看出FFT得点数(fft_transform_length)为1024;

b) FFT_OUT有一个最大值035b7xxx,最后fft_out_max也是这个值;

c) FFT_OUT最大值时fft_fre为976560(单位HZ),最后fft_out_fre也是这个值;

2) 输入FFT得din一直有得情况,可以运算,结果如下:

a) 可看出FFT IP输出得信号s_axis_data_tready一直为高;

b) 可看出FFT得点数(fft_transform_length)为1024;

c) FFT_OUT有一个最大值035b7xxx,最后fft_out_max也是这个值,但这个值得尾部数据不一定一致;

d) FFT_OUT最大值时fft_fre为976560(单位HZ),最后fft_out_fre也是这个值;

3) 输入FFT得I/Q与RE/IM不对应(交换)情况,可以运算,结果如下:

a) 可看出FFT得点数(fft_transform_length)为1024;

b) FFT_OUT有一个最大值035b7xxx,即fft_out_max得高位大小无变化;

c) FFT_OUT最大值时fft_fre为99023184(单位HZ),fft_fre_n为-976816(单位HZ);

4) 输入FFT得RE=有效信号,IM=0情况,可以运算,结果如下:

a) 可看出FFT得点数(fft_transform_length)为1024;

b) FFT_OUT有两个高点,且以中点FS/2对称;

c) FFT_OUT最大值出现在第二个高点(简称fS的后半区);

5) 输入FFT得RE=0,IM=有效信号情况,可以运算,结果如下:

a) 可看出FFT得点数(fft_transform_length)为1024;

b) FFT_OUT有两个高点,且以中点FS/2对称;

c) FFT_OUT最大值出现在第二个高点(简称fS的后半区);

6) 输入FFT得RE/IM都有效,但配置的FFT点数(fft_transform_length=16384)大于IP中设置的FFT点数据(8192)的情况,可以运算但结果不对,结果如下:

a) 可看出设置FFT得点数(fft_transform_length)为16384,一次输入的数据点数也是16384;

b) FFT运算结果是分两个8192点输出的(因为有两次fft_fre_tlast拉高);

c) FFT_OUT有一个高点,在FS的前半区,且最大的值在第一次8192输出的最大值比第二次大;

d) FFT_OUT最大值处计算的FFT_FRE不对;

3.5 仿真验证得出的结论

1) FFT可以连续不断运算,即FFT的输入根据点数拉高tlast即可一直流水线输入输出;

2) 当FFT输入的信号为I/Q时,必须跟RE/IM对应上,否则输出的频率会不对,会以中心点(FS/2)对称;

3) 当输入只有一路实信号(非I/Q信号),给到RE或者IM都可以,差别不大,出现最高点的位置和大小都基本一样;

4) FFT的输入点数可以重新配置,但是不能超过IP界面设置的最大值,超过最大值会按IP设置的最大值分组出数据,且值可能不对;

4 注意事项

1) 一定要注意I/Q信号与FFT的RE/IM对应关系;

2) 输出的频率值是根据采样频率FS以及FFT点数N,换算出的,当采样频率变化时需要修改代码中FS的值;

3) FFT IP输出每个点的频率与采样频率FS以及FFT点数N的关系如下:

a) FFT的点数将采样率FS均分为了N等分,即一个点的分辨率为FS/N;

b) 而每个点number(0~(N-1))的频率即为number*(FS/N);

4) IP中设置的FFT的点数一般是根据项目需要设置最大值(不同的值消耗的FPGA资源差距很大);

5) FFT IP输出值与dB的换算关系为:当FFT的输出值为DOUT=DOUT_RE2+DOUT_IM2时,要换算成dB时还需要额外计算:10log10(DOUT);也等价于20log10(sqrt(DOUT));

6) 此外这个值假如要与实际ADC输入信号功率对等的话,还需要人工标定(偏差相同的值);

7) IP中的fwd_inv一定要设置为1才是FFT,否则设置0为IFFT;

8) IP中的nfft值与FFT的点数对应关系如下(可以看出本IP最大计算点数为65536):

5例程位置

xilinx FFT IP核使用例程

![[pdf,epub]《软件方法》2024版电子书共290页(202405更新)](https://img-blog.csdnimg.cn/img_convert/047c7d61f74f8d134e49076132efe389.png)