爱德万测试(Advantest)的V93000系列测试系统是一个高度模块化和可扩展的平台,专为复杂和高性能的半导体器件测试而设计,包括系统级芯片(SoC)、存储器、射频(RF)和混合信号器件等。在Advantest 93000(通常被称为V93000或V93K)测试机中,CLOCK DOMAIN的概念主要与多通道测试中的时钟管理和同步相关。以下是对CLOCK DOMAIN在Advantest 93000测试机中的详细解释:

-

CLOCK DOMAIN的基本概念:

- CLOCK DOMAIN是指由特定时钟信号驱动的硬件组件或测试通道的集合。在V93000测试机中,这些通道可能需要进行同步测试,以确保测试的准确性和一致性。

-

CLOCK DOMAIN的类型:

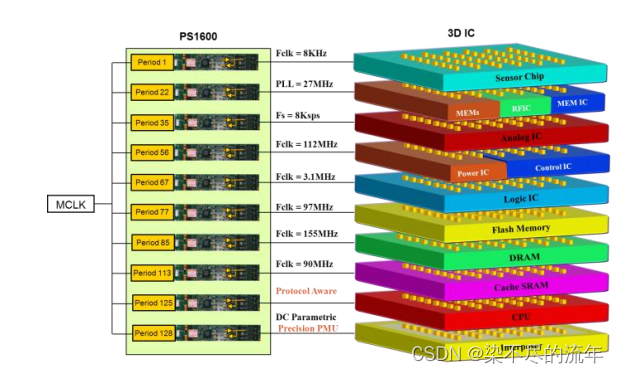

- SINGLE CLOCK DOMAIN:在这种模式下,模拟模块与通道模块共享主时钟MCLK(Master Clock)。此时,模拟采样频率(FS)受到时钟频率除以某个因子(N)的限制。

- MULTIPLE CLOCK DOMAIN:在此模式下,不同的测试通道或模块可以使用不同的时钟源。这允许更灵活的时钟设置和更高的采样频率。

-

时钟源和时钟板:

- V93000测试机中的时钟源通常由一个或多个时钟板提供。每个时钟板可以产生多个独立的MCLK线,分配到不同的测试卡槽上。

- 时钟板由软件控制,可以为不同的测试需求提供不同类型的时钟源。时钟板的作用包括频率发生、控制功能码、时钟的路由和信号分配、参考信号、继电器控制和电源线路等。

-

时钟管理和同步:

- 在进行多通道测试时,CLOCK DOMAIN的管理和同步变得尤为重要。测试人员需要确保所有相关的通道或模块都使用正确的时钟源,并在需要时进行精确的同步。

- Advantest 93000测试机提供了强大的时钟管理和同步功能,以确保测试的准确性和一致性。这些功能可能包括时钟分配、时钟相位调整、时钟同步控制等。

-

实际应用:

- 在进行SSD主控芯片的高温测试等复杂测试中,CLOCK DOMAIN的管理和同步尤为重要。测试人员需要根据测试需求配置适当的CLOCK DOMAIN,并确保所有相关的通道或模块都使用正确的时钟源和同步设置。

-

注意事项:

- 在配置CLOCK DOMAIN时,测试人员需要仔细考虑测试需求和硬件限制,以避免时钟冲突或同步问题。

- 如果在测试过程中出现时钟相关的问题,测试人员需要检查CLOCK DOMAIN的配置和同步设置,并进行相应的调整。

7.V93000测试机中时钟域特性的详细说明:

1)时钟域灵活性:V93000平台支持clock-domain-per-pin技术,这意味着每个测试引脚都可以独立配置其时钟信号。这项功能使得测试系统能够模拟芯片内部不同工作频率的时钟域,对于验证跨时钟域信号传输的正确性至关重要。

2)精确时钟控制:系统提供了精细的时钟控制能力,允许用户定义、生成和分配不同的时钟信号到各个测试引脚,包括时钟频率、相位关系、占空比调整等,这对于测试含有异步或准同步时钟域设计的器件尤为关键。

3)跨时钟域测试能力:鉴于多时钟域设计中常见的问题(如亚稳态、时序违例等),V93000通过其先进的测试算法和硬件能力,可以执行复杂的跨时钟域测试向量,以验证数据传输的完整性和时序合规性。

4)Protocol Engine-per-Pin:结合时钟域功能,每引脚的协议引擎可以针对不同接口协议进行精确测试,确保在多时钟域环境中协议层面上的正确交互。

5)SmartLoop与PRBS-per-pin:这些特性进一步增强了时钟域测试的效率和精度,允许对单个引脚进行循环回送测试或伪随机二进制序列(PRBS)测试,这对于验证时钟域边界上的信号质量和传输错误非常有用。

7)动态配置与测试优化:V93000测试机支持在测试过程中动态更改时钟配置,这使得测试工程师能更灵活地应对不同测试场景,优化测试覆盖率,同时减少测试时间和成本。

![Python期末模拟题库[python123题库]](https://img-blog.csdnimg.cn/img_convert/f2f03c29a396519b9b5d79d7fc3154aa.png)