PLL基本原理

锁相环(Phase-Locked Loop, PLL)是一种基本的反馈控制系统,广泛应用于电子通信、信号处理、时钟同步等多个领域。PLL通过反馈机制锁定输入信号的频率和相位,从而实现输出信号与输入信号的同步。其基本工作原理可以概括为以下几个步骤:

1. 参考信号:PLL系统需要一个稳定的参考信号作为输入,这个信号通常是一个稳定的时钟信号。

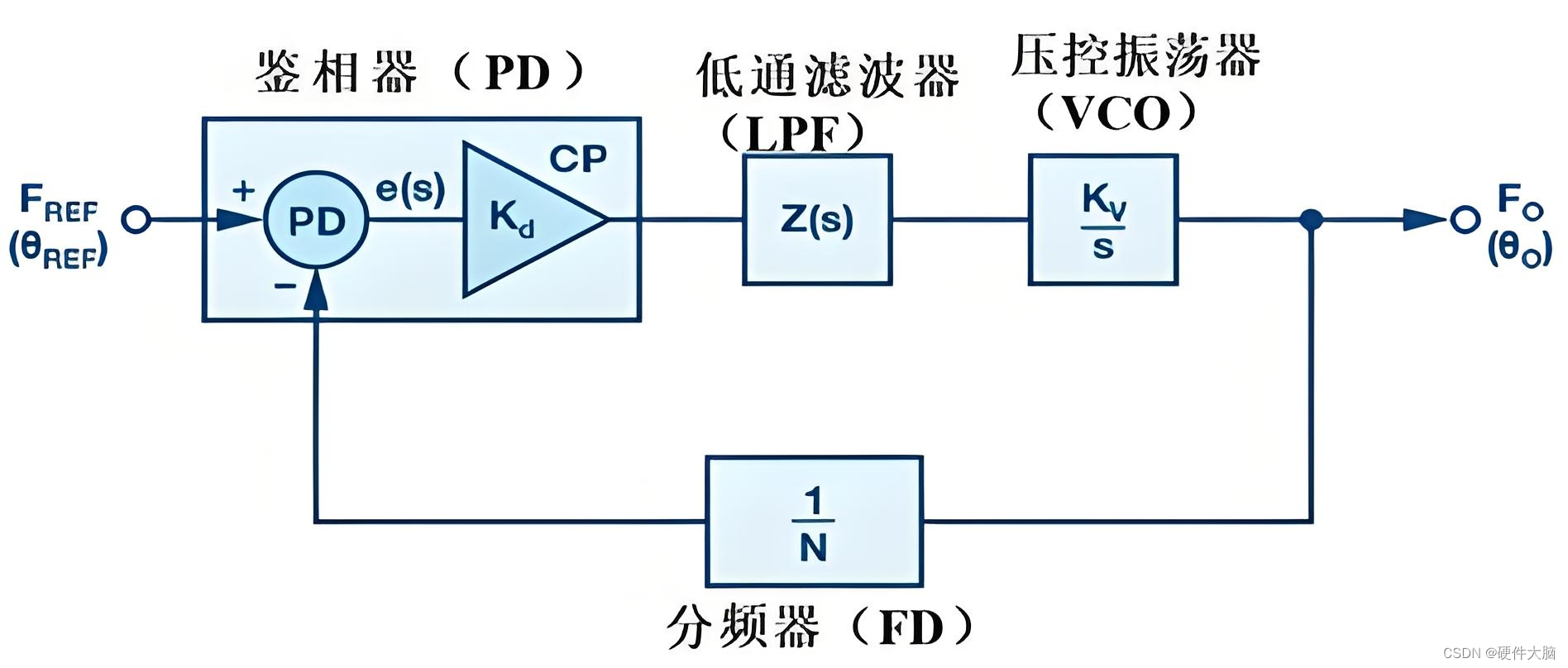

2. 相位比较:将参考信号与反馈信号(通常是VCO的输出)进行相位比较,以获取两个信号之间的相位差值。这一步骤通过鉴相器(Phase Detector, PD)完成,鉴相器将相位差转换为电压信号(误差信号)。

3. 环路滤波:误差信号通过环路滤波器(Loop Filter, LF)进行处理,以滤除高频分量并平滑输出。环路滤波器通常是一个低通滤波器,它输出一个控制电压给VCO。

4. 频率调节:压控振荡器(Voltage-Controlled Oscillator, VCO)根据环路滤波器输出的控制电压调整其输出信号的频率和相位,以减小与参考信号的相位差。

5. 锁定状态:当相位差减小到足够小的范围内时,PLL系统达到锁定状态。在锁定状态下,反馈信号与参考信号具有固定的相位差和频率差,实现信号的同步。

PLL设计

基本组成部分

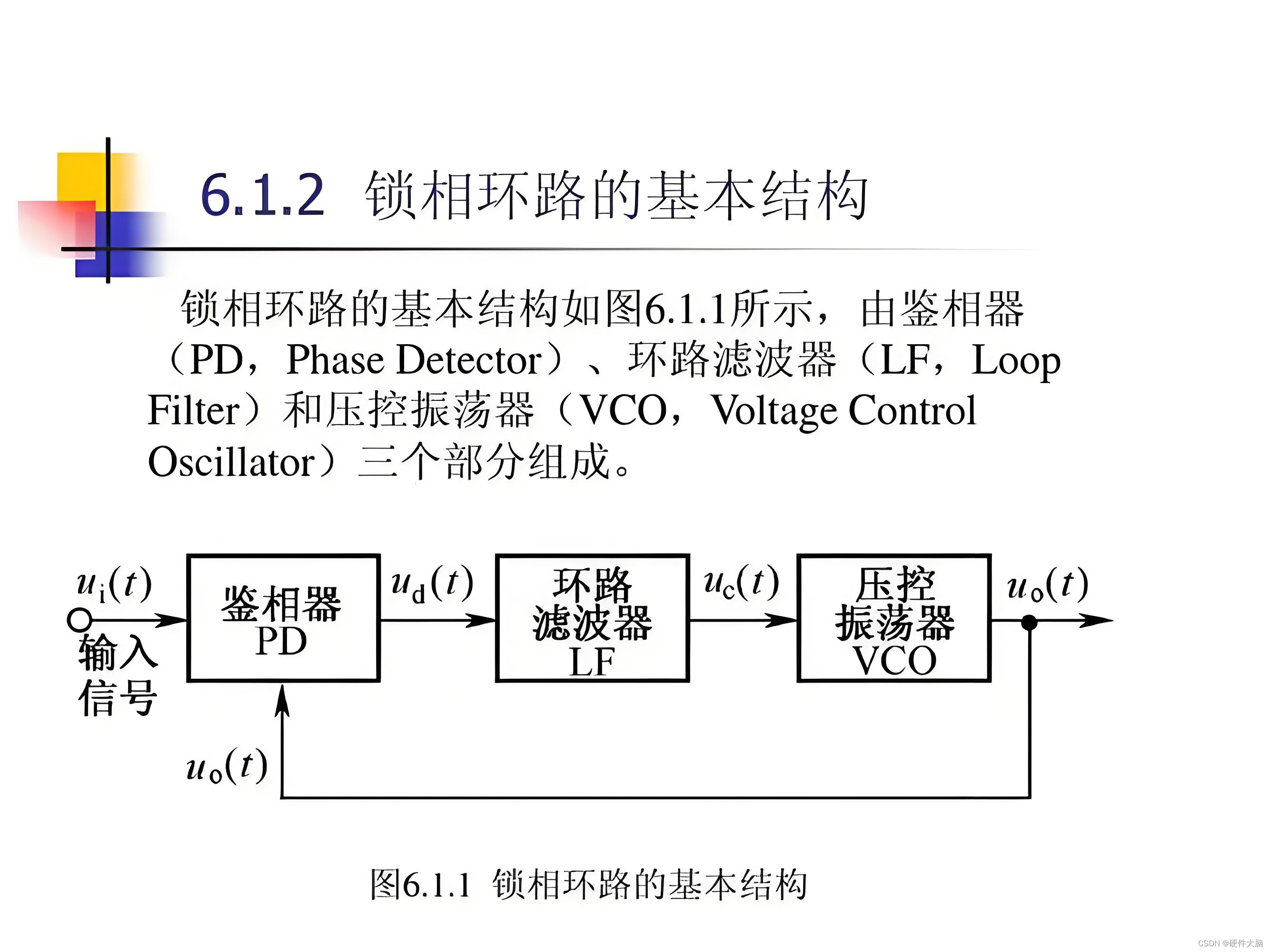

PLL电路主要由鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)三个基本部分组成。

1. 鉴相器(Phase Detector, PD):负责比较输入信号和VCO输出信号的相位差,并将相位差转换为电压信号(误差信号)。

2. 环路滤波器(Loop Filter, LPF):滤除误差信号中的高频分量,平滑输出,形成对VCO的控制电压。它通常是一个简单的RC滤波器或更复杂的滤波器设计。

3. 压控振荡器(Voltage-Controlled Oscillator, VCO):根据环路滤波器输出的控制电压调整其输出信号的频率和相位,以消除与参考信号的相位差。

设计要点

1. 稳定性:PLL系统必须稳定工作,避免振荡或失锁。稳定性与环路滤波器的设计密切相关,需仔细选择滤波器参数。

2. 捕获范围:PLL的捕获范围指其能从多宽的频率范围内捕获并锁定到输入信号。这取决于鉴相器和VCO的性能。

3. 相位噪声:相位噪声是衡量PLL性能的重要指标之一,影响系统的同步精度和信号质量。模拟PLL通常具有较好的相位噪声性能,而数字PLL则可能在高频或宽带应用中受限。

PLL应用

时钟生成和分配

在数字系统中,PLL用于产生和分配稳定的时钟信号。这些时钟信号对于系统的同步和数据传输至关重要。

频率合成

PLL可用于频率合成,即将一个低频信号合成为高频信号。这在通信和射频设备中非常有用,可以实现多频段信号的产生和调制。

调制解调

PLL在调频(FM)和调幅(AM)调制解调器中广泛应用。通过锁定载波信号,PLL能够从调制信号中解调出高质量的音频或数据信息。

信号恢复

PLL能够从噪声污染的信号中恢复出原始信号。这在信号可能短暂中断的场合(如脉冲传输)中特别有用,能够提供稳定的信号输出。

电源管理

在电源管理系统中,PLL用于产生稳定的时钟信号,优化功耗和电源调整。这有助于提高系统的整体效率和稳定性。

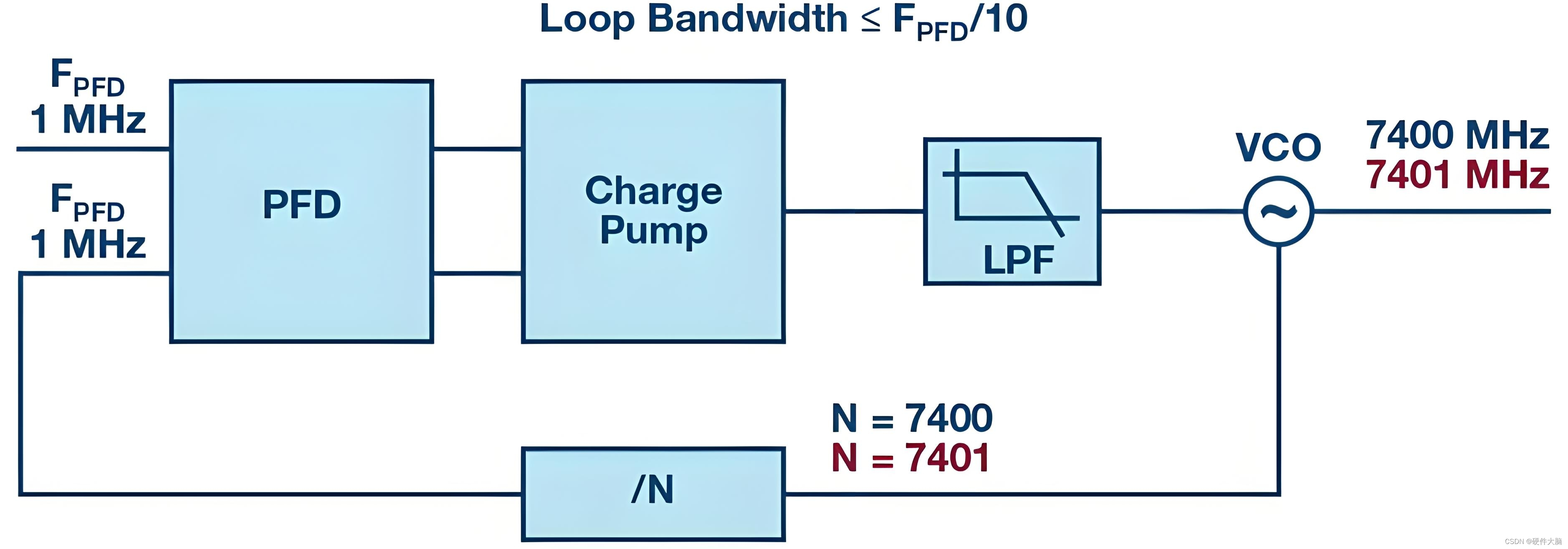

间接频率合成器

间接频率合成器是PLL的一个重要应用,通过调整VCO的输出频率,结合分频器等组件,实现多种频率的合成和输出。

总结

PLL作为一种基本的反馈控制系统,在电子通信、信号处理、时钟同步等多个领域发挥着重要作用。其基本原理是通过反馈机制锁定输入信号的频率和相位,从而实现输出信号与输入信号的同步。在设计PLL时,需要考虑系统的稳定性、捕获范围、相位噪声等关键因素。在应用方面,PLL广泛应用于时钟生成和分配、频率合成、调制解调、信号恢复以及电源管理等多个领域。

![[开端]如何看待“低代码”开发平台的兴起](https://i-blog.csdnimg.cn/direct/b098bfa1e57c4f0e9e14dc0b79310f52.png)

![[开端]JAVA抽象类使用到redis观察着](https://i-blog.csdnimg.cn/direct/51f83f92399b4be58ceda36eda342d92.png)