目录

单选

1.关于亚稳态的描述错误的是(A)

2.一段程序如下,请问在45这个时刻上,A B的值各是多少(B)

3.下列关于综合的说法哪项是不正确的(B)

4.当功能覆盖率(Functional Coverage)达到100%,可以说明:(C)

5.使用相同时钟沿的同步数字电路,以下因素和最高工作频率无关的是:(C)

6.同步电路设计中出现setup time不满足,不可以采用下面哪种措施解决(A)

7.下列说法正确的是(C)

8.Moore状态机和Mealy状态机的差异在(C)是否相关。

9.计算机执行程序时,在(A)的控制下,逐条从内存中取出指令、分析指令、执行指令。

10.相互间相位固定且频率相同的时钟就是同步时钟(A)

11.下面的verilog代码:

产生的时钟频率是:(A)

12.如果该class会被继承,则该class所有定义的function/task都需要加virtual(B)

13.bit、logic、reg都是4态数据类型(B)

14.关于亚稳态,以下说法错误的是(B)

15.对于相同位数输入的变量比较器,大于和小于的面积是一样的 (B)

16.以下说法关于低功耗的说法不正确的是:(D)

17.在System Verilog中,调用$write可以自动地在输出后进行换行。(B)

18.有如下代码

以代码最终实现的约束效果是(A)

19.CPU流水线级数越多,CPU每周期处理的指令数就越多(B)。

20.下列哪项不属于动态功耗? (C)

21.数字电路中用“1”和“0”分别表示两种状态,二者无大小之分(A)

22.芯片的某条时序路径的保持时间不满足,可通过降低工作频率来满足保持时间(B)。

23.异步处理电路中,两级触发器同步方法可以确保第二级寄存器的输出不出现亚稳态。(B)

24.一个十进制数-3,定点位宽为4bit,在Verilog语言中分别用2进制补码表示为(B)

25.systemverilog中类默认的成员属性是(B)

26.格雷码的异步处理可以采用直接打拍的方式,在STA时不需要特殊检查(A)

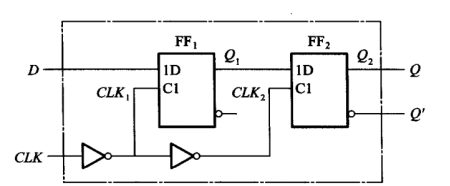

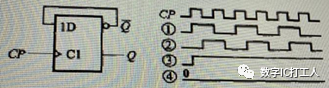

27.电路和波形如图,正确输出的波形是(B)

28.某包处理器的工作时钟为125MHz,在正常工作时,它可以每32个时钟周期处理个64字节的以太包。则该包处理器的处理性能是(A) .

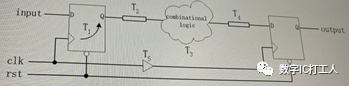

29.在同步电路设计中,逻辑电路的时序模型如下:

那么,为了保证数据正确采样(该路径为multi-cycle路径),下面哪个等式必须正确:(D)

30.为什么数字电路系统中只使用二进制?(C)

多选

1.电路设计中需要关注PPA,分别指(ABC)

2.下述关于覆盖率收集结果的描述正确的是(AD)

3.在设计中,可以被用于进行不同时钟域隔离的memory类型为(AD)

4.芯片的工作条件主要是指(BCD)

5.以下哪几种因素会影响芯片的静态功耗(ACE)

6.下面哪些语句是不可综合的(CDE)

7.在IC设计中,复位设计面临的主要问题包括(ABD)

8.下面关于always语句的使用描述正确的是(ABC)

9.125MHz时钟域的多bit信号A[127:0]需要同步到25MHz时钟域,可能使用的同步方式有(ABD)

10.某个时钟域的建立时间要求是3ns,保持时间要求是3ns,那么如下几个寄存器,存在时序收敛问题的是:ACD

单选

1.关于亚稳态的描述错误的是(A)

A.多用几级寄存器打拍可以消除亚稳态。

B.亚稳态是极不稳定的,理论上来讲处在亚稳态的时间可以无限长。

C.亚稳态稳定到0或者1,是随机的,与输入没有必然的关系。

D.如果数据传输中不满足触发器的建文时间Tsu和保持时间Th,可能产生亚稳态。

亚稳态无法消除,只能尽量避免。

2.一段程序如下,请问在45这个时刻上,A B的值各是多少(B)

fork

begin

A=1;

#20A=0;

#30A=1;

#50A=0;

end

begin

B=1;

#20 B=0;

#30 B=1;

#50 B=0.

end

join

A.0,1

B.0,0

C.1,0

D.1,1

fork_join内部begin_end块,并行执行,45时刻均为0,55均为1

3.下列关于综合的说法哪项是不正确的(B)

A.综合(Synthesis)简单地说就是将HDL代码转化为门级网表的过程

B.综合由Translation和Mapping两个步骤组成

C.Mapping把用GTECH库元件构成的电路映射到某一特定厂家的工艺库上

D.Translation是指把HDL语言描述的电路转化为用GTECH库元件组成的逻辑电路的过程

综合是将RTL转换成门级网表(gate-level netlist)的过程。综合过程分为转换(translation),优化(optimization)、映射(mapping)。

综合工具先通过read命令将RTL代码转化成通用的布尔等式,即GTECH(generic technology)。然后执行compile命令,根据设计者施加的延时,面积等约束,对网表进行优化。最后将RTL网表映射到工艺库上,成为一个门级网表。门级网表输入到布局布线工具,由它产生GDSll文件,验证正确后,交付芯片生产商制造。

综合以时序路径为基础进行优化。DC在对设计做综合时,其过程包括了进行静态时序分析(static timing analysis STA)。DC使用内建的时序分析器把设计分解成多条时间路径,然后根据设计的约束对路径进行优化。如果某条路径的延时大于约束的值,则时序违例。也可以用Prime Time作静态时序分析。PT是独立的时序分析器,主要用于整个芯片门级电路的静态时序分析。

4.当功能覆盖率(Functional Coverage)达到100%,可以说明:(C)

A.DUT的功能点已经100%覆盖。

B.功能覆盖率(FunctionalCoverage)对应的DUT响应是正确的。

C.某些令人关注的情况已经得到测试覆盖。

D.验证工作可以结束

测试点是人为分解得出的,无法保证100%覆盖,也无法保证100%正确,只能说明某些关注的情况得到覆盖,功能点都没有覆盖,验证工作怎么可以结束。即使代码覆盖率和功能覆盖率都达到100%,也要怀有对芯片流片的敬畏之心。

5.使用相同时钟沿的同步数字电路,以下因素和最高工作频率无关的是:(C)

A.触发器之间最长的组合逻辑

B.触发器的建立/保持时间

C.时钟低电平持续时间

D.逻辑块间互连布线长度

对于同步数字电路的最高频率,主要取决于关键路径是否能够收敛,那么就和a,c,d有关系。时钟的低电平持续时间主要影响到时钟信号的有效性。需要做clock pulse width检测,保证该时钟沿能正确地被寄存器采集。如果不满足,则逻辑功能有问题,和最高工作频率无关。

6.同步电路设计中出现setup time不满足,不可以采用下面哪种措施解决(A)

A.增加时钟频率

B.减小信号延迟

C.pipeline

D.降低时钟频率

采用流水线(pipeline)结构,在组合逻辑之间插入触发器,Tcomb减小;

减小信号延迟,Tffpd和Tcomb减小;

降低时钟频率,T增大;

增加时钟频率,T减小,会减小建立时间容限,建立时间将会更不满足;

7.下列说法正确的是(C)

A.设计异步FIFO时采用格雷码的原因主要是为了省功耗

B.对单比特控制信号打两拍后可以完全避免了亚稳态

C.异步处理需要考虑发送和接收时钟之间的频率关系

D.尽量将异步逻辑和同步逻辑剥离开,分别在不同的模块中实现

A主要是为了避免亚稳态;B无法避免;

转载存疑

8.Moore状态机和Mealy状态机的差异在(C)是否相关。

A.状态和输入信号

B.输出信号和状态

C.输出信号和输入信号

D.状态和输出信号

Moore型的输出只与当前状态有关

Mealy型的输出还与输入相关

9.计算机执行程序时,在(A)的控制下,逐条从内存中取出指令、分析指令、执行指令。

A.控制器

B.运算器

C.存储器

D.I/o设备

10.相互间相位固定且频率相同的时钟就是同步时钟(A)

A.正确

B.错误

时钟频率是整倍数,并且相互之间的相位是固定而且相差可预知的,才可以称得上是同步时钟。

11.下面的verilog代码:

timescale1ns/100ps

initial

clk=1'b0

always#100clk<= ~clk;

产生的时钟频率是:(A)

A.5MHz

B.10 MHz

C.100MHz

D.50MHz

1/200ns =5MHz

12.如果该class会被继承,则该class所有定义的function/task都需要加virtual(B)

A.正确

B.错误

若class会被继承,建议在所有的函数/任务中都加上virtual,方便之后拓展;new函数以及randmize等除外;

13.bit、logic、reg都是4态数据类型(B)

A.正确

B.错误

bit是2值逻辑

14.关于亚稳态,以下说法错误的是(B)

A.亚稳态出现的概率与器件工艺,时钟频率等有关系

B.亚稳态打两拍就可以消除

C.数字系统中,信号无法满足setup和Hold时容易出现亚稳态

D.当一个触发器进入亚稳态,既无法准确预测寄存器的输出电平,也很难预测何时输出才能稳定在某个正确的电平上

15.对于相同位数输入的变量比较器,大于和小于的面积是一样的 (B)

A.对

B.错误

无符号数面积相同,有符号数面积不同。(转载存疑)

16.以下说法关于低功耗的说法不正确的是:(D)

A.采用合理的powergating方案可以降低功耗。

B.clockgating可以降低芯片功耗

C.通过降低数据的翻转率可以降低功耗。

D.无论设计大小,一律采用先进工艺。

17.在System Verilog中,调用$write可以自动地在输出后进行换行。(B)

A.正确

B.错误

$display自动换行

18.有如下代码

class C1;

randint m;

constraintc1_ cons { m<=10;}

endclass

class C2 extends C1;

constraintc1_cons { m>=10;}

endclass

以代码最终实现的约束效果是(A)

A.m>=10

B.m<=10

C.m=10

D.解约束失败

要求满足所有的约束;子类会继承父类的约束,但对于与父类同名的约束,会进行覆盖;

19.CPU流水线级数越多,CPU每周期处理的指令数就越多(B)。

A.正确

B.错误

单周期CPU正确,多周期CPU每周期的指令数和很多因素有关

20.下列哪项不属于动态功耗? (C)

A.电路短路功耗

B.电路翻转功耗

C.二极管反向电流引起的功耗。

21.数字电路中用“1”和“0”分别表示两种状态,二者无大小之分(A)

A.正确

B.错误

22.芯片的某条时序路径的保持时间不满足,可通过降低工作频率来满足保持时间(B)。

A.正确

B.错误

当保持时间不满足时

- 理论上,可以增加Tffpd和Tcomb来解决,也就是增加触发器的D端到Q端的延时,以及两级触发器之间的组合逻辑电路部分。

- 目前大部分芯片的Thold时间都可以做到0ns。所以当保持时间不满足时,通常采用的做法是在传输路径上插入buffer,在不影响逻辑功能前提下,只具有增加延迟的作用。

PS:保持时间Thold和时钟频率之间是没有关系,故降低时钟速度不能解决保持时间不满足的问题,很多面试题喜欢在这里挖坑。

23.异步处理电路中,两级触发器同步方法可以确保第二级寄存器的输出不出现亚稳态。(B)

A.正确

B.错误

24.一个十进制数-3,定点位宽为4bit,在Verilog语言中分别用2进制补码表示为(B)

A.4'b1100

B.4'b1101

C.4'b1011

D.4'b0011

按位取反再加1

25.systemverilog中类默认的成员属性是(B)

A.private

B.public

C.automatic

D.local

另外两个分别是protected,local。需注意,public不是关键词。

26.格雷码的异步处理可以采用直接打拍的方式,在STA时不需要特殊检查(A)

A.正确

B.错误

STA只适用于同步电路

27.电路和波形如图,正确输出的波形是(B)

A.2

B.1

C.3

D.4

二分频电路

28.某包处理器的工作时钟为125MHz,在正常工作时,它可以每32个时钟周期处理个64字节的以太包。则该包处理器的处理性能是(A) .

A.2G bps

B.4G bps

C.1G bps

D.250M bps

(64*8/32)/(1/125M)=2000M bps=2G bps(个人理解)

29.在同步电路设计中,逻辑电路的时序模型如下:

T1为触发器的时钟端到数据输出端的延时,T2和T4为连线延时,T3为组合逻辑延时,T5为时钟网络延时:

假设时钟clk的周期为Tcycle;

假设Tsetup. Thold分别为触发器的setup time, hold time.

那么,为了保证数据正确采样(该路径为multi-cycle路径),下面哪个等式必须正确:(D)

A.T1+T2+T3+T4<Tcycle-Tsetup +T5,T1+T2+T3+T4>Thold

B.T1+T2+T3+T4+T5<Tcycle-Tsetup,T1+T2+T3+T4>Thold

C.T1+T2+T3+T4<Tcycle-Tsetup,T1+T2+T3+T4+T5>Thold

D.T1+T2+T3+T4<Tcycle-Tsetup+T5,T1+T2+T3+T4>Thold+T5

建立时间和保持时间

30.为什么数字电路系统中只使用二进制?(C)

A.自然界的本质决定

B.比十进制更简单

C.晶体管的特性决定

D.其他都正确

多选

1.电路设计中需要关注PPA,分别指(ABC)

A.功耗

B.性能

C.面积

D.成本

power,performance,area

2.下述关于覆盖率收集结果的描述正确的是(AD)

A.代码覆盖率高、功能覆盖率低,需要加强功能点的覆盖

B.代码覆盖率低、功能覆盖率高,往往是一个危险信号,说明功能覆盖率建模还不完善

C.功能覆盖率达到100时,代码覆盖率一定已经全部覆盖

D.代码覆盖率高,功能覆盖率高,往往标志验证正处于收敛状态,需要加强各边界点和异常点的测试

B选项也可能是代码冗余,此处存疑

(1)功能覆盖率高但是代码覆盖率低

分析未覆盖到的代码,推断仿真是否有遗漏的功能点,代码是否为冗余或不可达代码;

(2)功能覆盖率低但是代码覆盖率高

仿真用例没有关注到一些功能点,需要修改测试用例。

3.在设计中,可以被用于进行不同时钟域隔离的memory类型为(AD)

A.two-port Register File

B.single-port Register File

C.single-port RAM

D.dual-port RAM

4.芯片的工作条件主要是指(BCD)

A.工艺

B.电压

C.温度

D.湿度

对延时影响的因素——PVT指的是工艺、电压和温度

5.以下哪几种因素会影响芯片的静态功耗(ACE)

A.工作电压

B.负载电容

C.工作温度

D.翻转活动因子

E.工艺

这个https://blog.csdn.net/mu_guang_/article/details/115719673

6.下面哪些语句是不可综合的(CDE)

A.generate

B.always

C.time

D.initial

E.delays

7.在IC设计中,复位设计面临的主要问题包括(ABD)

A.时钟域的同步

B.去毛刺

C.可否做STA检查

D.对时钟的依赖程度

异步复位无法做STA检查

8.下面关于always语句的使用描述正确的是(ABC)

A.在组合always模块中使用阻塞赋值语句

B.在时序always模块中使用非阻塞赋值语句

C.避免在组合always模块中敏感信号列表中缺少信号

D.避免敏感信号列表中出现冗余信号

组合逻辑是描述输入和输出关系的功能块,由于延时的原因,输出可能会有毛刺,为避免避免毛刺需要引入冗余逻辑。

9.125MHz时钟域的多bit信号A[127:0]需要同步到25MHz时钟域,可能使用的同步方式有(ABD)

A.双向握手

B.DMUX

C.打三拍

D.异步FIFO

快到慢,多bit

10.某个时钟域的建立时间要求是3ns,保持时间要求是3ns,那么如下几个寄存器,存在时序收敛问题的是:ACD

A.数据在一个时钟周期内的连续稳定时间为6ns,且数据在触发器时钟有效沿前,保持稳定不变的时间为4ns,

B.数据在一个时钟周期内的连续稳定时间为8ns,且数据在触发器时钟有效沿前,保持稳定不变的时间为4ns,

C.数据在一个时钟周期内的连续稳定时间为8ns,且数据在触发器时钟有效治前,保持稳定不变的时间为2ns,

D.数据在一个时钟周期内的连续稳定时间为6ns,且数据在触发器时钟有效沿前,保持稳定不变的时间的2ns,

setup hold ACD均不满足时序要求

A 4 2

B 4 4

C 2 6

D 2 4